Адаптивний цифровий фазовий дискримінатор

Номер патенту: 113473

Опубліковано: 25.01.2017

Автори: Коваль Валерій Вікторович, Кальян Дмитро Олександрович, Коваль Віктор Валерійович

Формула / Реферат

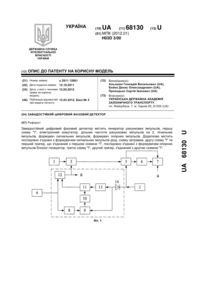

Адаптивний цифровий фазовий дискримінатор, що містить послідовно з'єднані формувач першої вхідної імпульсної послідовності, вхід якого є першим входом пристрою, лічильник імпульсів, K-виходів якого з'єднані з відповідними K-входами статичного регістра, при цьому вихід формувача першої вхідної імпульсної послідовності підключений також до першого входу блока прив'язки імпульсів вхідної імпульсної послідовності, другий вхід якого з'єднаний з k-м виходом додаткового лічильника, рахунковий вхід якого з'єднаний з виходом формувача другої вхідної послідовності, вхід якого є другим входом пристрою, причому вихід блока прив'язки імпульсів вхідної імпульсної послідовності з'єднаний з входом запису статичного регістра, K-виходів якого з'єднані з відповідними K-входами додаткового статичного регістра, K-виходів якого є цифровими виходами пристрою, причому вхід читання додаткового статичного регістра з'єднаний з виходом блока прив'язки імпульсів зчитування, перший вхід якого також з'єднаний з виходом блока прив'язки імпульсів вхідної імпульсної послідовності, а другий вхід блока прив'язки імпульсів зчитування з'єднаний з виходом формувача вхідної імпульсної послідовності зчитування, вхід якого є входом асинхронного читання, який відрізняється тим що введені K-входи попередньої установки лічильника імпульсів, що є Κ цифровими входами попередньої установки коду (адаптивного керування) пристрою та вхід дозволу попереднього запису лічильника імпульсів, що з'єднаний з виходом блока прив'язки імпульсів дозволу попереднього запису, перший вхід якого з'єднаний з виходом інвертора, вхід якого також з'єднаний з виходом формувача першої вхідної імпульсної послідовності, причому другий вхід блока прив'язки імпульсів дозволу попереднього запису з'єднаний з виходом блока прив'язки імпульсів узгодження, перший вхід якого також з'єднаний з k-м виходом додаткового лічильника, а другий вхід блока прив'язки імпульсів узгодження з'єднаний з виходом формувача вхідної імпульсної послідовності дозволу попереднього запису, вхід якого є входом дозволу попереднього запису пристрою.

Текст

Реферат: Винахід належить до галузі телекомунікації, метрології, енергетики та може застосовуватись в автоматиці, комп'ютерних, інформаційних технологіях для порівняння фаз двох взаємно незалежних коливань з метою вимірювання кута зсуву фази між ними і представлення результату в цифровому вигляді. Адаптивний цифровий фазовий дискримінатор додатково містить введені K-входи попередньої установки лічильника імпульсів, що є Κ цифровими входами попередньої установки коду (адаптивного керування) пристрою та вхід дозволу попереднього запису лічильника імпульсів, що з'єднаний з виходом блока прив'язки імпульсів дозволу попереднього запису, перший вхід якого з'єднаний з виходом інвертора, вхід якого також з'єднаний з виходом формувача першої вхідної імпульсної послідовності, причому другий вхід блока прив'язки імпульсів дозволу попереднього запису з'єднаний з виходом блока прив'язки імпульсів узгодження, перший вхід якого також з'єднаний з k-м виходом додаткового лічильника, а другий вхід блока прив'язки імпульсів узгодження з'єднаний з виходом формувача вхідної імпульсної послідовності дозволу попереднього запису, вхід якого є входом дозволу попереднього запису пристрою, за рахунок чого досягається забезпечення адаптивного керованого формування кодової комбінації про величину кута зсуву фази двох взаємно незалежних періодичних імпульсних послідовностей та підвищення достовірності представлення результатів вимірювань в цифровому вигляді. UA 113473 C2 (12) UA 113473 C2 UA 113473 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до галузі телекомунікацій, метрології, енергетики та може застосовуватись в автоматиці, комп'ютерних, інформаційних технологіях для порівняння фаз двох взаємно незалежних коливань з метою вимірювання кута зсуву фази між ними і представлення результату в цифровому вигляді. Відомий аналог (А.с. СССР №1095349, опубл. 19.08.1982 p.) фазовий дискримінатор, що містить формувач опорного і вхідного сигналів, а також послідовно з'єднані двійковий лічильник, статичний регістр та перетворювач код-напруга, при цьому вихід формувача опорного сигналу підключений до входу двійкового лічильника і першого входу блока прив'язки імпульсів вхідного сигналу, другий вхід якого з'єднаний з виходом формувача вхідного сигналу, а вихід блока прив'язки з'єднаний з входом керування статичного регістра. Недоліком аналога є відсутність керування станом двійкового лічильника. Найближчий аналог (Патент № 3081, опубл. 15.10.2004 р., бюл. № 10, Цифровий часовий дискримінатор), що містить послідовно з'єднані формувач першої вхідної імпульсної послідовності, вхід якого є першим входом пристрою, формувач другої вхідної послідовності, лічильник імпульсів і статичний регістр, блок прив'язки імпульсів вхідної імпульсної послідовності, додатковий лічильник, при цьому вихід формувача першої вхідної імпульсної послідовності підключений також до першого входу блока прив'язки імпульсів вхідної імпульсної послідовності, другий вхід якого з'єднаний з К-м виходом додаткового лічильника, рахунковий вхід якого з'єднаний з виходом формувача другої вхідної послідовності, вхід якого є другим входом пристрою, причому вихід блока прив'язки імпульсів вхідної імпульсної послідовності з'єднаний із входом запису статичного регістра, а в згадуваний дискримінатор уведені додатковий статичний регістр, блок прив'язки імпульсів зчитування, формувач вхідної імпульсної послідовності, при цьому Κ-виходи додаткового статичного регістра є цифровими виходами пристрою, а Κ-входи з'єднані з відповідними К-виходами статичного регістра, причому вхід читання додаткового статичного регістра з'єднаний з виходом блока прив'язки імпульсів зчитування, перший вхід якого з'єднаний з виходом блока прив'язки імпульсів вхідної імпульсної послідовності і також із входом запису статичного регістра, а другий вхід блока прив'язки імпульсів зчитування з'єднаний з виходом формувача вхідної імпульсної послідовності зчитування, вхід якого є входом асинхронного читання. Недоліком найближчого аналога є відсутність керування станом лічильника імпульсів, відносно стану додаткового лічильника імпульсів, на початок періоду вимірювання, що не забезпечує формування достовірної кодової комбінації про величину кута зсуву фази двох взаємно незалежних періодичних імпульсних послідовностей, а, отже, можливості виникнення помилок. Винаходом поставлена задача забезпечити адаптивне кероване формування кодової комбінації про величину кута зсуву фази двох взаємно незалежних періодичних імпульсних послідовностей та підвищення достовірності представлення результатів вимірювань в цифровому виді шляхом зміни конструкції. Поставлена винаходом задача вирішується тим, що адаптивний цифровий фазовий дискримінатор, що містить послідовно з'єднані формувач першої вхідної імпульсної послідовності, вхід якого є першим входом пристрою, лічильник імпульсів, K-виходів якого з'єднані з відповідними Κ-входами статичного регістра, при цьому вихід формувача першої вхідної імпульсної послідовності підключений також до першого входу блока прив'язки імпульсів вхідної імпульсної послідовності, другий вхід якого з'єднаний з k-м виходом додаткового лічильника, рахунковий вхід якого з'єднаний з виходом формувача другої вхідної послідовності, вхід якого є другим входом пристрою, причому вихід блока прив'язки імпульсів вхідної імпульсної послідовності з'єднаний з входом запису статичного регістра, K-виходів якого з'єднані з відповідними K-входами додаткового статичного регістра, K-виходів якого є цифровими виходами пристрою, причому вхід читання додаткового статичного регістра з'єднаний з виходом блока прив'язки імпульсів зчитування, перший вхід якого також з'єднаний з виходом блока прив'язки імпульсів вхідної імпульсної послідовності, а другий вхід блока прив'язки імпульсів зчитування з'єднаний з виходом формувача вхідної імпульсної послідовності зчитування, вхід якого є входом асинхронного читання, згідно з пропонованим рішенням забезпечення адаптивного керованого формування кодової комбінації про величину кута зсуву фази двох взаємно незалежних періодичних імпульсних послідовностей та підвищення достовірності представлення результатів вимірювань в цифровому вигляді, введені K-входи попередньої установки лічильника імпульсів, що є Κ цифровими входами попередньої установки коду (адаптивного керування) пристрою та вхід дозволу попереднього запису лічильника імпульсів, що з'єднаний з виходом блока прив'язки імпульсів дозволу попереднього запису, перший вхід якого з'єднаний з виходом інвертора, вхід якого також з'єднаний з виходом 1 UA 113473 C2 5 10 15 20 25 30 35 40 45 50 55 60 формувача першої вхідної імпульсної послідовності, причому другий вхід блока прив'язки імпульсів дозволу попереднього запису з'єднаний з виходом блока прив'язки імпульсів узгодження, перший вхід якого також з'єднаний з k-м виходом додаткового лічильника, а другий вхід блока прив'язки імпульсів узгодження з'єднаний з виходом формувача вхідної імпульсної послідовності дозволу попереднього запису, вхід якого є входом дозволу попереднього запису пристрою. На схемі 1 приведена електрична схема пропонованого пристрою; на схемі 2 - схемна реалізація блока прив'язки імпульсів, блока прив'язки імпульсів зчитування, блока прив'язки імпульсів дозволу попереднього запису і блока прив'язки імпульсів узгодження; на схемі 3 часові діаграми, що пояснюють роботу. Адаптивний цифровий фазовий дискримінатор, містить формувач 1 першої вхідної імпульсної послідовності, формувач 2 другої вхідної імпульсної послідовності, блок 3 прив'язки імпульсів вхідної імпульсної послідовності, лічильник 4 імпульсів, статичний 5 регістр, додатковий 6 лічильник, додатковий 7 статичний регістр, блок 8 прив'язки імпульсів зчитування, формувач 9 вхідної імпульсної послідовності зчитування, K-входи попередньої установки лічильника 4 імпульсів (нумеровані 1…k), що є Κ цифровими входами попередньої установки коду (адаптивного керування) пристрою та вхід дозволу попереднього запису лічильника 4 імпульсів, блок 10 прив'язки імпульсів дозволу попереднього запису, інвертор 11, блок 12 прив'язки імпульсів узгодження, формувач 13 вхідної імпульсної послідовності дозволу попереднього запису, що є входом дозволу попереднього запису пристрою. Пристрій працює таким чином. Сформована формувачем 1 перша вхідна імпульсна послідовність (схема 3, а) надходить на рахунковий вхід лічильника 4 імпульсів. Код числа, що зберігається у лічильнику 4 імпульсів, зростає на одиницю при подачі на вхід імпульсу першої вхідної імпульсної послідовності. Кодова комбінація, що буде формуватися на його виходах (схема 3, б … схема 3, д), відповідає кількості підрахованих вхідних імпульсів від свого початкового стану. На введені додаткові Kвходи (нумеровані 1…k), які є Κ цифровими входами попередньої установки коду пристрою, подають код (схема 3, н … схема 3, п), що відповідає необхідному значенню початкового стану адаптивного цифрового фазового дискримінатора. Отримана можливість зміни початкового стану пристрою дозволяє забезпечити адаптивне кероване формування кодової комбінації про величину кута зсуву фази двох взаємно незалежних періодичних імпульсних послідовностей. Сформований формувачем 13 вхідної імпульсної послідовності дозволу попереднього запису імпульс надходить на другий вхід блоку прив'язки імпульсів узгодження 12 і формує, у момент часу, коли за зазначеним фронтом наступає фронт імпульсу з виходу k-го розряду лічильника імпульсів 6, на виході фронт сигналу. Фронт сигналу з виходу блока прив'язки імпульсів узгодження 12, надходячи на другий вхід блока 10 прив'язки імпульсів дозволу попереднього запису формує, у момент часу, коли за зазначеним фронтом наступає фронт імпульсу з виходу інвертора 11, імпульс дозволу попереднього запису (схема 3, м). Фронтом імпульсу дозволу попереднього запису здійснюється попередня установка початкового стану лічильника 4 імпульсів (схема 3, б… схема 3, г). Повний цикл роботи лічильника 4 імпульсів визначається його періодом роботи θ1, який k зв'язаний з періодом T1 першої вхідної імпульсної послідовності співвідношенням θ1=Т1б•2 , після якого він повертається у початковий стан. Сформована формувачем 2 друга вхідна імпульсна послідовність надходить на рахунковий вхід лічильника імпульсів 6, на виході k-го розряду, якого через період θ2, що є періодом вимірювання, який зв'язаний з періодом Т2 другої вхідної імпульсної послідовності К співвідношенням θ2=Т2•2 , формується фронт сигналу, що надходить на другий вхід блока прив'язки імпульсів 3 і формує, у момент часу, коли за зазначеним фронтом наступає спад імпульсу першої вхідної імпульсної послідовності (при цьому робота лічильника 4 повинна здійснюватися фронтом зазначеного імпульсу), на виході блока прив'язки імпульсів 3, фронт сигналу який, надходячи на вхід запису регістра 5, здійснює запис, сформованої в даний момент на виходах лічильника 4 кодові комбінації, у статичний регістр 5. Записана кодова комбінація в статичний регістр 5 відповідає часовій неузгодженості між першою і другою вхідними імпульсними послідовностями і буде незмінною протягом тривалості інтервалу вимірювання, тобто до моменту появи наступного фронту сигнала з виходу блоку прив'язки імпульсів 3. Зчитування кодової комбінації може здійснюватися в будь-який момент часу імпульсами зчитування, які мають період менший періоду вимірювання θ, що надходять на вхід формувача 9 вхідної імпульсної послідовності зчитування. Сформований формувачем 9 вхідної імпульсної 2 UA 113473 C2 5 10 15 20 25 30 35 40 послідовності зчитування фронт імпульсу зчитування надходить на другий вхід блока 8 прив'язки імпульсів зчитування, на перший вхід якого надходить фронт сигналу з виходу блока 3 прив'язки імпульсів, що дозволяє зчитування. В результаті на виході блока прив'язки зчитування 8 формується фронт сигналу (схема 3, ж), який, надходячи на вхід запису додаткового 7 статичного регістра, записує кодову комбінацію статичного регістра 5 в додатковий 7 статичний регістр (схема 3, з… схема 3, к), що відповідає часовій неузгодженості між першою і другою вхідними імпульсними послідовностями. Технічне рішення винаходу забезпечує адаптивне кероване формування кодової комбінації про величину кута зсуву фази двох взаємно незалежних періодичних імпульсних послідовностей та підвищує достовірність представлення результатів вимірювань в цифровому вигляді. Керування пристроєм дозволяє його використовувати у сучасних інтелектуальних, адаптивних, оптимальних системах автоматики, пристроях вимірювання різниці фаз/часу періодичних сигналів. ФОРМУЛА ВИНАХОДУ Адаптивний цифровий фазовий дискримінатор, що містить послідовно з'єднані формувач першої вхідної імпульсної послідовності, вхід якого є першим входом пристрою, лічильник імпульсів, K-виходів якого з'єднані з відповідними K-входами статичного регістра, при цьому вихід формувача першої вхідної імпульсної послідовності підключений також до першого входу блока прив'язки імпульсів вхідної імпульсної послідовності, другий вхід якого з'єднаний з k-м виходом додаткового лічильника, рахунковий вхід якого з'єднаний з виходом формувача другої вхідної послідовності, вхід якого є другим входом пристрою, причому вихід блока прив'язки імпульсів вхідної імпульсної послідовності з'єднаний з входом запису статичного регістра, Kвиходів якого з'єднані з відповідними K-входами додаткового статичного регістра, K-виходів якого є цифровими виходами пристрою, причому вхід читання додаткового статичного регістра з'єднаний з виходом блока прив'язки імпульсів зчитування, перший вхід якого також з'єднаний з виходом блока прив'язки імпульсів вхідної імпульсної послідовності, а другий вхід блока прив'язки імпульсів зчитування з'єднаний з виходом формувача вхідної імпульсної послідовності зчитування, вхід якого є входом асинхронного читання, який відрізняється тим, що введені Kвходи попередньої установки лічильника імпульсів, що є Κ цифровими входами попередньої установки коду (адаптивного керування) пристрою та вхід дозволу попереднього запису лічильника імпульсів, що з'єднаний з виходом блока прив'язки імпульсів дозволу попереднього запису, перший вхід якого з'єднаний з виходом інвертора, вхід якого також з'єднаний з виходом формувача першої вхідної імпульсної послідовності, причому другий вхід блока прив'язки імпульсів дозволу попереднього запису з'єднаний з виходом блока прив'язки імпульсів узгодження, перший вхід якого також з'єднаний з k-м виходом додаткового лічильника, а другий вхід блока прив'язки імпульсів узгодження з'єднаний з виходом формувача вхідної імпульсної послідовності дозволу попереднього запису, вхід якого є входом дозволу попереднього запису пристрою. 3 UA 113473 C2 Комп’ютерна верстка О. Рябко Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03D 3/04, H03D 13/00

Мітки: фазовий, цифровий, адаптивний, дискримінатор

Код посилання

<a href="https://ua.patents.su/6-113473-adaptivnijj-cifrovijj-fazovijj-diskriminator.html" target="_blank" rel="follow" title="База патентів України">Адаптивний цифровий фазовий дискримінатор</a>

Попередній патент: Спосіб виявлення життєздатних некультурабельних мікроорганізмів у воді

Наступний патент: Установка для виробництва гіпсокартону та спосіб виготовлення гіпсокартонного листа

Випадковий патент: В'яжуче