Цифровий прецизійний часовий дискримінатор

Номер патенту: 84575

Опубліковано: 25.10.2013

Автори: Костік Богдан Ярославович, Лисенко Віталій Пилипович, Коваль Валерій Вікторович, Казакова Надія Феліксівна

Формула / Реферат

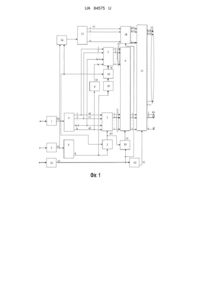

Цифровий прецизійний часовий дискримінатор, що містить перший формувач першої вхідної імпульсної послідовності, вхід якого є першим входом пристрою, а вихід якого також з'єднаний з першим входом блока прив'язки імпульсів вхідної імпульсної послідовності та з рахунковим входом першого лічильника імпульсів, k-виходів якого також з'єднані з відповідними k-входами статичного регістра, причому k-1 виходів першого лічильника імпульсів також з'єднані з відповідними к-1 входами першого додаткового статичного регістра, а k-й вихід першого лічильника імпульсів також з'єднаний із входом першого інвертора, вихід якого підключений до k-го входу першого додаткового статичного регістра, k-виходів якого підключені до відповідних перших k-входів комутатора, другі k-входи якого з'єднані з відповідними k-виходами статичного регістра, вхід запису якого також з'єднаний з виходом блока прив'язки імпульсів вхідної імпульсної послідовності та з D-входом D-тригера, вихід якого з'єднаний із входом керування комутатора, k-виходів якого з'єднані з відповідними к-входами другого додаткового статичного регістра, k-виходів якого є цифровими виходами пристрою, а вхід запису другого додаткового статичного регістра з'єднаний з виходом другого інвертора, вхід якого з'єднаний з рахунковим входом D-тригера та з виходом формувача імпульсів зчитування, вхід якого є входом асинхронного зчитування пристрою, причому вхід зчитування першого додаткового статичного регістра з'єднаний з виходом додаткового блока прив'язки імпульсів, перший вхід якого також з'єднаний з виходом формувача першої вхідної імпульсної послідовності, а другий вхід додаткового блока прив'язки імпульсів з'єднаний з виходом третього інвертора, вхід якого також з'єднаний з другим входом блока прив'язки імпульсів вхідної імпульсної послідовності та з k-м виходом другого лічильника, рахунковий вхід якого з'єднаний з виходом другого формувача другої вхідної імпульсної послідовності, вхід якого є другим входом пристрою, який відрізняється тим що додані третій додатковий статичний регістр, n-виходів якого з'єднані з відповідними додатковими n-входами другого додаткового статичного регістра, основні k-виходи якого разом з додатковими n-виходами є цифровими (k+n)-виходами пристрою, а n-входи третього додаткового статичного регістра з'єднані з відповідними n-виходами аналогово-цифрового перетворювача, вхід якого з'єднаний з виходом фазового дискримінатора, перший вхід якого з'єднаний з виходом першого формувача першої вхідної імпульсної послідовності, а другий вхід фазового дискримінатора з'єднаний з виходом другого формувача другої вхідної імпульсної послідовності, причому вхід зчитування третього додаткового статичного регістра також з'єднаний з виходом формувача імпульсів зчитування.

Текст

Реферат: Цифровий прецизійний часовий дискримінатор містить третій додатковий статичний регістр, nвиходів якого з'єднані з відповідними додатковими n-входами другого додаткового статичного регістра, основні k-виходи якого разом з додатковими n-виходами є цифровими (k+n)-виходами пристрою. А n-входи третього додаткового статичного регістра з'єднані з відповідними nвиходами аналогово-цифрового перетворювача, вхід якого з'єднаний з виходом фазового дискримінатора, перший вхід якого з'єднаний з виходом першого формувача першої вхідної імпульсної послідовності, а другий вхід фазового дискримінатора з'єднаний з виходом другого формувача другої вхідної імпульсної послідовності. Вхід зчитування третього додаткового статичного регістра також з'єднаний з виходом формувача імпульсів зчитування. UA 84575 U (54) ЦИФРОВИЙ ПРЕЦИЗІЙНИЙ ЧАСОВИЙ ДИСКРИМІНАТОР UA 84575 U UA 84575 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до галузі радіотехнічних, телекомунікаційних, інформаційних пристроїв і може використовуватися для виміру часової неузгодженості двох взаємно незалежних імпульсних послідовностей у цифрових вимірювальних системах, системах синхронізації, автопідстроювання фази та частоти. Найбільш близьким аналогом по технічній суті (патент №3887, МПК Н03D 3/04, опубл. Бюл. №12 від 15.12.04 асинхронний цифровий часовий дискримінатор), що містить перший формувач першої вхідної імпульсної послідовності, вхід якого є першим входом пристрою, а вихід якого також з'єднаний з першим входом блока прив'язки імпульсів вхідної імпульсної послідовності та з рахунковим входом першого лічильника імпульсів, k-виходів якого також з'єднані з відповідними к-входами статичного регістра, причому, k-1 виходів першого лічильника імпульсів також з'єднані з відповідними k-1 входами першого додаткового статичного регістра, а k-й вихід першого лічильника імпульсів також з'єднаний із входом першого інвертора, вихід якого підключений до k-го входу першого додаткового статичного регістра, k-виходів якого підключені до відповідних перших k-входів комутатора, другі k-входи якого з'єднані з відповідними kвиходами статичного регістра, вхід запису якого також з'єднаний з виходом блока прив'язки імпульсів вхідної імпульсної послідовності та з D-входом D-тригера, вихід якого з'єднаний із входом керування комутатора, k-виходів якого з'єднані з відповідними k-входами другого додаткового статичного регістра, k-виходів якого є цифровими виходами пристрою, а вхід запису другого додаткового статичного регістра з'єднаний з виходом другого інвертора, вхід якого також з'єднаний з рахунковим входом D-тригера та з виходом формувача імпульсів зчитування, вхід якого є входом асинхронного зчитування пристрою, причому вхід зчитування першого додаткового статичного регістра з'єднаний з виходом додаткового блока прив'язки імпульсів, перший вхід якого також з'єднаний з виходом формувача першої вхідної імпульсної послідовності, а другий вхід додаткового блока прив'язки імпульсів з'єднаний з виходом третього інвертора, вхід якого також з'єднаний з другим входом блока прив'язки імпульсів вхідної імпульсної послідовності та з k-м виходом другого лічильника, рахунковий вхід якого з'єднаний з виходом другого формувача другої вхідної імпульсної послідовності, вхід якого є другим входом пристрою. Недоліком зазначеного пристрою є недостатня точність, яка обмежена тривалістю тактового інтервалу Т вхідних імпульсних послідовностей, між якими вимірюється часова неузгодженість. В основу корисної моделі поставлена задача шляхом зміни конструкції підвищити точність вимірювання часової неузгодженості між першою і другою вхідними імпульсними послідовностями. Поставлена задача вирішується тим, що введення у цифровий прецизійний часовий дискримінатор, що містить перший формувач першої вхідної імпульсної послідовності, вхід якого є першим входом пристрою, а вихід якого також з'єднаний з першим входом блока прив'язки імпульсів вхідної імпульсної послідовності та з рахунковим входом першого лічильника імпульсів, k-виходів якого також з'єднані з відповідними k- входами статичного регістра, причому k-1 виходів першого лічильника імпульсів також з'єднані з відповідними k-1 входами першого додаткового статичного регістра, а k-й вихід першого лічильника імпульсів також з'єднаний із входом першого інвертора, вихід якого підключений до k-го входу першого додаткового статичного регістра, k-виходів якого підключені до відповідних перших k-входів комутатора, другі k-входи якого з'єднані з відповідними k-виходами статичного регістра, вхід запису якого також з'єднаний з виходом блока прив'язки імпульсів вхідної імпульсної послідовності та з D-входом D-тригера, вихід якого з'єднаний із входом керування комутатора, k-виходів якого з'єднані з відповідними k-входами другого додаткового статичного регістра, вхід запису якого з'єднаний з виходом другого інвертора, вхід якого також з'єднаний з рахунковим входом D-тригера та з виходом формувача імпульсів зчитування, вхід якого є входом асинхронного зчитування пристрою, причому, вхід зчитування першого додаткового статичного регістра з'єднаний з виходом додаткового блока прив'язки імпульсів, перший вхід якого також з'єднаний з виходом формувача першої вхідної імпульсної послідовності, а другий вхід додаткового блока прив'язки імпульсів з'єднаний з виходом третього інвертора, вхід якого також з'єднаний з другим входом блока прив'язки імпульсів вхідної імпульсної послідовності та з k-м виходом другого лічильника, рахунковий вхід якого з'єднаний з виходом другого формувача другої вхідної імпульсної послідовності, вхід якого є другим входом пристрою, введені додаткові n-виходи (нумеровані k+1…k+n) другого додаткового статичного регістра, які разом з основними k-виходами другого додаткового статичного регістра є k+n цифровими виходами пристрою, причому додаткові n-входи (нумеровані k+1…k+n) додаткового статичного регістра підключені до відповідних n-виходів третього додаткового статичного регістра, вхід запису якого також з'єднаний з виходом формувача імпульсів зчитування, а n-входи третього додаткового 1 UA 84575 U 5 10 15 20 25 30 35 40 45 50 55 60 статичного регістра з'єднані з відповідними n-виходами аналогово-цифрового перетворювача, вхід якого підключений до виходу фазового дискримінатора, перший вхід якого також з'єднаний з виходом першого формувача першої вхідної імпульсної послідовності, а другий вхід фазового дискримінатора також з'єднаний з виходом другого формувача другої вхідної імпульсної послідовності. Суть корисної моделі пояснює креслення. На Фіг.1 приведена схема пропонованого пристрою; на Фіг. 2-часові діаграми, що пояснюють роботу. Цифровий прецизійний часовий дискримінатор містить: формувачі першої 1 і другої 2 вхідної імпульсної послідовності, блок прив'язки імпульсів 3, перший лічильник імпульсів 4, статичний регістр 5 і другий лічильник імпульсів 6, перший додатковий статичний регістр 7, перший інвертор 8; комутатор 9; D- тригер 10; другий додатковий статичний регістр 11; другий інвертор 12; формувач імпульсів зчитування 13; додатковий блок прив'язки імпульсів 14; третій інвертор 15 аналогічні відповідно формувачам першої і другої вхідної імпульсної послідовності, блока прив'язки імпульсів, першому лічильнику імпульсів, статичному регістру, другому лічильнику імпульсів, першому додатковому статичному регістру, першому інвертору; комутатору; D-тригеру; другому додатковому статичному регістру; другому інвертору; формувачу імпульсів зчитування; додатковому блоку прив'язки імпульсів; третьому інвертору пристрою прототипу, фазовий дискримінатор 16, аналогово-цифровий перетворювач 17, третій додатковий статичний регістр 18, другий додатковий статичний регістр 11 з додатковими nвиходами і n-входами. Пропонований пристрій працює у такий спосіб. Сформована формувачем 1 перша вхідна імпульсна послідовність (схема 2а) надходить на рахунковий вхід лічильника імпульсів 4, на виходах якого буде формуватися кодова комбінація (схема 2в … схема 2д), що відповідає кількості вхідних імпульсів, що надійшли, від свого початкового стану (як стан може бути обраний такий стан лічильника імпульсів, при якому на виходах його всіх розрядів встановлено сигнал логічного нуля). Сформована формувачем 2 друга вхідна імпульсна послідовність надходить на рахунковий вхід лічильника імпульсів 6, на виході k-го розряду, якого через період θ, що є періодом вимірювання і зв'язаний з періодом Т вхідної імпульсної послідовності співвідношенням Θ = К Т2 , формується фронт сигналу, що надходить на другий вхід блока прив'язки імпульсів 3 і формує, у момент часу, коли за зазначеним фронтом наступає спад імпульсу першої вхідної імпульсної послідовності (при цьому робота лічильника 4 повинна здійснюватися фронтом зазначеного імпульсу), на виході блока прив'язки імпульсів 3 (схема 2ж), фронт сигналу який, надходячи на вхід запису регістра 5, здійснює запис, сформованої в даний момент на виходах лічильника 4 кодові комбінації, у статичний регістр 5 (СР). Записана кодова комбінація в статичний регістр 5 (виділена еліпсом на схемах 2в, 2г, 2д) відповідає часовій неузгодженості між першою і другою вхідними імпульсними послідовностями і буде незмінною (постійною const) протягом тривалості інтервалу вимірювання рівній періоду, тобто до моменту появи наступного фронту сигналу з виходу блока прив'язки імпульсів 3 (схема 2і). Вихідний сигнал k-го розряду лічильника імпульсів 6 інвертується інвертором 15, що забезпечує формування фронту сигналу в середині періоду вимірювання θ, і надходить на другий вхід додаткового блока прив'язки імпульсів 14 і формує в момент часу, коли за зазначеним фронтом наступає спад імпульсу першої вхідної імпульсної послідовності (при цьому робота лічильника 4 здійснюється фронтом зазначеного імпульсу), на виході додаткового блока прив'язки імпульсів 14 (схема 2з), фронт сигналу який, надходячи на вхід запису першого додаткового статичного регістра 7, здійснює запис інвертованого першим інвертором 8 сигналу з k-го виходу першого лічильники 4 (схема 2е), а також сформованої в даний момент на k-1 виходах першого лічильники 4 кодової комбінації в регістр 7. Записана кодова комбінація в додатковому статичному регістрі 7 (виділена еліпсом на схемах 2в, 2г, 2е) відповідає часовій неузгодженості між першою і другою вхідними імпульсними послідовностями і буде незмінною (постійною - const) протягом тривалості комплементарного інтервалу вимірювання рівній , тобто до моменту появи наступного фронту сигналу з виходу додаткового блока прив'язки імпульсів 14 (схема 2к). Комплементарний інтервал вимірювання 0 зміщений за часом на величину θ/2 щодо інтервалу вимірювання θ (схема 2і та схема 2к), що при незмінних значеннях кодових комбінацій на даних інтервалах дозволяє забезпечити асинхронне зчитування цифрової інформації імпульсами зчитування тривалістю σ

ДивитисяДодаткова інформація

Автори англійськоюLysenko Vitalii Pylypovych, Kazakova Nadiia Feliksivna

Автори російськоюЛысенко Виталий Филиппович, Казакова Надежда Феликсовна

МПК / Мітки

МПК: H03D 13/00

Мітки: прецизійний, дискримінатор, часовий, цифровий

Код посилання

<a href="https://ua.patents.su/7-84575-cifrovijj-precizijjnijj-chasovijj-diskriminator.html" target="_blank" rel="follow" title="База патентів України">Цифровий прецизійний часовий дискримінатор</a>

Попередній патент: Спосіб визначення здатності lactobacillus до продукції перекису водню з використанням еритроцитів крові

Наступний патент: Пакетик з нетканого матеріалу з сумішшю приправ

Випадковий патент: Спосіб визначення ендотоксикозу