Схема керування для енергонезалежного напівпровідникового запам’ятовуючого пристрою

Формула / Реферат

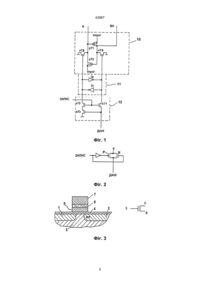

1. Схема управління для енергонезалежносо напівпровідникового запам'ятовуючого пристрою (ЗП). яка містить схему (10) перетворення рівнів, що подає вихідне значення (В) і комплементарне до нього вихідне значення (ВН) на розрядну шину та/або шину слів напівпровідникового ЗП, причому між схемою (12) введення даних і схемою (10) перетворення рівнів вона містить схему-защіпку (11) для проміжного запам'ятовування даних, що підлягають запису у напівпровідниковий ЗП, яка відрізняється тим, що схема (12) введення даних складається із першого nМОН-транзистора, ввімкненого своїм каналом витік-стік між входом даних (ДАНІ) і першим виходом даних, і ввімкнених між масою і другим виходом даних, послідовно з'єднаних між собою другого і третього nМОН-транзисторів (nТ2, nТЗ), причому затвор другого nМОН-транзистора (nТ2) з'єднаний із затвором першого nМОН-транзистора (nТ1), а затвор третього nМОН-транзистора (nТЗ) з'єднаний з витоком (стоком) першого nМОН-транзистора (nТ1).

2. Схема управління за п. 1, яка відрізняється тим, що схема-защіпка (11) складається із двох ввімкнених зустрічно-паралельно інверторів (11, 12).

Текст

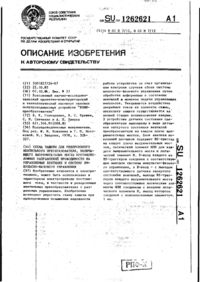

1. Схема управління для енергонезалежного напівпровідникового запам'ятовуючого пристрою (ЗП), яка містить схему (10) перетворення рівнів, що подає вихідне значення (В) і комплементарне C2 (54) СХЕМА КЕРУВАННЯ ДЛЯ ЕНЕРГОНЕЗАЛЕЖНОГО НАПІВПРОВІДНИКОВОГО ЗАПАМ'ЯТОВУЮЧОГО ПРИСТРОЮ 42887 ни 2 колектора напругу +15 В, що дає змогу електронам здійснювати тунельний перехід із плаваючого затвора 5 крізь тунельний оксидний шар 4 у зону 2 стоку. Але можна також для програмування до керуючого затвору 7 прикласти напругу -11 В, а до зони 2 стоку напругу +4 В. І в цьому випадку електрони будуть стимулюватися до здійснення тунельного переходу із плаваючого затвору 5 у зону 2 стоку. При програмуванні з використанням гарячих електронів до керуючого затвору 7 прикладають напругу +15 В, до зони 2 стоку напругу +5 В, а до зони 1 витоку напругу 10 В. Внаслідок цього електрони переміщуються із зони 2 стоку до зони 1 витоку і одночасно здійснюють тунельний перехід крізь тунельний оксидний шар 4 у плаваючий затвор 5. Як відомо, програмування і стирання даних у ЕСППЗП здійснюють байтами, тоді як швидкодійні ЗП програмують з використанням гарячих електронів чи тунельного ефекту Фоулера-Нордхайма байтами, а стирають з використанням тунельного ефекту Фоулера-Нордхайма блоками. На фіг. 4 зображено інший тип комірок пам'яті так звану комірку із розщепленим затвором, у якій на напівпровідниковій підкладці 3 виконано n+леговану зону 1 витоку, n+-леговану зону 2 стоку, тунельний оксидний шар 4, плаваючий затвор 5, проміжний шар 6 полідіелектрика і керуючий затвор 7. "Знижену" частину управляючого затвору 7 називають також послідовним затвором 8, оскільки розміщений вище керуючий затвор 7 і послідовний затвор 8 можуть розглядатися як з'єднані між собою затвори двох з'єднаних послідовно транзисторів структури n(Метал-Оксид-Напівпровідник) (nМОН = nMOS). Зображена на фіг. 3 комірка з багаторівневим затвором схематично відтворена наведеним у правій частині фігури символом, причому, літери мають такі значення: "З" = " керуючий затвор 7, "С" = вивід зони 2 стоку, "В" = вивід зони 1 витоку. Комірки пам'яті зображеного на фіг. 3 типу можуть бути використані для створення напівпровідникового ЗП з розрядними шинами РШ0, РШ1, РШ2, РШ3 і шинами слів ШС0, ШС1, ШС2 і ШС3, як схематично зображено на фіг. 5. У напівпровідниковому ЗП для стирання чи запису даних у окремі комірки пам'яті високі напруги мають бути селективно подані на вибрані шини слів чи розрядні шини. Поряд із напівпровідниковими ЗП високими напругами, наприклад, 15 В мають включатися також схеми формування спеціальних регульованих напруг, що мають стабільність, вищу, ніж напруга живлення. Важливим прикладом застосування є, наприклад, керування розрядними шинами швидкодійних ЗП з негативною напругою програмування (див. статтю R. Heinrich, W. Heinrigs, G. Tempel, J. WinnerI, T. Zettler, у журналі "Proc. Of the International Electron Device Meeting (IEDM)", 1993, с. 445448). Для досягнення стабільних умов програмування напругу розрядних шин встановлюють на рівні 5 В, а на шини слів подають напругу -12 В. Надалі під терміном "висока напруга" розуміються також і такі регульовані напруги, наприклад, 5 В, нижчі від напруги живлення 5,5 В. Для формування таких керуючих напруг необхідна спеціальна схема, яка має забезпечувати високу стабільність напруг і займати малу площу. Зокрема, у патенті США US-A-5,293,561 описана схема керування з розподільником напруг для роздільного живлення високими напругами поля пам'яті і ЗП для надлишкових установок. Ця відома схема керування містить, зокрема, перетворювач рівнів, який робить можливою подачу на напівпровідниковий ЗП вихідної напруги і комплементарної до неї вихідної напруги. Одначе, виявилось, що відома схема керування згідно з US-A-5,293,561 мало придатна для керуванням розрядними шинами, оскільки вона не дозволяє здійснювати проміжне запам'ятовування даних. Крім того, відома схема керування містить nМОН-транзистори збідненого типу, які вимагають значних технологічних витрат у вигляді додаткових конструктивних елементів. Схема керування згідно з європейським патентом ЕР 0154379 А2 містить велику кількість рМОНтранзисторів, які займають порівняно велику площу і мають меншу струмову навантажувальну здатність. Тому задача даного винаходу полягає у розробленні схеми керування для енергонезалежного напівпровідникового запам'ятовуючого пристрою, яка забезпечує формування високих керуючих напруг з високою стабільністю і може бути реалізована з використанням якомога меншої кількості елементів на малій площі, завдяки чому вона може бути розміщена у растрі матриці напівпровідникового ЗП. Для вирішення цієї задачі схема керування вказаного вище виду виконана з використанням відмітних ознак п. 1 формули винаходу. Схема введення даних може складатися із ввімкненого своїм каналом витік-стік між входом даних і першим виходом даних першого nМОНтранзистора і ввімкнених між масою і другим виходом даних послідовно з'єднаних між собою другого і третього nМОН-транзисторів, причому, затвор другого nМОН-транзистора з'єднаний із затвором першого nМОН-транзистора, а затвор третього nМОН-транзистора з'єднаний з витоком або стоком першого nМОН-транзистора. Слід чітко вказати на те, що така схема введення даних може використовуватися також окремо від схеми керування, коли необхідно простими засобами сформувати сигнал і інвертований відносно нього сигнал. Винайдену схему керування можна реалізувати з використанням невеликої кількості елементів на малій площі, завдяки чому вона може бути розміщена у растрі матриці напівпровідникового ЗП. Схема введення даних складається лише із трьох nМОН-транзисторів, завдяки чому вона може бути реалізована просто і на малій площі, що вкрай важливо для напівпровідникових ЗП або їх растрів. Оскільки тут не використовуються рМОН-транзистори, вся схема введення даних може бути розміщена у одній кишені для функціональних елементів, що дає додатковий виграш у площі. До того ж, завдяки вищій струмовій навантажувальній здатності nМОН-транзисторів порівняно з рМОНтранзисторами, вся схема може бути виконана особливо мініатюрною. 2 42887 Ця схема-защіпка у вигідному варіанті здійснення винаходу може складатися із двох інверторів, ввімкнених зустрічно-паралельно. Нижче винахід детальніше пояснюється з використанням ілюстрацій. На них зображено: фіг. 1 - принципова схема винайденої схеми керування; фіг. 2 - логічний елемент передачі; фіг. 3 - поперечний переріз комірки пам'яті з багаторівневим затвором; фіг. 4 - поперечний переріз комірки пам'яті з розщепленим затвором; фіг. 5 - матриця комірок запам'ятовуючого пристрою з шинами слів розрядними шинами. На фіг. 1 зображена принципова схема винайденої схеми керування. Ця схема керування складається із схеми 10 перетворення рівнів, схемизащіпки (Latch) 11 і схеми 12 введення даних. Схема 10 перетворення рівнів складається із рМОН-транзисторів рТ1, рТ2 і nМОН-транзисторів nТ4, nТ5 і має вихідні виводи В і ВН, з'єднані відповідно з розрядними шинами і шинами слів напівпровідникового ЗП. В залежності від значення напруги на вході даних ДАНІ (логічна "1" чи логічний "0") виходи В і ВН формують напругу програмування Vпpoг або 0 В. При цьому напруга на виході ВН комплементарна. До стоку чи витоку рМОН-транзисторів відповідно рТ1 і рТ2 прикладено зовнішню напругу Vпpoг, наприклад, 15 В. За допомогою транзисторів nТ4, nТ5, рТ1 і рТ2 здійснюється керування подачею цієї напруги Vпpoг на виходи В і ВН, причому, як було сказано вище, вихід ВН комплементарний виходу В. Схема перетворення рівнів, аналогічна використовуваній схемі 10 перетворення рівнів, відома із уже згаданого патенту США US-A-5,293,561. Перед схемою 10 перетворення рівнів ввімкнено схему-защіпку 11, яка складається із двох ввімкнених зустрічно-паралельно інверторів І1 і І2. Перед цією схемою-защіпкою 11 розміщено схему 12 введення даних, яка складається із трьох nМОН-транзисторів nТ1-nТ3. Дані, що підлягають запису у запам'ятовуючий пристрій, наприклад, напруга 5 В, що відповідає логічній "1", подаються через вхід для даних ДАНІ. При цьому витік чи стік транзистора nТ1 і затвор транзистора nТ3 з'єднані зі входом ДАНІ, а транзистори nТ2 і nТ3 з'єднані послідовно. Затвори транзисторів nТ1 і nТ2 з'єднані між собою із виводом управління записом ЗАПИС. Якщо, наприклад, на вивід ЗАПИС подано напругу 5 В, то транзистори nТ1 і nТ2 відкриті, внаслідок чого на лівому на фіг. 1 вході схемизащіпки 11 присутня напруга 0 В, а на правий вхід схеми-защіпки 11 через транзистор nТ1 передається вхідний сигнал логічної "1" (5 В за винятком напруги відсічки транзистора nТ1). Винайдена схема керування особливо придатна для даних, що мають бути записані у енергонезалежні напівпровідникові ЗП. В цій схемі керування здійснюється проміжне запам'ятовування вхідних даних у схемі-защіпці 11 і на кожну розрядну шину подається регульована напруга програмування Vпpoг. В такому застосуванні схема керування може бути передбачена окремо для кожної шини слів чи розрядної шини. Дані, що мають бути записані при програмуванні, подаються на вхід ДАНІ. Потім імпульсом позитивної полярності, поданим на вивід ЗАПИС, вони передаються у схему-защіпку 11. Потім, в залежності від значення даних на вході ДАНІ ("1" чи "0"), схема 10 перетворення рівнів формує на виходах В і ВН напруги Vпpoг чи 0 В відповідно. При цьому сигнал на виході ВН комплементарний до сигналу на виході N і становить 0 В чи Vпpoг, коли на виході В сигнал становить Vпpoг чи 0 В відповідно. Само зрозуміло, винайдена схема керування може бути використана для керування розрядною шиною та/або шиною слів для загального розподілу високих напруг. Схема 12 введення даних складається лише із трьох nМОН-транзисторів nТ1, nТ2 і nТ3. Таким чином, вона може бути реалізована просто і компактно, що має велике значення для растрових ЗП. Оскільки для її реалізації не використовуються рМОН-транзистори, ця частина схеми може бути виготовлена у спільній кишені, що означає суттєвий виграш у площі. При подачі на вхід ДАНІ логічного "0" схема керування передає напругу 0 В на правий на фіг. 1 вузол схеми-защіпки 11 через транзистор nТ1, а на лівий вузол через транзистори nТ2 і nТ3. Схема керування згідно з винаходом не потребує додаткових інверторів для керування транзисторами nТ4 і nТ5; цю функцію виконують інвертори I1 і I2 схеми-защіпки. Таким чином, вигідна комбінація схеми-защіпки 11 зі схемою 10 перетворення рівнів економить функціональні елементи і тому особливо придатна для застосування у критичних до площі матричних ЗП. 3 42887 ПМ-3962 Позиційні позначення Нові Старі 1. 1 2. 2 3. 3 4. 4 5. 5 6. 6 7. 7 8. 8 9. CG 10. D 11. S 12. BL0 13. WL0 14. 10 15. 11 16. 12 17. pT1 18. pT2 19. nT4 20. nT5 21. D 22. DN 23. ДАНІ 24. Vпpoг 25. І1 26. І2 27. nT1 28. nT2 29. NТ3 30. ЗАПИС Назва зона витоку зона стоку напівпровідникова підкладка тунельний оксидний шар плаваючий затвор проміжний шар 6 полідіелектрика керуючий затвор послідовний затвор УЗ затвор С стік В витік РШ0 розрядна шина ШС0 шина слів схема перетворення рівнів схема-защіпка (Latch) схема введення даних рМОН-транзистор рМОН-транзистор nМОН-транзистор nМОН-транзистор В(ихід) В(ихід) Н(егативний) вхід даних напруга програмування інвертор інвертор nМОН-транзистор nМОН-транзистор nМОН-транзистор керування записом 4 42887 Фіг. 1 Фіг. 2 Фіг. 3 5 42887 Фіг. 4 Фіг. 5 __________________________________________________________ ДП "Український інститут промислової власності" (Укрпатент) Україна, 01133, Київ-133, бульв. Лесі Українки, 26 (044) 295-81-42, 295-61-97 __________________________________________________________ Підписано до друку ________ 2002 р. Формат 60х84 1/8. Обсяг ______ обл.-вид. арк. Тираж 50 прим. Зам._______ ____________________________________________________________ УкрІНТЕІ, 03680, Київ-39 МСП, вул. Горького, 180. (044) 268-25-22 ___________________________________________________________ 6

ДивитисяДодаткова інформація

Назва патенту англійськоюControl chart for nonvolatile semiconductor storage unit

Автори англійськоюZettler Thomas

Назва патенту російськоюСхема управления для энергонезависимого полупроводникового запоминающего устройства

Автори російськоюЦеттлер Томас

МПК / Мітки

МПК: G11C 16/06

Мітки: енергонезалежного, пристрою, напівпровідникового, схема, керування, запам'ятовуючого

Код посилання

<a href="https://ua.patents.su/6-42887-skhema-keruvannya-dlya-energonezalezhnogo-napivprovidnikovogo-zapamyatovuyuchogo-pristroyu.html" target="_blank" rel="follow" title="База патентів України">Схема керування для енергонезалежного напівпровідникового запам’ятовуючого пристрою</a>

Попередній патент: Витискувач для контрольованої видачі дози рідини, яка знаходиться в картриджі

Наступний патент: Парогенератор, який працює на відхідному теплі

Випадковий патент: Спосіб перевірки терморезисторів