Пристрій для регулювання світлового режиму в птахівничих приміщеннях

Номер патенту: 15268

Опубліковано: 30.06.1997

Автори: Горго Олександр Дмитрович, Наконечний Володимир Васильович, Герасимчук Юрій Васильович

Формула / Реферат

Устройство для регулирования светового режима в птицеводческих помещениях, содержащее осветительные лампы, которые подключены к питающей сети через первый и второй встречно-параллельно включенные тиристоры, формирователь синхроимпульсов, первый и второй генераторы импульсов, RS-триггер, делитель частоты, первый и второй формирователи открывающих импульсов, выходы которых соединены с соответствующими управляющими входами первого и второго тиристоров, причем вход формирователя синхроимпульсов подключен к выводам питающей сети, а первый выход - к соединенным между собой R -входами RS-триггера и делителя частоты, счетный вход которого соединен с выходом первого генератора импульсов, отличающееся тем, что оно снабжено первым и вторым четырех входовыми элементами И, двоичным n - разрядным счетчиком, программируемым цифровым n-разрядным таймером, делителем частоты с изменяемым коэффициентом деления, первым и вторым цифровыми компараторами, формирователем импульса начальной установки, двоичным n-разрядным реверсивным счетчиком, элементами НЕ, (n+1) - входовым элементом И-НЕ, первым и вторым двухвходовыми элементами И-НЕ, задатчиком коэффициента деления, n-входовым элементом ИЛИ-НЕ, первым и вторым двухвходовыми элементами И, причем первые входы первого и второго четырехвходовых элементов И соединены соответственно с вторым и третьим выходами формирователя синхроимпульсов подключенного первым выходом к соединенным между собой R-входом двоичного n-разрядного счетчика и счетным входом делителя частоты с изменяемым коэффициентом деления, выход RS-триггера подключен к вторым входам первого и второго четырехвходовых элементов И третьи, входы которых соединены с выходом второго генератора импульсов, выход делителя частоты соединен со счетным входом двоичного n-разрядного счетчика, подключенного разрядными выходами к первой группе соответствующих входов первого цифрового компаратора, выход "равно" которого соединен с S-входом RS-триггера, выход формирователя импульса начальной установки подключен к соединенным между собой R-входам делителя частоты с изменяемым коэффициентом деления и двоичного n-разрядного реверсивного счетчика, подключенного разрядными выходами к первой группе соответствующих входов второго цифрового компаратора, а через элементы НЕ - к второй группе соответствующих входов первого цифрового компаратора и к входам (п+1) - входового элемента И-НЕ, выход которого соединен с первыми входами первого и второго двухвходовых элементов И-НЕ, задатчик коэффициента деления подключен разрядными выходами к соответствующим информационным входам делителя частоты с изменяемым коэффициентом деления, выход которого соединен со счетным входом двоичного n- разрядного реверсивного счетчика, разрядные выходы программируемого цифрового n -разрядного таймера соединены с второй группой соответствующих входов второго цифрового компаратора и с входами n-входового элемента ИЛИ-НЕ, подключенного выходом к свободным входам (п+1)- входового и первого двухвходового элемента И-НЕ, а через элемент НЕ -к одному из входов первого двухвходового элемента И, второй вход которого соединен с выходом "меньше" второго цифрового компаратора, а выход - с входом направления счета двоичного n -разрядного реверсивного счетчика, выход "равно" второго цифрового компаратора через элемент НЕ соединен со свободным входом второго двухвходового элемента И-НЕ, подключенного выходом к одному из входов второго двухвходового элемента И, второй вход которого соединен с выходом первого двухвходового элемента И-НЕ, а выход - с входом запрета счета двоичного n-разрядного реверсивного счетчика.

Текст

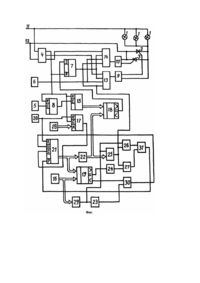

Предлагаемое изобретение относится к сельскохозяйственному производству и может быть использовано в осветительных установках помещений для выращивания птицы и сельскохозяйственных животных, где необходимо регулирование светового потока источников излучения, а также плавное включение и отключение освещения. Известен способ содержания кур-несушек в клетках [1], предусматривающий изменение интенсивности освещения в течение дня в две фазы: в первую - в течение 6 ... 9ч на уровне 5 ... 7лк и во вторую, в оставшийся период светового дня, повышение ее до 25 ... 30Лк. Общая длительность светового дня составляет 8 ... 9ч в 140-дневном возрасте птицы с постепенным увеличением по 0,5ч в неделю до 17ч в конце продуктивного периода. Изменение освещенности в течение дня создает условия, сходные с естественными при напольном содержании кур 8 гнездах. Способ позволяет достичь более полной реализации генетических потенций кур, Однако он предусматривает только две фазы изменения интенсивности освещения, которые не увязаны с периодами кормления птицы. Кроме того, отсутствует плавное увеличение и снижение освещенности при включении и отключении освещения. Это не позволяет получать максимальную экономию электроэнергии на освещении и увеличить срок службы источников излучения при одновременном повышении продуктивности птицы. Известно устройство для регулирования светового режима в птицеводческих помещениях [2], содержащее осветительные лампы, подключенные к питающей сети через стабилизатор-ограничитель переменного тока, который имеет на выходе два встречнопараллельно включенных тиристора и разделительный трансформатор, в цепь встречнопараллельно включенных тиристоров введен контакт программного реле времени и два диода. Анод первого диода соединен с катодом второго и с обмоткой разделительного трансформатора, а катод первого диода и анод второго соединены соответственно с анодом первого и катодом второго тиристора. При разомкнутых контактах программного реле времени питание осветительных ламп осуществляется только в один полупериод питающего напряжения, а при замкнутых контактах - в оба полупериода питающего напряжения. Это позволяет получить два уровня освещенности в помещении и возможность повысить точность имитации светового дня, что дает экономию электроэнергии на освещение. Недостатком этого устройства является то, что оно позволяет создавать только два уровня освещенности в помещениях для выращивания птицы и не дает возможности регулировать уровень освещенности, например в зависимости от возраста птицы, а также на протяжении светового дня. Не реализуется плавное изменение освещенности при переходе от высокого уровня освещенности до низкого и наоборот, что влечет появление стресса птицы. Это не позволяет обеспечивать наиболее благоприятное взаимодействие организма птицы с окружающей средой и кроме того, нерационально расходуется электроэнергия. Использование аналоговых сигналов в цепях управления углом открытия коммутирующих элементов снижает надежность устройства. Это связано с тем, что старание элементов и окружающая среда (температура, влажность и т.д.), оказывают существенное влияние на параметры отдельных элементов, а следовательно и на стабильность аналоговых сигналов. Известно устройство (прототип) для регулирования мощности нагрузки [3], содержащее нагрузку, например осветительные лампы, подключенные к питающей сети через первый и второй встречно-параллельно включенные тиристоры, формирователь синхроимпульсов, вход которого соединен с выводами для подключения питающей сети, первый и второй генераторы импульсов, RS-триггер, делитель частоты, первый и второй формирователи открывающих импульсов. Первый и второй выходы формирователя синхроимпульсов соединены с первыми управляющими входами соответственно первого и второго формирователей открывающих импульсов, выходы которых подключены к соответствующим управляющим входам первого и второго тиристоров, третий выход формирователя синхроимпульсов подключен к R-входам RSтриггера и делителя частоты, счетный вход которого соединен с выходом первого генератора импульсов, выход делителя частоты соединен с Sвходом RS-триггера, подключенного выходом к управляющему входу второго генератора импульсов, выход которого соединен с вторыми управляющими входами первого и второго формирователей открывающих импульсов. Устройство обеспечивает цифровое управление углом открытия тиристоров, а следовательно и регулирование светового потока осветительных ламп. Недостатком этого устройства является то, что плавное изменение светового потока осветительных ламп при включении и отключении освещения может осуществляться только вручную и отсутствует возможность реализовать режимы освещения по программе с регулировкой уровня освещенности как на протяжении светового дня, так и на протяжении всего цикла выращивания птицы. Уровень освещенности также изменяется только вручную. Кроме того, при возобновлении энергоснабжения, после плановых или аварийных отключений питающей сети, устройство не обеспечивает плавного нарастания светового потока ламп, что вызывает стресс птицы и снижает строк службы ламп накаливания. Необходимо учитывать и то, что в этом устройстве разница между углами открытия тиристоров соседних полупериодов синусоиды напряжения питающей сети зависит от частоты выходных импульсов первого генератора импульсов. Поэтому при работе устройства, в частности, с малой частотой выходных импульсов первого генератора, что соответствует малой мощности в нагрузке, наблюдается "качание" фазы включения тиристоров. Это создает повышенную пульсацию светового потока осветительных ламп при низких уровнях освещенности, что отрицательно сказывается на продуктивности птицы и условиях работы обслуживающего персонала. Задачей изобретения является создание устройства для регулирования светового режима в птицеводческих помещениях, в котором, благодаря применению цифрового управления углом открытия коммутирующих элементов осуществляется управление световым режимом в птицеводческом помещении как на протяжении светового дня, так и на протяжении всего цикла выращивания птицы по заданной программе с плавным изменением освещенности мест обитания птицы при включении и отключении освещения и при переходах от низких уровней освещенности к высоким и наоборот. При этом обеспечивается повышение точности имитации светового дня на протяжении всего цикла выращивания птицы, экономия электроэнергии на освещение и снижение пульсаций светового потока осветительных ламп. Задача решается благодаря тому, что в устройство для регулирования светового режима в птицеводческих помещениях, содержащее осветительные лампы, подключенные к питающей сети через первый и второй встречно-параллельно включенные тиристоры, формирователь синхроимпульсов, первый и второй генераторы импульсов, RS-триггер, делитель частоты, первый и второй формирователи открывающих импульсов, выходы которых соединены с соответствующими управляющими входами первого и второго тиристоров, вход формирователя синхроимпульсов подключен к выводам питающей сети, а первый выход - к Соединенным между собой R-входами RSтриггера и делителя частоты, счетный вход которого соединен с выходом первого генератора импульсов, введены первый и второй четырехвходовые элементы И, двоичный nразрядный счетчик, программируемый цифровой n-разрядный таймер, делитель частоты с изменяемым коэффициентом деления, первый и второй цифровые компараторы, формирователь импульса начальной установки, двоичный nразрядный реверсивный счетчик, элементы НЕ, (n + 1)-входовой элемент И-НЕ, первый и второй двухвходовые элементы И-НЕ, задатчик коэффициента деления, n-входовой элемент ИЛИНЕ, первый и второй двухвходовые элементы И, причем первые входы первого и второго четырехвходовых элементов И соединены соответственно с вторым и третьим выходами формирователя синхроимпульсов подключенного первым выходом к соединенным между собой Rвходом двоичного n-разрядного счетчика и счетного входа делителя частоты с изменяемым коэффициентом деления, выход RS-триггера подключен к вторым входам первого и второго четырехвходовых элементов И, третьи входы которых соединены с выходом второго генератора импульсов, выход делителя частоты соединен со счетным входом двоичного n-разрядного счетчика, подключенного разрядными выходами к первой группе соответствующих входов первого цифрового компаратора, выход "равно" которого соединен с S-входом RS-триггера, выход формирователя импульса начальной установки подключен к соединенным между собой R-входами делителя частоты с изменяемым коэффициентом деления и двоичного n-разрядного реверсивного счетчика, подключенного разрядными выходами к первой группе соответствующих входов второго цифрового компаратора, а через элементы НЕ - к второй группе соответствующих входов первого цифрового компаратора и к входам (n + 1)входового элемента И-НЕ, выход которого соединен с первыми входами первого и второго двухвходовых элементов И-НЕ, задатчик коэффициента деления подключен разрядными выходами к соответствующим информационным входам делителя частоты с изменяемым коэффициентом деления, выход которого соединен со счетным входом двоичного n-разрядного реверсивного счетчика, разрядные выходы программируемого цифрового n-разрядного таймера соединены с второй группой соответствующих входов второго цифрового компаратора и с входами n-входового элемента ИЛИ-НЕ подключенного выходом к свободным входам (n + 1)-входового и первого двухвходово-го элементов И-НЕ, а через элемент НЕ - к одному из входов первого двухвходового элемента И, второй вход которого соединен с выходом "меньше" второго цифрового компаратора, а выход - с входом направления счета двоичного n-разрядного реверсивного счетчика, выход "равно" второго цифрового компаратора через элемент НЕ соединен со свободным входом второго двухвходового элемента И-НЕ, подключенного выходом к одному из входов второго двухвходового элемента И, второй вход которого соединен с выходом первого двухвходового элемента И-НЕ, а выход - с входом запрета счета двоичного nразрядного реверсивного счетчика. Аналогов отличительной части формулы изобретения не обнаружено. На чертеже (фиг.) представлена схема устройства для регулирования светового режима в птицеводческих помещениях. Устройство содержит осветительные лампы 1, первый и второй тиристоры 2 и 3, формирователь синхроимпульсов 4, первый и второй генераторы импульсов 5 и 6, делитель частоты 8, RS-триггер 7, первый и второй формирователи открывающих импульсов 9 и 10, выходы которых соединены с соответствующими управляющими входами первого и второго тиристоров 2 и 3. К выводам 11, 12 для присоединения к питающей сети переменного тока через встречно-параллельно включенные первый и второй тиристоры 2, 3 подключены осветительные лампы 1, а также вход формирователя синхроимпульсов 4, первый выход которого соединен с R-входами RS-триггера 7 и делителя частоты 8, подключенного счетным входом к выходу первого генератора импульсов 5. Устройство содержит также первый и второй четырехвходовые элементы И13 и 14, двоичный nразрядный счетчик 15, программируемый цифровой n-разрядный таймер 16, делитель частоты 17 с изменяемым коэффициентом деления, первый и второй цифровые компараторы 18 и 19, формирователь импульса начальной установки 20, двоичный n-разрядный реверсивный счетчик 21, n элементов НЕ 22, (n + 1) - й элемент НЕ 23, (n + 2) - й элемент НЕ 24, (n + 1)-входовой элемент И-ИЕ 25, первый и второй двухвходовые элементы И-НЕ 26 и 27, задатчик коэффициента деления 28, n-входовой элемент ИЛИ-НЕ 29, первый и второй двухвходовые элементы И 30 и 31. Первые входы первого и второго четырехвходовых элементов И 13 и 14 соединены соответственно с вторым и третьим выходами формирователя синхроимпульсов 4, первый выход которого подключен также к соединенным между собой R-входом двоичного n-разрядного счетчика 15 и счетным входом делителя частоты 17 с изменяемым коэффициентом деления. Выход RSтриггера 7 подключен к вторым входам первого и второго четырехвходовых элементов И 13 и 14 третьи входы которых соединены с выходом второго генератора импульса 6. Выход делителя частоты 8 соединен со счетным входом двоичного n-разрядного счетчика 15, подключенного разрядными выходами к первой группе соответствующих входов первого цифрового компаратора 19, выход "равно" которого соединен с S-входом RS-триггера 7. Выход формирователя импульса начальной установки 20 подключен к соединенным между собой R-входами делителя частоты 17 с изменяемым коэффициентом деления и двоичного n-разрядного реверсивного счетчика 15, подключенного разрядными выходами к первой группе соответствующих входов второго цифрового компаратора 19, а через п элементов НЕ 22 - к второй группе соответствующих входов первого цифрового компаратора 18 и к входам (n + 1)-входового элемента И-НЕ 25, выход которого соединен с первыми входами первого и второго двухвходовых элементов И-НЕ 26 и 27. Задатчик коэффициента деления 28 подключен разрядными выходами к соответствующим информационным входам делителя частоты 17 с изменяемым коэффициентом деления, выход которого соединен со счетным входом двоичного nразрядного реверсивного счетчика 21. Разрядные выходы программируемого цифрового nразрядного таймера 16 соединены с второй группой соответствующих входов второго цифрового компаратора 19 и с входами nвходового элемента ИЛИ-НЕ 29, подключенного выходом к свободным входам (m + 1)-входового элемента И-НЕ 25 и первого двухвходового элемента И-НЕ 26, а через (n + 1) - й элемент НЕ 23 - к одному из входов первого двухвходового элемента И 29, второй вход которого соединен с выходом "меньше" второго цифрового компаратора 19, а выход - с входом направления счета двоичного n-разрядного реверсивного счетчика 21. Выход "равно" второго цифрового компаратора 19 через (n + 2) - й элемент НЕ 24 соединен со свободным входом второго двухвходового элемента И-НЕ 27, подключенного выходом к одному из входов второго двухвходового элемента И 31, второй вход которого соединен с выходом первого двухвходового элемента И-НЕ 26, а выход - с входом запрета счета двоичного n-разрядного реверсивного счетчика 21. Функции программируемого цифрового nразрядного таймера 16 может выполнять любой из известных программируемых устройств, например реле времени 2 РВМ. Остальные элементы отличительной части предлагаемого изобретения имеются в номенклатуре большинства существующих серий микросхем. Устройство работает следующим образом. К выводам 11 и 12 подается напряжение питающей сети. На первом выходе формирователя синхроимпульсов 4 в моменты перехода синусоиды напряжения питающей сети через нуль формируются короткие прямоугольные импульсы, а на его втором и третьем выходах формируются прямоугольные импульсы на протяжении соответственно положительной и отрицательной полуволн синусоид напряжения питающей сети, которые подаются на первые входы четырехвходовых элементов И 13 и 14. Второй генератор импульсов 6 формирует импульсы с частотой 5 - 6кГц, которые поступают на третьи входы четырехвходовых элементов И 13 и 14. Первый генератор импульсов 5 формирует импульсы, частота которых определяется по формуле где - частота импульсов на выходе первого генератора импульсов 5, Гц; - количество разрядных выходов двоичного n-разрядного счетчика 15; - коэффициент деления делителя частоты 8; - частота напряжения питающей сети, Гц. В момент подключения устройства к питающей сети на выходе формирователя импульса начальной установки 20 формируется прямоугольный импульс, который устанавливает делитель частоты с изменяемым коэффициентом деления 17 и двоичный n-разрядный реверсивный счетчик 21 в нулевое состояние. При нулевом коде на разрядных выходах программируемого цифрового n-разрядного таймера 16 на выходе n-входового элемента ИЛИНЕ 29 появляется сигнал логической единицы, который поступает на один из входов (n + 1)входового элемента И-НЕ 25, на остальные входы которого также поступают сигналы логической единицы с разрядных выходов двоичного nразрядного реверсивного счетчика 21 через n элементов НЕ 22. На выходе (n + 1)-входового элемента И-НЕ 25 установится сигнал логического нуля, который поступает на четвертые входы четырехвходовых элементов И13 и 14. Поэтому на выходах этих элементов, а также на выходах первого и второго формирователей открывающих импульсов 9 и 10 установится сигнал логического нуля. Первый и второй тиристоры 2 и 3 останутся в закрытом состоянии, ток через осветительные лампы 1 протекать не будет. Это соответствует отключенному состоянию освещения. Кроме того, поскольку с выхода (n + 1)входового элемента И-НЕ 25 сигнал логического нуля поступает также и на первые входы двухвходовых элементов И-НЕ 26 и 27, то на их выходах, а также на выходе двухвходового элемента И 31, установится сигнал логическом единицы. Этот сигнал поступает на вход запрета счета двоичного n-разрядного реверсивного счетчика 21. Счет импульсов прекращается. Сигнал логического нуля на разрядных выходах двоичного n-разрядного реверсивного счетчика 21 не изменяется, освещение останется отключенным. Если на разрядных выходах программируемого цифрового n-разрядного таймера 16 устанавливается код отличный от нуля, то на выходе n-входового элемента ИЛИ-НЕ 29 появляется сигнал логического нуля, а на выходе (n + 1)-входового элемента И-НЕ 25 сигнал логической единицы, который поступает на четвертые входы четырехвходовых элементов И 13 и 14. Сигнал логической единицы с выхода (n + 1)входового элемента И-НЕ 25 поступает также на первый вход второго двухвходового элемента И-НЕ 27. Поскольку к второй группе соответствующих входов второго цифрового компаратора 19 с разрядных выходов программируемого цифрового n-разрядного таймера 16 поступает код отличный от нуля, а к первой группе входов этого компаратора от разрядных выходов двоичного nразрядного реверсивного счетчика поступает нулевой код, то на выходе "равно" второго цифрового компаратора 19 появится сигнал логического нуля. Следовательно, на второй вход второго двухвходового элемента И-НЕ 27 поступит сигнал логической единицы, а на выходе этого элемента появится сигнал логического нуля. Поэтому на выходе второго двухвходового элемента И 31 будет сигнал логического нуля, который поступает на вход запрета счета двоичного n-разрядного реверсивного счетчика 21. Счет импульсов разрешается. Причем, поскольку код первой группы входов второго цифрового компаратора 19 меньше кода на его второй группе входов, то на выходе "меньше" этого компаратора будет сигнал логической единицы, который поступает на второй вход первого двухвходового элемента И 30. На первый вход этого элемента через (n + 1) - й элемент НЕ 23 с выхода nвходового элемента ИЛИ-НЕ 29 также поступает сигнал логической единицы. Поэтому на выходе первого двухвходового элемента И 30 будет сигнал логической единицы, который поступает на вход направления счета двоичного n-разрядного реверсивного счетчика 21. При этом каждый импульс на счетном входе этого счетчика будет увеличивать код на его разрядных выходах на единицу. Когда код, который поступает с разрядных выходов n-разрядного реверсивного счетчика 21 к первой группе соответствующих входов первого цифрового компаратора 19, станет равным коду, который поступает с разрядных выходов nразрядного таймера 16 к второй группе соответствующих входов этого же компаратора, на его выходе "равно" появится сигнал логической единицы, а на выходе (n + 2) - го элемента НЕ 24 сигнал логического нуля. Поскольку код на разрядных выходах n-разрядного реверсивного счетчика 21 стал отличным от нуля, то на входы (n + 1)-входового элемента И-НЕ 25 поступает код отличный от единицы. Следовательно, на выходе этого элемента устанавливается сигнал логической единицы, который поступает на четвертые входы первого и второго четырехвходовых элементов И 13 и 14 и на второй вход двухвходового элемента И-НЕ 26, а также на первый вход двухвходового элемента И-НЕ 27, на второй вход которого поступает сигнал логического нуля. На выходе двухвходового элемента И-НЕ 27 устанавливается сигнал логической единицы, который поступает на второй вход двухвходового элемента И 31. Поскольку при не нулевом коде на разрядных выходах nразрядного таймера 16, на выходе n-входового элемента ИЛИ-НЕ 29 устанавливается сигнал логического нуля, который поступает на первый вход двухвходового элемента И-НЕ 26, на его выходе появится сигнал логической единицы. Наличие сигнала логической единицы на первом и втором входах двухвходового элемента И 31 приводит к появлению такого же сигнала на его выходе, который поступает на вход запрета счета двоичного n-разрядного реверсивного счетчика 21. Счет импульсов прекращается. Таким образом, если нулевой код на разрядных выходах n-разрядного таймера 16 в некоторый момент времени становится отличным от нуля, то код на разрядных выходах n-разрядного реверсивного счетчика 21 через промежутки времени T увеличивается на единицу. Величина этого промежутка времени определяется по формуле где 17; - коэффициент деления делителя частоты - частота напряжения питающей сети. При этом, код на разрядных выходах n-разрядного реверсивного счетчика 21 увеличивается до тех пор, пока не станет равным коду на разрядных выходах n-разрядного таймера 16. В этот момент времени, когда код на разрядных выходах n-разрядного таймера 16 устанавливается отличным от нуля, код на разрядных выходах n-разрядного реверсивного счетчика 21 сохраняется нулевым и остается таковым на протяжении времени T. Следовательно, на протяжении этого промежутка времени к второй группе входов первого цифрового компаратора 18 будет поступать единичный код. К первой группе входов этого компаратора поступает код, который на протяжении полупериода напряжения питающей сети изменяется от нулевого до единичного. Нулевой код устанавливается в момент перехода синусоиды напряжения питающей сети через нуль, поскольку короткие прямоугольные импульсы, которые поступают с выхода формирователя синхроимпульсов 4 в эти моменты времени на Rвход n-разрядного счетчика 15 устанавливают его в нулевое состояние. На протяжении полупериода напряжения питающей сети импульсы с выхода первого генератора импульсов 5 через делитель частоты 8 увеличивают нулевой код на разрядных выходах n-разрядного счетчика 15, а следовательно и на первой группе входов первого цифрового компаратора 18 - до единичного. В момент появления единичного кода на первой группе входов первого цифрового компаратора 18, на его выходе "равно" появляется сигнал логической единицы, который переводит в единичное состояние RS-триггер 7. Следовательно, на вторых входах первого и второго четырехвходовых элементов И 13 и 14 появляется сигнал логической единицы. В момент появления этого сигнала импульсы с выхода второго генератора импульсов 6 поступают на входы первого и второго формирователей открывающих импульсов 9 и 10. Причем, на вход первого формирователя открывающих импульсов 9 импульсы с выхода второго генератора импульсов 6 поступят при прохождении отрицательной полуволны синусоиды напряжения питающей сети, поскольку в эти промежутки времени на третьем выходе формирователя синхроимпульсов 4 формируется сигнал логической единицы, который поступает только на первый вход первого четырехвходового элемента И 13. На вход второго формирователя открывающих импульсов 10 импульсы с выхода второго генератора импульсов 6 поступят при прохождении положительной полуволны синусоиды напряжения питающей сети, так как в эти промежутки времени на втором выходе формирователя синхроимпульсов 4 формируется сигнал логической единицы, который поступает только на первый вход второго четырехвходового элемента И 14. Таким образом, в периоды прохождения отрицательной и положительной полуволн синусоиды напряжения питающей сети, когда коды на первой и второй группе входов первого цифрового компаратора 18 сравниваются, открывающие импульсы поступают на управляющие входы соответственно первого и второго тиристоров 2 и 3. При единичном коде, который поступает на вторую группу входов первого цифрового компаратора 18, угол открытия тиристоров 2 и 3 наибольший и определяется по формуле где 3; 8; - наибольший угол открытия тиристоров 2 и - коэффициент деления делителя частоты - количество разрядных выходов двоичного n-разрядного счетчика 15; - частота напряжения питающей сети, Гц: - частота импульсов на выходе первого генератора импульсов 5, Гц. Через промежуток времени T, когда код на разрядных выходах n-разрядного реверсивного счетчика 21 увеличивается на единицу, единичный код на второй группе входов первого цифрового компаратора 18 уменьшается на единицу. Поэтому, для формирования такого же кода на первой группе входов первого цифрового компаратора 18 потребуется меньший промежуток времени и сигнал логической единицы на выходе "равно" этого компаратора появится раньше, угол открытия тиристоров 2 и 3 уменьшится. Таким образом, увеличение кода на разрядных выходах n-разрядного реверсивного счетчика 21 приводит к уменьшению угла открытия тиристоров 2 и 3. Когда код на разрядных выходах n-разрядного реверсивного счетчика достигнет единичного значения, тогда на вторую группу входов первого цифрового компаратора 18 поступит нулевой код и сигнал логической единицы на его выходе "равно" будет формироваться в момент перехода синусоиды напряжения питающей сети через нуль. Следовательно, открывающие импульсы на управляющие входы первого и второго тиристоров 2 и 3 будут поступать на протяжении всего полупериода синусоиды напряжения питающей сети. Уменьшение угла открытия тиристоров 2 и 3 от наибольшего значения до нуля приводит к увеличению тока через осветительные лампы 1, а следовательно и их светового потока. Продолжительность промежутка времени, на протяжении которого световой поток осветительных ламп изменяется от нулевого до максимального значения определяется по формуле где 17; - коэффициент деления делителя частоты - количество разрядных выходов двоичного n-разрядного счетчика 15; - частота напряжения питающей сети, Гц; Поскольку в моменты перехода синусоиды напряжения питающей сети через ноль делителя частоты 8 и двоичный n-разрядный счетчик 15 устанавливаются в нулевое состояние, то разница между моментами времени на протяжении двух соседних полупериодов напряжения питающей сети, когда появляется соответствующий код на разрядных выходах двоичного n-разрядного счетчика или сигналы логической единицы на выходе "равно" первого цифрового компаратора 18, будет количественной характеристикой "качания" угла открытия тиристоров 2 и 3. Численное значение этой разницы определяется по формуле где - промежуток времени между моментами отпирания тиристоров 2 и 3 соседних полупериодов напряжения питающей сети, с; - количество разрядных выходов двоичного n-разрядного счетчика 15; - коэффициент деления делителя частоты 8; - частота напряжения питающей сети, ГЦ. "Качание" угла открытия тиристоров 2 и 3 не зависит от частоты на выходе первого генератора импульсов 5 и при достаточно большом количестве разрядных выходов двоичного n-разрядного счетчика 15 n и соответствующем коэффициенте деления делителя частоты 8 пульсации светового потока осветительных ламп 1 не ощущается. Для снижения светового потока осветительных ламп 1 на разрядных выходах программируемого цифрового таймера 16 устанавливают код отличный от единичного. При этом, поскольку код на первой группе входов второго цифрового компаратора 19 стал больше кода на его второй группе входов, то на выходе "меньше" этого компаратора установится сигнал логического нуля, который поступает на второй вход первого двухвходового элемента И 30. На выходе этого элемента также устанавливается сигнал логического нуля, который поступает не вход направления счета двоичного n-разрядного реверсивного счетчика 21. Кроме того, поскольку код на первой группе входов второго цифрового компаратора 19 не равен коду на его второй группе входов, то на выходе "равно" этого компаратора будет сигнал логического нуля, который поступает на вход элемента НЕ 24. С выхода этого элемента сигнал логической единицы поступает на второй вход второго двухвходового элемента И-НЕ 27, на первый вход которого с выхода (n + 1)-входового элемента И-НЕ 25 также поступает сигнал логической единицы. Поэтому на выходе второго двухвходового элемента И-НЕ 27 установится сигнал логического нуля, который поступает на второй вход второго двухвходового элемента И 31 и на его выходе также появится сигнал логического нуля. Этот сигнал поступает на вход запрета счета двоичного n-разрядного реверсивного счетчика 21. Счет импульсов разрешается. При этом каждый импульс на счетном входе двоичного n-разрядного реверсивного счетчика 21 будет уменьшать код на его разрядных выходах на единицу. В то же время код, который поступает на вторую группу входов первого цифрового компаратора 18 будет увеличиваться на единицу. Поэтому, для формирования такого же кода на первой группе входов первого цифрового компаратора 18 потребуется больший промежуток времени и сигнал логической единицы на выходе "равно" этого компаратора появится позже, угол открытия тиристоров 2 и 3 увеличится, а световой поток осветительных ламп 1 уменьшится. Следующий импульс, который поступает на счетный вход двоичного n-разрядного реверсивного счетчика 21 опять увеличит код, который поступает на вторую группу входов первого цифрового компаратора 18 на единицу, Угол открытия тиристоров 2 и 3 снова увеличится, а световой поток осветительных ламп 1 соответственно уменьшится. Когда код, который поступает на первую группу входов второго цифрового компаратора 19 станет равным коду, который поступает на вторую группу входов этого компаратора, на его выходе "равно" появится сигнал логической единицы. Это приводит к появлению сигнала логической единицы на входе запрета счета двоичного nразрядного реверсивного счетчика 21. Счет импульсов запрещается. Таким образом, угол открытия тиристоров 2 и 3, а следовательно и световой поток осветительных ламп 1 будет соответствовать тому коду, который установлен на разрядных выходах цифрового n-разрядного таймера 16. При этом световой поток осветительных ламп 1 остается неизменным пока не изменится код на разрядных выходах цифрового n-разрядного таймера 16. Для отключения освещения на разрядных выходах программируемого цифрового таймера 16 устанавливают нулевой код. При этом, поскольку код, который поступает на первую группу входов второго цифрового компаратора 19, стал больше кода, который поступает на вторую группу входов, то на выходе "меньше" этого компаратора устанавливается сигнал логического нуля, который поступает на второй вход первого двухвходового элемента И 30. На выходе этого элемента также устанавливается сигнал логического нуля, который поступает на вход направления счета двоичного nразрядного реверсивного счетчика 21. Кроме того, поскольку код на первой группе входов второго цифрового компаратора 19 не равен коду на его второй группе входов, то на выходе "равно" этого компаратора будет сигнал логического нуля, который поступает на вход элемента НЕ 24. С выхода этого элемента сигнал логической единицы поступает на второй вход двухвходового элемента И-НЕ 27, на первый вход которого с выхода (n + 1)-входового элемента И-НЕ 25 также поступает сигнал логической единицы. Поэтому на выходе второго двухвходового элемента И-НЕ 27 установится сигнал логического нуля, который поступает на второй вход второго двухвходового элемента И 31 и на его выходе также появится сигнал логического нуля. Этот сигнал поступает на вход запрета счета двоичного n-разрядного реверсивного счетчика 21. Счет импульсов разрешается. При этом, каждый импульс на счетном входе двоичного n-разрядного реверсивного счетчика 21 будет уменьшать код на его разрядных выходах на единицу, а код, который поступает на вторую группу входов первого цифрового компаратора 18, будет увеличиваться на единицы. Это приводит к соответствующему увеличению угла открытия тиристоров 2 и 3 и снижения светового потока осветительных ламп 1. Когда код на разрядных выходах двоичного nразрядного реверсивного счетчика 21 станет нулевым, то на выходе (n + 1)-входового элемента И-НЕ 25 появится сигнал логического нуля, который поступает на четвертые входы первого и второго четырехвходовых элементов И 13 и 14. На выходе этих элементов, а следовательно на входах первого и второго формирователей открывающих импульсов 9 и 10, установится сигнал логического нуля. Первый и второй тиристоры 2 и 3 закрываются, освещение отключается. Кроме того, поскольку на первые входы первого и второго двухвходовых элементов И-НЕ 26 и 27 поступает сигнал логического нуля, то на их выходах, а следовательно на входах элемента И 31, будет сигнал логической единицы. С выхода этого элемента сигнал логической единицы поступает на вход запрета счета двоичного n-разрядного реверсивного счетчика 21. Счет импульсов запрещается. В таком состоянии устройство находится все время пока на разрядных выходах программируемого цифрового n-разрядного таймера 16 установлен нулевой код. Таким образом, путем установки на разрядных выходах программируемого цифрового nразрядного таймера 16 соответствующего кода реализуется плавное изменение освещенности при включении освещения и при переходах от высокого уровня освещенности до низкого и наоборот, а также при отключении освещения. Кроме того, имеется возможность поддерживать необходимый уровень освещенности на протяжении заданного промежутка времени. Это позволяет исключить стрессовые ситуации, обеспечить наиболее благоприятное взаимодействие организма птицы с окружающей средой, повысить точность имитации светового дня, что дает экономию электроэнергии на освещение. Использование цифровых сигналов для управления углом открытия коммутирующих элементов повышает надежность устройства.

ДивитисяДодаткова інформація

Назва патенту англійськоюAppliance for control of light mode in poultry keeping premises

Автори англійськоюHerasymchuk Yurii Vasyliovych, Nakonechnyi Volodymyr Vasyliovych, Horho Oleksandr Dmytrovych

Назва патенту російськоюУстройство для регулировки светового режима в птицеводческих помещениях

Автори російськоюГерасимчук Юрий Васильевич, Наконечный Владимир Васильевич, Горго Александр Дмитриевич

МПК / Мітки

МПК: G05F 1/44

Мітки: птахівничих, регулювання, режиму, приміщеннях, світлового, пристрій

Код посилання

<a href="https://ua.patents.su/7-15268-pristrijj-dlya-regulyuvannya-svitlovogo-rezhimu-v-ptakhivnichikh-primishhennyakh.html" target="_blank" rel="follow" title="База патентів України">Пристрій для регулювання світлового режиму в птахівничих приміщеннях</a>