Пристрій для приймання і обробки команд телеуправління

Формула / Реферат

Устройство для приема и обработки команд телеуправления, содержащее приемник, вход которого является входом устройства, первый и второй выходы приемника соединены соответственно с входом генератора импульсов и через первый инвертор с первым входом первого компаратора, блок усилителей, выходы которого соединены с одноименными входами выходного блока, первый и второй счетчики, первый выход второго счетчика соединен с первым входом первого элемента ИЛИ, второй — четвертый элементы ИЛИ, первый и второй элементы И, первые распределитель импульсов, триггер и блок памяти, преобразователь параллельного кода в последовательный и eлемент задержки, отличающееся тем, что, с целью повышения информативности устройства, в него введены блок датчиков, коммутатор, группа регистров сдвига, демультиплексор, формирователи импульсов, второй распределитель импульсов, второй блок памяти, второй — шестой триггеры, третий — шестой элементы И, пятый и шестой элементы ИЛИ и второй — четвертый инверторы, первый выход генератора импульсов соединен непосредственно с первым входом коммутатора и через первый формирователь импульсов с первыми входами первого распределителя импульсов и второго элемента И, второй выход генератора импульсов соединен с первыми входами второго счетчика и второго распределителя импульсов, третий выход генератора импульсов соединен со вторым входом коммутатора, выход которого соединен через второй инвертор с первым входом демультиплексора и непосредственно с первым входом третьего элемента И и вторым входом второго счетчика, второй выход которого соединен с первым входом первого счетчика, третьим входом второго счетчика и вторым входом первого элемента ИЛИ, выход первого элемента ИЛИ соедине» с первым входом третьего элемента ИЛИ, выход которого соединен с первыми входами первого и второго блоков памяти, выход первого блока памяти соединен с первыми входами регистров сдвига группы и второго триггера и вторым входом компаратора, выход которого соединен с первым входом третьего триггера, инверсный выход которого соединен через элемент задержки с входом третьего инвертора и первым входом четвертого триггера и непосредственно со вторым входом второго элемента И, выход которого соединен со вторым входом третьего триггера, выход третьего инвертора соединен с первым входом второго формирователя импульсов, зыход которого соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с первыми входами первого, пятого и шестого триггеров, второй вход и инверсный выход первого триггера соединены соответственно с первым выходом приемника и вторым входом первого распределителя импульсов, первый и второй выходы которого соединены со вторыми входами соответственно пятого и шестого триггеров, третьи входы которых и первый вход первого элемента И подключены ко второму выходу приемника, третий выход первого распределителя импульсов соединен со своим третьим входом и вторым входом первого счетчика, третий вход которого подключен к первому выходу приемника, выходы группы выходов первого счетчика соединены с соответствующими входами группы входов первого и второго блоков памяти, демультиплексора и преобразователя параллельного кода в последовательный, первый выход первого счетчика соединен непосредственно с первым входом третьего формирователя импульсов и через четвертый инвертор с третьим входом третьего триггера и первым входом четвертого элемента И, второй выход первого счетчика соединен со вторыми входами четвертого триггера и второго формирователя импульсов, выход третьего формирователя импульсов соединен с вторым входом четвертого элемента ИЛИ и третьим входом четвертого триггера, выход которого соединен с вторым входом третьего формирователя импульсов, третьим входом коммутатора и первым входом пятого элемента И, выход которого соединен с вторым входом демультиплексора, выходы которого соединены с вторыми входами одноименных регистров сдвига группы, выходы которых соединены с соответствующими входами блока усилителей, выход пятого триггера соединен с вторым входом пятого элемента И и спервым входом второго элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого соединен с вторым входом первого блока памяти, выход шестого триггера соединен с вторыми входами второго элемента ИЛИ и третьего элемента И, инверсный выход которого соединен с вторым входом второго распределителя импульсов, первый выход которого соединен с вторым входом второго триггера и первым входом шестого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, второй выход второгo распределителя импульсов соединен с третьими входами четвертого элемента ИЛИ и второго триггера, инверсный выход которого соединен с вторым входом первого элемента И, выход которого соединен с третьим входом первого блока памяти, прямой выход второго триггера соединен с вторыми входами шестого элемента И и пятого элемента ИЛИ и первым входом шестого элемента ИЛИ, выход которого соединен с вторым входом второго блока памяти, выходы блока датчиков соединены с соответствующими входами преобразователя параллельного кода в последовательный, выход которого соединен с вторым входом шестого элемента ИЛИ и третьим входом второго блока памяти, выход которого и выход выходного блока являются соответственно выходом сигнализации и выходом управления устройства.

Текст

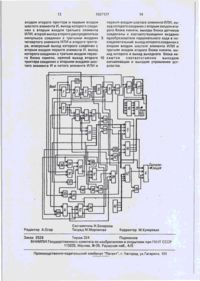

СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИК (19) (И) (51)5 G 0 8 C 19/28 ГОСУДАРСТВЕННЫЙ КОМИТЕТ ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ ПРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21)4713121/24 (22)03,07.89 * (46)30.07.91. Бюл. №28 (71) Житомирское производственное объединение "Промавтоматика" (72) М.Л. Портнов (53)621.398(088.8) (56) Авторское свидетельство СССР № 1441436,кл. G 08 С 19/28, 1987. (54) УСТРОЙСТВО ДЛЯ ПРИЁМА И ОБРАБОТКИ КОМАНД ТЕЛЕУПРАВЛЕНИЯ (57) Изобретение относится к системам телемеханики для охранной сигнализации, в которых требуется принимать команды телеуправления охраняемыми объектами. Цель изобретения - повышение информативности устройства. Устройство содержит приемник команд, генератор тактовых импульсов, распределители импульсов, блоки памяти, триггеры, счетчики, коммутатор, демультиплексор группу регистров сдвига, блок усилителей, выходной блок, компаратор, элементы ИЛИ, формирователи импульсов, элементы И, инверторы, элемент задержки, блок датчиков телесигналов и преобразователь параллельного кода в последовательный. 1 ил. Изобретение относится к-телемеханике и может быть использовано, в частности, в системах охранной сигнализации для приема команд телеуправления типа "Взять объект на охрану" или "Снять объект с охраны", в которых также требуется фиксировать любые нарушения нормального состояния контролируемых объектов и блокировать чувствительность к переходам этих объектов из аварийного в нормальное состояние до поступления специальных команд квитирования телесигналов как результат реакции оператора на каждый ранее принятый аварийный телесигнал. Цель изобретения - повышение информативности устройства путем фиксирования всех вновь возникающих аварийных телесигналов и блокировки чувствительности к переходам контролируемых объектов из аварийного в нормальное состояние де получения индивидуальных команд квитирования телесигналов, подтверждающих прием ранее выданных аварийных телесигналов. На чертеже показана структурная схема предлагаемого устройства. Устройство содержит приемник 1 команд, генератор 2 тактовых импульсов, первый и второй распределители 3 и 4 импульсов, первый и второй блоки 5 и б памяти, первый, пятый, шестой, третий, четвертый и второй триггеры 7-12, первый и второй счетчики 13 и 14, коммутатор 15, демультиплексор 16, группу регистров 17 сдвига, блок 18 усилителей, выходной блок 19 (блок выходных реле), компаратор 20, с первого по шестой элементы ИЛИ 21-26, первый, третий и второй формирователи 2729 импульсов, первый, второй, пятый, четвертый, шестой и третий элементы И 30-35, первый, четвертый, третий и второй инверторы 36-39, элемент 40 задержки, блок 41 датчиков телесигналов и преобразователь 42 параллельного кода ь последовательный. Устройство работает следующим образом. Последовательный код команд телеуправления и квитирования телесигналов, 1667137 включающий синхронизирующую посылку (стартовую комбинацию), признаки передачи вида передаваемой команды, а также поэиционный код устанавливаемого состояния объекта управления или адреса 5 квитируемого телесигнала, повторенный дважды с целью повышения достоверности, поступают из линии связи в^ приемник 1. После выделения приемником 1 синхронизирующей посыки образуется сигнал на его 10 первом выходе. Этим сигналом, подаваемым на вход генератора 2, корректируется фаза тактовых сигналов, выдаваемых по первому выходу генератора 2, так что устанавливается соответствие мвжду фронтами 15 сигналов генератора 2 и информационными сигналами, выделяемыми приемником 1 и выдаваемыми по его второму входу. Частота сигналов от генератора и информационных сигналов из линии связи одинакова. Сигна- 20 лом с первого выхода приемника 1 устанавливается также начальное (нулевое) состояние счетчика 13 (адресов), а триггер 7 (выделения рабочего цикла) переводится в состояние " 1 " . 25 Сигнал от триггера 7 деблокирует работу первого распределителя 3, который после этого начинает воспринимать импульсные сигналы формирователя 27, образованные по спадам тактовых сигналов с первого вы- 30 хода генератора 2, С учетом того, что признаки передачи команд телеуправления и квитирования телесигналов следуют с разделением во времени вслед за синхронизирующей посылкой и предваряют передачу 35 информационных сигналов, распределитель 3 выделяет отдельные временные интервалы и формирует сигналы " 1 " на соответствующих выходах: на первом - для приема признака команды телеуправления; 40 на втором - для приема признака команды квитирования телесигналов, на третьем для приема информационного кода, содержащего собственно команды телеуправления или адреса квитируемого телесигнала. 45 В позиции " 1 " распределителя с его выхода подается сигнал стробирования на вход триггера 8, а в позиции "2" - на вход триггера 9, На информационные входы триггеров 8 и 9 подаются сигналы с второго 50 выхода приемника 1. Благодаря такому включению триггер 8 устанавливается в " 1 " при приеме команды телеуправления, а триггер 9 - при приеме команды квитирования телесигнала. Рабочие циклы, когда оба 5 триггера 8 и 9 остаются в "О", выделяются для передачи телесигналов (режим передачи телесигналов не рассматривается). Установка триггера 8 или 9 в " 1" означает необходимость ввода последовательного 10 информационного кода в блок 5 памяти. Для синхронизации вывода данных из приемника 1 и их ввода в блок 5 используется счетчик 13 (адресов принимаемых команд). Сигнал разрешения поступает с третьего выхода распределителя 3 на второй вход счетчика 13. ' Распределитель 3 должен удерживаться в позиции "3' на все время ввода информации в блок 5 памяти, для чего сигнал с третьего выхода подключается также к второму входу распределителя 3, который при этом теряет чувствительность к тактовым сигналам, подаваемым на его первый вход. Таковые сигналы поступают на первый, а сигнал установки начального (нулевого) состояния - на третий входы счетчика 13. Число основных разрядов счетчика 13 выбирают с учетом числа объектов телеуправления и телесигнализации. В данном варианте реализации устройства число объектов телеуправления и телесигнализации принято равным 64, т.е. число основных разрядов должно быть равным шести. Кроме того, для работы устройства требуется, кроме основных, также два дополнительных разряда. Сигналом " 1 " по первому (СЕ) входу счетчик переводится в режим счета тактовых сигналов, поступающих по второму (С) входу. Сигналом" 1" по третьему (R) входу счетчик устанавливается в "0". Кодовая комбинация сигналов на группе выходов счетчика 13 определяет адрес ячейки памяти блока Б. Блок 5 используется для последовательного ввода и вывода информационных сигналов. В рассматриваемом режиме ввода в ОЗУ информационных сигналов, выделенных блоком 1, информационные сигналы поступают на третий (информационный) вход блока 5 с выхода элемента И 30. повторяющего сигналы от приемника 1, так как на его второй вход подзн сигнал " 1 " с инверсного выхода триггера 12. Режим записи данных задается сигналом " 1 " по второму входу блока 5, который образуется на выходе элемента ИЛИ 25, на вход которого через элемент И 33 поступает сигнал "1" от элемента І/ІЛИ 22 (один из триггеров 8 или 9 - в состоянии "Г). Ввод сигналов в блок 5 стробируется сигналом, поступающим на его первый вход, причем для обеспечения устойчивой работы необходимо разделить по времени сигналы стробирования и изменения адресов ячеек памяти. Указанное разделение сигналов реализуется счетчиком 14, элементом ИЛИ 21 и коммутатором 15 следующим образом. Коммутатор 15 пропускает на выход сигналы с 1667137 первого или второго входа в зависимости от уровня сигнала управления на его третьем входе. В режиме записи информации в блок 5 сигнал управления от триггера 11 равен "О", поэтому коммутатор 15 пропускает на 5 выход сигналы с второго входа, т.е. с.третьего выхода генератора 2, соответствующего частоте передачи (и приема) информации по линии связи, Каждым прошедшим через коммутатор 15 сигналом счетчик ^устанав- 10 ливается в "О" и удерживается в этом состоянии до паузы между тактовыми импульсами, после чего счетчик 14 оказывается чувствительным к сигналам по первому входу, поступающим с второго выхода гене- 15 ратора 2. Частота этих сигналов выбирается значительно большей частоты передачи информации по линии связи. По первому сигналу, поступающему на тактовый (первый) вход счетчика 14 после снятия сигнала "1" с 20 его третьего входа, счетчик переводится в первую позицию, когда сигнал " 1" образуется на его первом выходе. При Зтом сигнал " 1 " от элемента ИЛИ 21 через элемент ИЛИ 23 поступает на вход стробирования блока 5, блокирует чувствительность блока и, та- 25 ким образом, разрешает смену сигналов - адресов на первой группе входов. С задержкой, равной одному периоду сигналов по первому выходу генератора 2, сигнал "1" устанавливается на втором выходе счет- 30 чика 14. При этом сигнал блокировки блока 5 удерживается, но также формируется сигнал " 1 " на втором входе счетчика 13. который переключается в следующую кодовую позицию, подготавливая стробирование 35 очередной ячейки блока 5. Кроме того, сигнал ''1" с второго выхода счетчика 14 подается на его второй вход, блокируя чувствительность счетчика к тактовым сигналам. Указанное состояние удерживается 40 до очередного фронта сигнала от коммутатора 15, т.е. от генератора 2. По указанному сигналу сигнал "1" на выходе элемента ИЛИ 21 исчезает, что обеспечивает управление ячейкой блока 5, адрес которой определяет- 45 ся кодом на выходе счетчика 13. В блок 5 вводится сигнал с выхода приемника 1, причем вводимый сигнал соответствует его выходному сигналу в момент перехода в "1" сигнала на выходе элемента ИЛИ 23, т.е. 50 ввод данных смещается относительно времени его передачи примерно на половину периода тактовой частоты передачи данных по линии связи и формируется в зоне наиболее достоверного приема. 55 Отмеченный режим записи данных в блок 5 продолжается до ввода в счетчик 13 шестидесяти четырех тактов, после чего по сигналу от инвертора 37 блокируется эле мент И 33 и исчезает сигнал " 1" от элемента ИЛИ 25, задающий режим записи данных. Блок 5 переводится в режим считывания данных, причем, так как кодовые комбинации на основных разрядах (на группе выходов) счетчика 13 начинают повторяться, сканируются те же ячейки блока 5, в которые в предшествующих шестидесяти четырех тактах записывались данные с выхода приемника 1. Очередные шестьдесят четыре такта используются для контроля достоверности принятой информации путем сравнения записанной основной последовательности с повторно передаваемой, инверсной по отношению к основной, Сравнение повторно принимаемых последовательных сигналов (проинвертированных инвертором 36)1 со считываемыми из блока 5 производится одпоразрядным компаратором 20, построенным на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ. Фиксация результатов сравнения сигналов смещается по отношению к фронтам сравниваемых сигналов и осуществляется триггером 10 по сигналам от формирователя 27. Элемент И 31 блокирует чувствительность триггера 10 к сигналам управления после его перевода в состояние " 1 " , что обеспечивает удержание зафиксированного сигнала несравнения до момента контроля результата, который проводится после завершения приема всей информационной посылки, т.е. в момент появления сигналов "1" на вторых выходах счетчика 13 и инвертора 37. По сигналу "1" на втором выходе счетчика 13 триггер 11 переводится в "1", если триггер 10 к этому моменту остался в состоянии "0". Чтобы исключить неоднозначность сигнала управления триггером 11 из-за того, что триггер 10 переводится в "0" сигналом от инвертора 37 а то же время, когда формируется сигнал управления триггером 11, между выходом триггера 10 и входом управления триггера 11 устанавливается элемент 40 задержки, реализованный, например, на интегрирующей RC-цепочке. Задержка должна компенсировать возможный сдвиг по времени моментов сброса в "0" триггера 10 и управления триггером 11. Установка триггера 11 в "Г означает, что основная и дополнительная информационные последовательности приняты от приемника 1 без ошибок и могут выполняться этапы дальнейшей обработки принятых команд, В противном случае сигнал от инвертора 38 разрешает работу формирователя 29 импульсов, импульс от которого через элемент ИЛИ 24 возвращает триггеры 7, 8 и 9 в "0". завершая рабочий 1667137 цикл без проведения других этапов обработки и выдачи принятой информации. Дальнейшая работа устройства определяется видом принятой команды. Если приняты команды управления объектами телеуправления, формируется сигнал " 1 " на выходе элемента И 32 и разрешается работа демультиплексора 16, управляющего перезаписью информации из блока 5 в блок 17 регистров. Для упрощения устройства принятые команды выводятся из блока 5 и вводятся в блок 17 регистров последовательно. При этом блок 17 представляет собой регистры сдвига с последовательным вводом и параллельным выводом информации и может быть реализован, например, на микросхемах 561 ИР2. Во время ввода и перемещения информации в регистрах его выходная информация недостоверна; поэтому, чтобы исключить влияние временной недостоверности информации на состояние реле выходного блока 19, блок регистров 1Т секционируется. Число регистров 17 в блоке может быть произвольным и должно быть выбрано с учетом общего числа объектов управления так, чтобы время перемещения информации было значительно меньше времени срабатывания и отпускания используемых реле. На первый вход (данных) всех регистров 17 подается информационный сигнал с выхода блока 5, а на второй - тактовые сигналы с выходов демультиплексора 16. Демультиплексор 16 обеспечивает разделение по времени управления каждым регистром 17. На его группу адресных входов поданы кодовые сигналы с четвертого - шестого выходов группы счетчика 13. На первый вход демультиплексорз 16 поданы тактирующие сигналы с выхода коммутатора 15, смещенные на половину периода инвертором 39, а на второй - разрешающий сигнал от элемента И 32. Демультиплексор 16 формирует импульсные сигналы, повторяющие сигналы инвертора 39, на одном из выходов, причем номер выхода определяется кодовыми сигналами на его адресных входах. 5 10 15 20 25 30 35 40 45 В данном варианте реализации устрой- 50 ства демультиплексор должен быть рассчитан на восемь выходов (по числу регистров 17). Число тактовых сигналов на каждом выходе демультиплексора 16 должно соответствовать числу ячеек в каждом регистре 17 55 и равно восьми в данном случае. Поэтому кодовые адресные сигналы демультиплексора 16 соединяются с четвертым - шестым выходами группы выходов счетчика 13, состояние которых изменяется при поступле 8 нии на вход счетчика 13 каждых восьми тактовых сигналов от коммутатора 15. Как видно, сигналы управления демультиплексором 16 и блоком 5 памяти объединены, что обеспечивает синхронное считывание данных из блока 5 и их занесение в регистры 17, Скорость перезаписи должна быть максимальной, чтобы избежать искажения команд, воспринимаемых реле блока 19. Эта скорость задается сигналами с третьего выхода генератора 2, которые в режиме перезаписи (сигнал "1" от триггера 11) проходят на выход коммутатора 15. С учетом описанного механизма управления счетчиком 14 и блоком 5 памяти необходимо, чтобы частота сигналов на третьем выходе генератора 2 была не менее чем в три раза ниже частоты сигналов на втором выходе генератора. Режим перезаписи принятых блоком 5 . команд телеуправления в регистры 17 завершается при вводе в счетчик 13 шестидесяти четырех тактовых сигналов, т.е. при появлении сигнала " 1 " на первом выходе счетчика 13 после установки "1" на выходе триггера 11. При этих условиях образуется импульс формирователем 28, которым триггер 11 возвращается в нулевое состояние. Импульсным сигналом формирователя 28 через элемент ИЛИ 24 возвращаются в нулевое состояние триггеры 7 и 8, завершая установленный рабочий цикл устройства. Рассмотрим режим обработки принятых команд квитирования телесигнализации. Каждая принятая команда означает, что ранее переданный аварийный телесигнал, например о нарушении шлейфа охранной сигнализации, воспринят на пункте приема. По команде квитирования вместо хранимого в блоке памяти аварийного телесигнала разрешается запись текущего состояния датчика телесигнала. Благодаря этому обеспечивается запоминание кратковременного аварийного телесигнала до получения подтверждения приема аварийного телесигнала. Используемый в устройстве алгоритм поочередного квитирования аварийных телесигналов позволяет избежать их потери при одновременном поступлении нескольких аварийных телесигналов. Для хранения телесигналов используется специальный блок 6 памяти, аналогичный по структуре блоку 5. Упрощение схемы устройства достигается тем, что для управления блоком 6 используются те же элементы, что и для блока 5. В частности, в блоках 5 и Є объединяются адресные шины и вход стробирования. На третий (информационный) вход блока 6 подается сигнал от преобразователя 42, поступающий от блока 41 1667137 10 датчиков телесигналов. На информационустанавливается всостояние, соответствуюные входы преобразователя подаются выщее сигналу от блока 5, по фронту сигнала ходные сигналы от блока 41, а на адресные нз втором выходе второго распределителя входы - кодовые сигналы от счетчика 13. На 4. Распределитель 4 воспринимает тактовыход преобразователя 42 проходит сигнал, 5 вые импульсы с второго выхода генератора соответствующий сигналу от блока 41, но2, если на его второй вход (установки нулемер которого определяется сигналами от вого состояния) не подан сигнал блокировки счетчика 13. Таким образом, сканирование от элемента И 35. В рассматриваемом режисигналов от датчиков синхронизировано ме на элемент И 35 от триггера 9 и коммутасчетчиком 13, причем этими же сигналами 10 тора 15 поданы сигналы " 1 " , поэтому на его от счетчика 13 определяются и адреса ячеек инверсном выходе присутствует сигнал "0", памяти блока 6. Сигнал " 1 " на выходе преразрешающий последовательное формирообразователя 42 и информационном входе вание сигналов " 1 " на первом, втором и блока 6 означает, что зафиксировано аватретьем выходах распределителя 4. рийное состояние датчика телесигнала. При 15 Если триггер 12 устанавливается в "1", этом через элемент ИЛИ 26 сигнал " 1" форэто означает разрешение квитирования темируется и на втором входе управления релесигнала. При этом сигнал с прямого выхожимом работы блока 6, который да триггера подается на элемент ИЛИ 26, переводится в режим записи. Аналогично устанавливающий режим записи для блока описанному для блока 5 в блок б записыва20 6. Сигнал с первого выхода распределителя ется аварийный телесигнал по адресу, зада4 через элемент И 34 подается на вход элеваемому счетчиком 13. Режим записи мента ИЛИ 23, в результате чего блок 6 устанавливается только при обнаружении кратковременно теряет чувствительность к аварийных телесигналов; при появлении на входным сигналам. Затем при появлении выходе преобразователя 42 сигнала "0", т.е. нормального значения телесигнала, сигна- 25 сигнала на втором выходе распределителя 4 и его исчезновении на первом, элемент ИЛИ лом "О" от элемента ИЛИ 26 блок 6 автома23 вновь формирует разрешающий сигнал и тически устанавливается в режим в блок 6 заносится сигнал, соответствующий считывания без разрушения информации, сигналу от преобразователя 42, т.е. в блок ранее записанной в блок 6. Таким образом, в рассматриваемом режиме в блок 6 зано- 30 по адресу выбранного телесигнала записывается текущее значение сигнала от датчисятся все вновь зафиксированные аварийка. Чтобы исключить повторное ные сигналы, сохраняются все ранее квитирование одного и того же сигнала и записанные и блокируется замещение аватаким образом, исключить пропуск вновь рийного сигнала нормальным даже если датчик из аварийного перешел в нормаль- 35 фиксируемого аварийного сигнала, одновременно с записью текущего значения теное состояние. Из блока 6 в рабочих циклах лесигнала в блок 6 гасится команда, передачи телесигналов, не рассматриваехранимая в блоке 5. Для этого с инверсного мых при описании работы устройства, телевыхода триггера 12 сигнал "0" подается на сигналы передаются на пункт приема, от которого по мере реакции оператора на ава- 40 вход элемента И 30, который формирует сигрийные телесигналы поступают команды нал "0" на информационном входе блока 5. квитирования телесигналов, разрешающие Так как блок 5 кратковременно сигналом от запись в блок 6 текущих значений сигналов элемента ИЛИ 23, восприняпшего сигнал от соответствующих датчиков. " 1 " от элемента И 34, переведен в режим 45 записи, в блок 5 по установленному счетчиком 13 адресу записывается сигнал "О". Этап квитирования телесигналов реалиПосле завершения управления блоками зуется следующим образом. Команда-адрес квитируемого сигнала занесена в блок 5, 5 и 6, т.е. при появлении сигнала "1" на признак приема команды квитирования - в втором выходе распределителя 4, по сіігнатриггер 9, а разрешение вывода команды - 50 лу от элемента ИЛИ 24 возвращаются в "0" в триггер 11. триггеры 7 и 9, завершая рабочий цикл приема и обработки команды квитирования теВ интервале времени, когда на выходе лесигнала. коммутатора 15 присутствует сигнал "0", т.е. во время импульса на третьем выходе генеБлагодаря предлагаемому выполнению ратора 2, на выходах элементов ИЛИ 23 и 55 устройства обеспечивается прием, обработИЛИ 25 - "0", а на выходе блока 5 - сигнал, ка и вывод команд телеуправления двух тисоответствующий принятой команде по адпов - для задания состояния объектов ресу, установленному на выходах счетчика управления и для квитирования телесигна13. Сигнал от блока 5 подан на второй (уплов, что повышает информативность предравляющий) вход триггера 12. Триггер 12 лагаемого устройства. Прием и обработка 11 1667137 всех команд проводятся с использованием общих блоков, т.е. улучшение технических характеристик устройства достигается без его существенного усложнения. Формула изобретения 5 Устройство для приема и обработки команд телеуправления, содержащее приемник, вход которого является входом устройства, первый и второй выходы приемника соединены соответственно с входом 10 генератора импульсов и через первый инвертор с первым входом первого компаратора, блок усилителей, выходы которого соединены с одноименными входами выходного блока, первый и второй счетчики, 15 первый выход второго счетчика соединен с первым входом первого элемента ИЛИ, второй - четвертый элементы ИЛИ, первый и второй элементы И, первые распределитель импульсов, триггер и блок памяти, преобра- 20 зователь параллельного кода в последовательный и элемент задержки, о т л и ч а ю щ е е с я тем, что, с целью повышения информативности устройства, в него введены блок датчиков, коммутатор, группа регистров сдвига, демультиплексер, 25 формирователи импульсов, второй распределитель импульсов, второй блок памяти, второй - шестой триггеры, третий - шестой элементы И, пятый и шестой элементы ИЛИ и второй - четвертый инверторы, первый 30 выход генератора импульсов соединен непосредственно с первым входом коммутатора и через первый формирователь импульсов с первыми входами первого распределителя импульсов и второго элемента 35 И, второй выход генератора импульсов соединен с первыми входами второго счетчика и второго распределителя импульсов, третий выход генератора импульсов соединен с вторым входом коммутатора, выход кото- 40 рого соединен через второй инвертор с первым входом демультиплексора и непосредственно с первым входом третьего элемента И и вторым входом второго счетчика, второй выход которого соединен с 45 первым входом первого счетчика, третьим входом второго счетчика и вторым входом первого элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом третьего элемента ИЛИ, выход которого со- 50 единен с первыми входами первого и второго блоков памяти, выход первого блока памяти соединен с первыми входами регистров сдвига группы и второго триггера и вторым входом компаратора, выход которо- 55 го соединен с первым входом третьего триггера, инверсный выход которого соединен через элемент задержки с входом третьего инвертора и первым входом четвертого 12 триггера и непосредственно с вторым входом второго элемента И, выход которого соединен с вторым входом третьего триггера, выход третьего инвертора соединен с первым входом второго формирователя импульсов, выход которого соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с первыми входами первого, пятого и шестоготриггеров, второй вход и инверсный выход первого триггера соединены соответственно с первым выходом приемника и вторым входом первого распределителя импульсов, первый и второй выходы которого соединены с вторыми входами соответственно пятого и шестого триггеров, третьи входы которых и первый вход первого элемента И подключены к второму выходу приемника, третий выход первого распределителя импульсов соединен со своим третьим входом и вторым входом первого счетчика, третий вход которого подключен к первому выходу приемника, выходы группы выходов первого счетчика соединены с соответствующими входами группы входов первого и второго блоков памяти, демультиплексора и преобразователя параллельного кода в последовательный, первый выход первого счетчика соединен непосредственно с первым входом третьего формирователя импульсов и через четвертый инвертор с третьим входом третьего триггера и первым входом четвертого элемента И, второй выход первого счетчика соединен с вторыми входами четвертого триггера и второго формирователя импульсов, выход третьего формирователя импульсов соединен с вторым входом четвертого элемента ИЛИ и третьим входом четвертого триггера, выход которого соединен с вторым входом третьего формирователя импульсов, третьим входом коммутатора и первым входом пятого элемента И, выход которого соединен с вторым входом демультиплексора, выходы которого соединены с вторыми входами одноименных регистров сдвига группы, выходы которых соединены с соответствующими входами блока усилителей, выход пятого триггера соединен с вторым входом пятого элемента И и с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого соединен с вторым входом первого блока памяти, выход шестого триггера соединен с вторыми входами второго элемента ИЛИ и третьего элемента И, инверсный выход которого соединен с вторым входом второго распределителя импульсов, первый выход которого соединен с вторым 13 1667137 первым входом шестого элемента ИЛИ, вывходом второго триггера и первым входом ход которого соединен с вторым входом втошестого элемента И, выход которого соедирого блока памяти, выходы блока датчиков нен с вторым входом третьего элемента соединены с соответствующими входами ИЛИ, второй выход второго распределителя преобразователя параллельного кода в поимпульсов соединен с третьими входами следовательный, выход которого соединен с четвертого элемента ИЛИ и второго триггевторым входом шестого элемента ИЛИ и ра, инверсный выход которого соединен с третьим входом второго блока памяти, вывторым входом первого элемента И, выход ход которого и выход выходного блока явкоторого соединен с третьим входом первосоответственно выходом го блока памяти, прямой выход второго 10 ляются сигнализации и выходом управления усттриггера соединен с вторыми входами шесройства. того элемента И и пятого элемента ИЛИ и Редактор А.Огар Составитель Н.Бочарова Техред М.Моргентал Корректор М.Кучерявая Заказ 2528 Тираж 324 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for telecontrol receipt and processing

Автори англійськоюPortnov Mykhailo Lvovych

Назва патенту російськоюУстройство для приема и обработки команд телеуправления

Автори російськоюПортнов Михаил Львович

МПК / Мітки

МПК: G08C 19/28

Мітки: обробки, пристрій, телеуправління, приймання, команд

Код посилання

<a href="https://ua.patents.su/8-1848-pristrijj-dlya-prijjmannya-i-obrobki-komand-teleupravlinnya.html" target="_blank" rel="follow" title="База патентів України">Пристрій для приймання і обробки команд телеуправління</a>

Попередній патент: Контрольований пункт системи телемеханіки

Наступний патент: Спосіб одержання диоксиду дінітрілу 2,4,6-триметилбензол-1,3-дікарбонової кислоти

Випадковий патент: Спосіб ранньої діагностики реактивного синовіту у хворих на остеоартроз