Пристрій для моделювання нейрона

Номер патенту: 52771

Опубліковано: 10.09.2010

Автори: Куперштейн Леонід Михайлович, Хаїмзон Ігор Ізєвич, Мартинюк Тетяна Борисівна, Сидорук Леся Володимирівна

Формула / Реферат

Пристрій для моделювання нейрона, який містить керовані резисторні елементи, блоки моделювання синапсів, які складаються з послідовно з'єднаних узгоджуючих підсилювачів, входи яких є входами блоків моделювання синапсів, накопичуючих елементів, елементів затримки, блоки моделювання дендритів, які складаються з суматорів, елементів затримки та інвертора, утворюючих прямий та зворотний ланцюги так, що елементи затримки і суматори по першому неінвертованому входу включені до них послідовно і чергуються між собою, причому зворотний ланцюг починається з суматора, а вихід його останнього елемента затримки з'єднаний через інвертор з входом першого елемента затримки прямого ланцюга, другі неінвертовані входи суматорів прямого ланцюга з'єднані з інвертованими входами суміжних з ними суматорів зворотного ланцюга і є входами блока моделювання дендриту, які з'єднані з виходами відповідної до нього групи блоків моделювання синапсів, вихід кожного елемента затримки прямого ланцюга з'єднаний з другим неінвертованим входом відповідного суматора зворотного ланцюга і є виходом блока моделювання дендриту і дендритним виходом пристрою, а вихід кожного елемента затримки зворотного ланцюга з'єднаний з третім неінвертованим входом відповідного суматора прямого ланцюга, прямий ланцюг закінчується елементом затримки, вихід якого є проксимальним виходом блока моделювання дендриту, формувач вихідних імпульсів, вихід якого є виходом пристрою, пристрій також містить блок синхронізації, входи якого з'єднані з виходом пристрою і його входами, а виходи за кількістю синапсів підключені до керуючих входів резисторних елементів, причому кожний блок моделювання дендриту містить додаткові елементи затримки за кількістю наявних у них елементів затримки без одного та двовхідні суматори, кожний додатковий елемент затримки підключений у розрив між наявним у прямому і зворотному ланцюгу послідовно підключеним з ним суматором, виходи двовхідних суматорів є дендритними виходами, перший вхід кожного суматора під'єднаний між виходом елемента затримки і входом додаткового елемента затримки прямого ланцюга, а другий вхід - між відповідними їм елементами затримки зворотного ланцюга, кількість двовхідних суматорів дорівнює кількості ділянок дендриту між синаптичними контактами, який відрізняється тим, що в нього введено перетворювачі напруги в код за кількістю блоків моделювання дендритів і адаптивний суматор, входи якого з'єднані з виходами перетворювачів напруги в код і який містить установний вхід та вхід керування пристрою, вихід адаптивного суматора з'єднаний з входом формувача вихідних імпульсів, крім того проксимальний вихід кожного блока моделювання дендриту з'єднаний з входом відповідного перетворювача напруги в код.

Текст

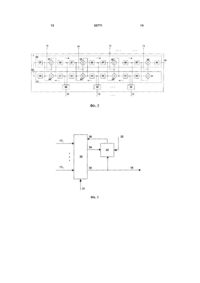

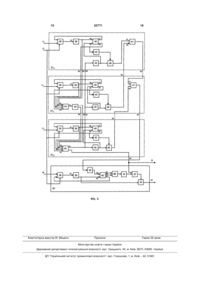

Пристрій для моделювання нейрона, який містить керовані резисторні елементи, блоки моделювання синапсів, які складаються з послідовно з'єднаних узгоджуючих підсилювачів, входи яких є входами блоків моделювання синапсів, накопичуючих елементів, елементів затримки, блоки моделювання дендритів, які складаються з суматорів, елементів затримки та інвертора, утворюючих прямий та зворотний ланцюги так, що елементи затримки і суматори по першому неінвертованому входу включені до них послідовно і чергуються між собою, причому зворотний ланцюг починається з суматора, а вихід його останнього елемента затримки з'єднаний через інвертор з входом першого елемента затримки прямого ланцюга, другі неінвертовані входи суматорів прямого ланцюга з'єднані з інвертованими входами суміжних з ними суматорів зворотного ланцюга і є входами блока моделювання дендриту, які з'єднані з виходами відповідної до нього групи блоків моделювання синапсів, вихід кожного елемента затримки прямого ланцюга з'єднаний з другим неінвертованим входом відповідного суматора зворотного ланцюга і є виходом блока моделювання дендриту і дендритним виходом пристрою, а вихід кожного елеме U 2 (11) 1 3 52771 4 рованого формувача, третій і четвертий суматори, одного та двовхідні суматори, кожний додатковий п'ятий суматор з двома входами, групу нелінійних елемент затримки підключений у розрив між наявелементів за кількістю збуджуючих і гальмівних ним у прямому та зворотному ланцюгу послідовно входів пристрою, які розділені і через відповідні підключеним з ним суматором, виходи двовхідних послідовні ланцюжки з'єднані з входами першого і суматорів є дендритними виходами, перший вхід другого суматорів, виходи яких з'єднані з входами кожного суматора під'єднаний між виходом елеметретього суматора, вихід якого з'єднаний з входанта затримки і входом додаткового елемента зами функціонального перетворювача і порогового тримки прямого ланцюга, а другий вхід - між відпоелемента, збуджуючі входи пристрою через відповідними йому елементами затримки зворотного відні послідовні ланцюжки з'єднані з входами неліланцюга, кількість двовхідних суматорів дорівнює нійних елементів, виходи яких з'єднані з входами кількості ділянок дендриту між синаптичними кончетвертого суматора, вихід якого з'єднаний з третактами. тім входом п'ятого суматора. Недоліком даного пристрою є складність його Недоліком даного пристрою є складність його структури, зокрема, порогового блока. структури. В основу корисної моделі поставлено задачу Найбільш близьким за технічною суттю є пристворення пристрою для моделювання нейрона, в стрій для моделювання нейрона (а.с. СРСР № якому за рахунок введення нового блока з розши1585811, кл. G06G7/60, 1990р., Бюл. №30), який реними функціональними можливостями та нових містить керовані резисторні елементи, блоки мозв'язків досягається спрощення структури приделювання синапсів, які складаються з послідовно строю. з'єднаних узгоджуючих підсилювачів, входи яких є Поставлена задача досягається тим, що у входами блоків моделювання синапсів, накопичупристрій для моделювання нейрона, який містить ючих елементів, елементів затримки, блоки модекеровані резисторні елементи, блоки моделюванлювання дендритів, які складаються з трьохвхідня синапсів, які складаються з послідовно з'єднаних суматорів, в подальшому суматорів, елементів них узгоджуючих підсилювачів, входи яких є вхозатримки і інвертора, утворюючих прямий та зводами блоків моделювання синапсів, накопичуючих ротний ланцюги так, що елементи затримки і суелементів, елементів затримки, блоки моделюматори по першому неінвертованому входу вклювання дендритів, які складаються з суматорів, чені до них послідовно і чергуються між собою, елементів затримки та інвертора, утворюючих причому зворотний ланцюг починається з суматопрямий та зворотний ланцюги так, що елементи ра, а вихід його останнього елемента затримки затримки і суматори по першому неінвертованому з'єднаний через інвертор з входом першого елевходу включені до них послідовно і чергуються між мента затримки прямого ланцюга, другі неінвертособою, причому зворотний ланцюг починається з вані входи суматорів прямого ланцюга з'єднані з суматора, а вихід його останнього елемента заінвертованими входами суміжних з ними суматорів тримки з'єднаний через інвертор з входом першого зворотного ланцюга і є входами блока моделюелемента затримки прямого ланцюга, другі неінвання дендриту, які з'єднані з виходами відповідвертовані входи суматорів прямого ланцюга з'єдної до нього групи блоків моделювання синапсів, нані з інвертованими входами суміжних з ними вихід кожного елемента затримки прямого ланцюсуматорів зворотного ланцюга і є входами блока га з'єднаний з другим неінвертованими входом моделювання дендриту, які з'єднані з виходами відповідного суматора зворотного ланцюга і є вивідповідної до нього групи блоків моделювання ходом блока моделювання дендриту і дендритним синапсів, вихід кожного елемента затримки прямовиходом пристрою, а вихід кожного елемента заго ланцюга з'єднаний з другим неінвертованими тримки зворотного ланцюга з'єднаний з третім неівходом відповідного суматора зворотного ланцюга нвертованим входом відповідного суматора пряі є виходом блока моделювання дендриту і дендмого ланцюга, прямий ланцюг закінчується ритним виходом пристрою, а вихід кожного елемеелементом затримки, вихід якого є проксимальним нта затримки зворотного ланцюга з'єднаний з тревиходом блока моделювання дендриту, адитивний тім неінвертованим входом відповідного суматора суматор, входи якого підключені до проксимальних прямого ланцюга, прямий ланцюг закінчується виходів блоків моделювання дендриту, пороговий елементом затримки, вихід якого є проксимальним блок, підключений на вихід адитивного суматора і виходом блока моделювання дендриту, формувач який складається з елемента порівняння, вхід яковихідних імпульсів, вихід якого є виходом приго є входом порогового блока, блока формування строю, пристрій також містить блок синхронізації, порогу, вихід якого підключений на другий вхід входи якого з'єднані з виходом пристрою і його елемента порівняння, формувача вихідних імпульвходами, а виходи за кількістю синапсів підключені сів, підключеного до виходу елемента порівняння, до керуючих входів резисторних елементів, приблока зворотного зв'язку, вихід якого підключений чому кожний блок моделювання дендриту містить до входу блока формування порогу, а вхід з'єднадодаткові елементи затримки за кількістю наявних ний з виходом пристрою, яким є вихід формувача у них елементів затримки без одного та двовхідні вихідних імпульсів, пристрій також містить блок суматори, кожний додатковий елемент затримки синхронізації, входи якого з'єднані з виходом припідключений у розрив між наявним у прямому і строю і його входами, а виходи за кількістю синапзворотному ланцюгу послідовно підключеним з сів підключені до керуючих входів резисторних ним суматором, виходи двовхідних суматорів є елементів, причому кожний блок моделювання дендритними виходами, перший вхід кожного судендриту містить додаткові елементи затримки за матора під'єднаний між виходом елемента затрикількістю наявних у них елементів затримки без мки і входом додаткового елемента затримки пря 5 52771 6 мого ланцюга, а другий вхід - між відповідними їм верту 31 групу елементів затримки. Суматори 22 елементами затримки зворотного ланцюга, кільпершої групи, елементи 26 першої та елементи 27 кість двовхідних суматорів дорівнює кількості ділядругої груп елементів затримки складають прямий нок дендриту між синаптичними контактами, ввеланцюг 23, а суматори 24 другої групи, елементи дено перетворювачі напруги в код за кількістю 30 третьої та елементи 31 четвертої груп елеменблоків моделювання дендритів і адаптивний суматів затримки складають зворотний ланцюг 25 блотор, входи якого з'єднані з виходами перетворюка 7 моделювання дендриту. вачів напруги в код і який містить установний вхід Збуджуючі входи 13 з'єднані з першим входом та вхід керування пристрою, вихід адаптивного непарних суматорів 22 першої групи, вихід яких суматора з'єднаний з входом формувача вихідних з'єднаний з входом елементів 26 затримки першої імпульсів, крім того проксимальний вихід кожного групи. Вихід елементів 26 затримки першої групи блока моделювання дендриту з'єднаний з входом з'єднаний з входом елементів 27 затримки другої відповідного перетворювача напруги в код. групи, вихід яких з'єднаний з другим входом сумаНа фіг.1 представлена функціональна схема торів 22 першої групи, перший вхід парних сумазапропонованого пристрою для моделювання торів 22 першої групи з'єднаний з гальмівними нейрона; на фіг.2 - функціональна схема блока входами 14, а вихід останнього елемента 26 замоделювання дендриту, на фіг.3 - структурна схетримки першої групи є проксимальним виходом 16 ма адаптивного суматора, на фіг.4 - функціональблока 7 моделювання дендриту. на схема алгебраїчного суматора. Гальмівні входи 14 з'єднані з першим входом Пристрій для моделювання нейрона (фіг.1) мінепарних суматорів 24 другої групи, вихід яких стить керовані резисторні елементи 1, блоки 2 і 3 з'єднаний з входом елементів 30 затримки третьої моделювання збуджуючих і гальмівних синапсів групи. Вихід елементів 30 затримки третьої групи відповідно, кожен з яких складається з узгоджуюз'єднаний з першим входом групи двовхідних сучого підсилювача 4, накопичувального елемента 5 маторів 28, виходи яких є дендритними виходами і елемента 6 синаптичної затримки, блоки 7 моде15 пристрою. Вихід елементів 30 затримки третьої лювання дендритів, перетворювачі 8 напруги в групи з'єднаний з входом елементів 31 затримки код, адаптивний суматор 9, формувач 10 вихідних четвертої групи, вихід яких з'єднаний з третім вхоімпульсів, а також блок 11 синхронізації. Збуджуюдом суматорів 24 другої групи, перший вхід парних чі та гальмівні входи 12 пристрою з'єднані з вхосуматорів 24 другої групи з'єднаний зі збуджуючим дами керованих резисторних елементів 1, кожний входом 13. Вихід суматорів 24 другої групи з'єдназбуджуючий вихід яких з'єднаний з входом відпоний з входом елементів 30 затримки третьої групи, відного блока 2 моделювання збуджуючих синапа вихід останнього елемента 30 затримки третьої сів, який є входом узгоджуючого підсилювача 4. групи з'єднаний з входом інвертора 29. Вихід інВихід узгоджуючого підсилювача 4 з'єднаний з вертора 29 з'єднаний з входом елемента 27 завходом накопичувального елемента 5, вихід якого тримки другої групи, вихід якого з'єднаний з другим з'єднаний з входом елемента 6 синаптичної завходом суматора 22 першої групи. Вихід елементів тримки, вихід якого з'єднаний зі збуджуючим вхо31 затримки четвертої групи з'єднаний з третім дом 13 відповідного блока 7 моделювання дендвходом суматорів 22 першої групи. Вихід елеменриту. Кожний гальмівний вихід керованих тів 26 затримки першої групи з'єднаний з другим резисторних елементів 1 з'єднаний з входом відвходом відповідного двовхідного суматора 28 груповідного блока 3 моделювання гальмівних синаппи. сів, який є входом узгоджуючого підсилювача 4. Адаптивний суматор 9 (фіг.3) містить алгебраВихід узгоджуючого підсилювача 4 з'єднаний з їчний суматор 32 і блок 33 формування порогу, входом накопичувального елемента 5, інверсний причому алгебраїчний суматор 32 має інформавихід якого з'єднаний з входом елемента 6 синапційні входи 171,..,17n, а його виходи 34 і 35 з'єднані тичної затримки, вихід якого з'єднаний з гальмівз відповідними входами блока 33 формування поним входом 14 відповідного блока 7 моделювання рогу, вихід якого з'єднаний з входом 36 порогу алдендриту. Блоки 7 моделювання дендритів мають гебраїчного суматора 32. Вихід 35 алгебраїчного дендритні виходи 15 і проксимальний вихід 16, суматора 32 є виходом 18 адаптивного суматора який з'єднаний з входом відповідного перетворю9, а установний вхід 20 і вхід 21 керування привача 8 напруги в код, вихід якого з'єднаний з відстрою з'єднані з відповідними входами блока 33 повідним входом 17і (і=1,..,n) адаптивного суматоформування порогу і алгебраїчного суматора 32. ра 9. Вихід 18 адаптивного суматора 9 з'єднаний з Алгебраїчний суматор 32 (фіг. 4) містить n ковходом формувача 10 вихідних імпульсів, вихід 19 мірок 37, причому і - та комірка 37 містить мультиякого є інформаційним виходом пристрою, а також плексор 38, регістр 39, суматор - віднімач 40, суз'єднаний з входом блока 11 синхронізації, виходи матор 41, D - тригер 42, мініматор 43, два регістри якого з'єднані з керуючими входами керованих 44, 45, комутатор 46. Перший інформаційний вхід резисторних елементів 1, а його входи з'єднані мультиплексора 38 з'єднаний з входом 17i і-ої котакож з входами пристрою. Адаптивний суматор 9 мірки 37, керувальний вхід з'єднаний з входом 21 має установний вхід 20 і вхід 21 керування прикерування пристрою, а його вихід підключено до строю. входу 47 регістра 39, в якого вихід з'єднаний з Блок 7 моделювання дендриту (фіг. 2) містить прямим входом 48 суматора - віднімача 40 та інпершу групу суматорів 22, прямий ланцюг 23, друформаційним входом 49 мініматора43. гу групу суматорів 24, зворотний ланцюг 25, першу В і-й комірці 37 вихід регістра 45 з'єднаний з 26 і другу 27 групи елементів затримки, групу двопершим (інформаційним) входом комутатора 46 та вхідних суматорів 28, інвертор 29, третю 30 і четінверсним входом 50 суматора - віднімача 40, ви 7 52771 8 хід 51 якого з'єднаний з другим інформаційним блоків 2 і блоків 3 моделювання збуджуючих і гавходом мультиплексора 38, а вихід 52 знака сумальмівних синапсів відповідно, де через узгоджуючі тора - віднімача 40 з'єднаний зі знаковим входом підсилювачі 4 подаються на накопичуючі елементи 53 мі-німатора 43 і D - входом D - тригера 42, інве5, при цьому змінюють форму, тривалість і знак рсний вихід якого з'єднаний з другим (керуваль(збуджуючий або гальмівний синапс) і перетворюним) входом комутатора 46. Вихід комутатора 46 ються в локальні постсинаптичні потенціали підключено до виходу 54 і-ої комірки 37, крім того, (ЛПСП). Далі вони затримуються на час синаптичінформаційний вхід 55 мініматора 43 і-ої комірки ної затримки в елементах 6 і надходять на збу37 з'єднаний з виходом 56 (і-1) - ої комірки 37, вхід джуючі 13 і гальмівні 14 входи відповідних блоків 7 57 суматора 41 і -ї комірки 37 з'єднаний з виходом моделювання дендритів у відповідності з розташу58 (і-1) - ої комірки 37, а вхід 59 підключено до виванням синапсів на кожному реальному дендриті. ходу 54 (і+1) - ої комірки 37. Сигнал з проксимального виходу 16 кожного блока В і-й комірці 37 вхід регістра 45 підключено до 7 моделювання дендриту подається на перетвовходу 60 цієї комірки 37, вихід 61 мініматора 43 рювач 8 напруги в код, з виходу якого далі подаз'єднаний з входом регістра 44 цієї комірки, інфоється на відповідний вхід 17і (і=1,..,n) адаптивного рмаційний вихід якого є виходом 56 і-ої комірки 37, суматора 9, де відбувається їх порогове підсумоа його вихід знака є виходом 62 і-ої комірки 37, вування. Сумарний сигнал з виходу 18 адаптивноякий з'єднаний зі знаковим входом 63 мініматора го суматора 9 надходить на вхід формувача 10 43 (і+1) - ої комірки 37, а вихід 61 мініматора 43 nвихідних імпульсів, вихідний сигнал якого надхоої комірки 37 підключений до входів 60 всіх (n-1) дить на вихід 19 пристрою, а також на вхід блока молодших комірок 37. 11 синхронізації разом з вхідними сигналами приУ першій комірці 37 вихід регістра 39 є вихострою, які надходять на відповідні входи цього дом 56 першої комірки 37, вихід 52 знака суматора блока. В залежності від співвідношення цих сигна- віднімача 40 є її виходом 62, а вхід 57 суматора лів з блока 11 синхронізації надходять керуючі 41 з'єднаний з виходом комутатора 46 цієї ж комірсигнали, які змінюють опір відповідних керованих ки 37. Вихід 61 мініматора 43 n-ої комірки 37 з'єдрезисторних елементів 1. наний з входом регістра 45 цієї комірки, а його Блок 7 моделювання дендриту (фіг. 2) працює вихід ознаки нуля є виходом 64 n-ої комірки 37. в такий спосіб. Блок 65 порогового оброблення містить мульСигнали ЛПСП в кожному блоці 7 моделювантиплексор 38, регістр 39, суматор - віднімач 40, D ня дендриту з його збуджуючих 13 і гальмівних 14 тригер 42, регістр 45, елементи АБО 66 і І 67, ковходів надходять на неінвертуючі входи першої мутатор 68. Перший інформаційний вхід мультипгрупи 22 та інвертуючі входи другої групи 24 сумалексора 38 блока 65 порогового оброблення з'єдторів цього блока. В кожному суматорі при цьому наний з входом 36 порогу, керувальний вхід відбувається підсумовування ЛПСП з хвилею поз'єднаний з входом 21 керування пристрою, а його тенціалу, який розповсюджується вздовж прямого вихід підключено до входу 47 регістра 39, вихід ланцюга 23 до проксимального виходу 16. Через якого з'єднаний з прямим входом 48 суматора час τ відносно ЛПСП кожного синапсу з виходу віднімача 40 блока 65 порогового оброблення, блоків 2 або 3 моделювання збуджуючих і гальмівихід 51 якого з'єднаний з другим інформаційним вних синапсів, які надходять з входів 13 і 14 на входом мультиплексора 38 блока 65 порогового суматори 22 і 24 блока 7 моделювання дендриту, в оброблення. Вихід 58 (n-1) - ї комірки 37 з'єднаний кожному з них відбувається алгебраїчне підсумоз інформаційним входом регістра 45 блока 65 повування прямої та зворотної хвилі, причому вкларогового оброблення, його вихід з'єднаний з інвердення цих хвиль у результуючий сигнал на виході сним входом 50 суматора - віднімача 40 блока 65 кожного з суматорів 22 і 24 від найближчого до порогового оброблення, вихід 52 знака якого з'єднього по обидві сторони вздовж дендриту синапсів наний з першим входом елемента АБО 66, а вихід визначаються відношенням постійних часових за69 ознаки нуля з'єднаний з другим входом елеметримок 1 і 2 елементів 26, 27, 30, 31 затримки нта АБО 66. Вихід елемента АБО 66 з'єднаний 3D ( 26= 31= 1; 27= 30= 2) і коефіцієнтів передачі К1 і К2 - входом D - тригера 42 блока 65 порогового оброцих елементів (К26=К31=К1; К27=К30=К2). блення, прямий вихід якого з'єднаний з першим Співвідношення цих величин визначає половходом елемента І 67 блока 65 порогового обробження місця відведення внутрішньодендритного лення, другий вхід якого з'єднаний з виходом 64 nпотенціалу в проміжку між сусідніми входами 13 і ої комірки 37, а його вихід підключений до керува14 синапсів і може розташовуватись у будь якому льного входу комутатора 68. Інформаційний вхід місці цієї ділянки, що дозволяє точно відобразити комутатора 68 блока 65 порогового оброблення морфологію реальних міждендритних зв'язків нейз'єднаний з виходом регістра 39 блока 65 порогоронів з розвинутим дендритом. У результаті цього вого оброблення, його вихід є виходом 35 алгебсигнали на дендритних виходах 15, враховуючи раїчного суматора, а вихід 64 n-ої комірки 37 є дію оберненої хвилі, запізнюються відносно ЛПСП виходом 34 алгебраїчного суматора. на час відстані від входів 13 і 14 синапсів до дендПристрій для моделювання нейрона (фіг.1) ритного виходу 15 і відрізняються амплітудою від працює таким чином. ЛПСП в залежності від величини затухання при Вхідні сигнали у вигляді спайкової послідовнорусі хвилі потенціалу до дендритного виходу 15. сті подаються зі входів 12 пристрою на входи кеСуть роботи адаптивного суматора 9 (фіг.3) рованих резисторних елементів 1, де масштабуполягає в тому, що порогове оброблення n чисел ються за амплітудою у відповідності з вагою зводиться до обчислення і підсумовування N частсинаптичного контакту, далі надходять на входи кових сум Sj, де N - кількість різноманітних вхідних 9 величин аі,0, порівняння цих сум з порогом рмування вихідних даних вигляду: 52771 10 урахуванням сигналів на вході 21 керування приі фострою. Сумарний сигнал з виходу 35 алгебраїчного суматора 32 надходить на відповідний вхід блоn N N ка 33 формування порогу, на інший вхід якого S , якщо S a i,0 Sj q jd j , , (1) Y надходить керуючий сигнал з виходу 34 алгебраїi 1 j 1 j 1 0 у протилежно му випадку , чного суматора 32. На установний вхід 20 блока 33 формування порогу подаються установні дані, що де Y - результат оброблення пристрою; qj - зазадають початкове значення порогу підсумовувангальна значуща частина доданків (мінімальний ня в алгебраїчному суматорі 32, а сигнал з виходу елемент) j-го етапу; dj - кратність загальної части35 алгебраїчного суматора 32 є вихідним сигналом ни qj на j-му етапі; - значення порогу обробленна виході 18 адаптивного суматора 9. ня, j - етап оброблення. Алгебраїчний суматор 32 (фіг.4) працює таким Процес порогового оброблення в адаптивному чином. суматорі 9 має такий вигляд. На вхід 17i і-ої комірки 37 надходить і-й опеСпочатку визначається загальна значуща часранд аі,0 з групи операндів, кількість яких n. Запис тина qj всіх доданків на j-му етапі оброблення, операндів в комірки 37 виконується паралельно за тобто: наявністю одиничного сигналу на вході 21 керу(2) q j min a i, j 1 n , j 1 N , , вання пристрою. Через мультиплексор 38 і - й i 1 операнд аі,0 надходить на вхід 47 регістра 39 і-ої де аі,0 - і-й доданок на вході 17i адаптивного комірки 37. суматора 9, і перевіряється умова: Одночасно на вхід 36 порогу подають зовнішqj=0. (3) Якщо умова (3) виконується, то процес обробній поріг , який через мультиплексор 38 блока 65 порогового оброблення надходить по входу 47 в лення припиняється. У протилежному випадку виділяється різницевий зріз Aj, тобто сукупність регістр 39 цього блока. Після цього виконується послідовне виділення загальної (мінімальної знавеличин різниці всіх доданків j-го етапу з їхньою загальною частиною qj тобто: чущої) частини двох операндів - (і-1) - го та і-го мініматором 43 і запис результату в регістр 44 і-ої n n , (4) Aj a i, j a i, j 1 q j i 1 i 1 комірки 37 з виходу 61 мініматора 43. Згідно з виВ подальшому отриманий різницевий зріз Aj є разом (2) ця операція виконується послідовно, вхідною множиною доданків для наступного (j+1) починаючи з другої комірки 37. Кінцевий результат го етапу оброблення. q1 виділення загальної частини всіх n операндів на Далі формується часткова сума Sj як кратне першому етапі формується в n-ій комірці 37 і з загальної частини qj, де кратність dj визначається виходу 61 мініматора 43 цієї комірки 37 записуєтькількістю додатних доданків j-го етапу: ся в регістри 45 всіх n комірок 37 паралельно по їх Sj=qjdj. (5) входу 60. Після сформування часткової суми S1 за форПісля цього в і-й комірці 37 відбувається порімулою (5) на першому етапі формується різниця вняння в суматорі - віднімачі 40 і-го операнда аі,0, між заданим порогом та частковою сумою S1, що надходить з регістра 39 на його прямий вхід 48, отриманою на цьому етапі, тобто: та загальної частини q1 всіх операндів, що надхо(6) ∆1= -S1 дить з регістра 45 на його інверсний вхід 50. Поріперевіряється умова вняння відбувається в процесі віднімання від ве∆1≤0 (7) личини операнда загальної частини всіх величин і в разі її виконання перевіряється виконання операндів згідно з виразом (4) і ця різниця записуумови (3). Якщо обидві умови виконуються, то фоється з виходу 51 суматора - віднімача 40 через рмується відповідний результат Y пристрою (1) і мультиплексор 38 в регістр 39 по його входу 47 за порогове оброблення припиняється. Якщо умова наявністю нульового сигналу на вході 21 керуван(3) не виконується, то процес порогового обробня пристрою. При цьому на виході 52 знака сумалення продовжується і в подальшому поточна різтора - віднімача 40 формується знак різниці. Пениця ∆j-1 є поточним значенням порогу на наступред початком роботи регістри 39, 44, 45 і тригер 42 ному j-му етапі оброблення, тобто всіх комірок 37 і блока 65 порогового оброблення ∆j=∆j-1-S1. (8) занулені. На j-му етапі перевіряється умова При відсутності одиничного сигналу знака ві∆j≤0. (9) д'ємного результату одиничний сигнал з інверсноПроцес порогового оброблення повторюється го виходу D - тригера 42 подається на керувальдо визначення нульової величини qj (3). Виконання ний вхід комутатора 46 і дозволяє проходження в умови (3) свідчить про закінчення процесу і про і-й комірці 37 через комутатор 46 загальної частиформування остаточного результату Y порогового ни q1 операндів з регістра 45 через вихід 54 цієї оброблення (1) на виході 18 адаптивного суматора комірки 37 на вхід 59 суматора 41(і-1) - ої комірки 9. 37, де відбувається накопичування загальної часАдаптивний суматор 9 (фіг. 3) працює таким тини операндів. У випадку, якщо на виході 52 значином. ка суматора - віднімача 40 і-ої комірки 37 з'явиться Вхідні сигнали у вигляді кодів подаються на віодиничний сигнал знака від'ємного результату, то дповідні входи 171,..,17n алгебраїчного суматора наявність нульового сигналу на інверсному виході 32, на вхід 36 якого з виходу блока 33 формування D - тригера 42, а отже, на керувальному вході копорогу подається поточний поріг. В алгебраїчному мутатора 46 заборонить надходження загальної суматорі 32 здійснюється порогове підсумування з частини q1 операндів на даному етапі оброблення 11 52771 12 через комутатор 46 на вхід 59 суматора 41 (і-1) - ої В подальшому процес порогового оброблення комірки 37. виконується аналогічно першому етапу обробленВ суматорі 41 кожної комірки 37, крім n-ої, відня згідно з формулами (2) - (5) та (8), (9) і припибувається послідовне підсумовування загальних няється тоді, коли загальна значуща частина всіх частин q1 групи з n операндів, в результаті чого на поточних доданків на j-му етапі дорівнює нулю за виході суматора 41 (n-1) - ої комірки 37, тобто на виразом (3), а саме, коли присутній одиничний виході 58 цієї комірки 37 формується часткова сусигнал на виході 64 n-ої комірки 37, тобто на вихома S1 операндів згідно з виразом (5), яка записуді ознаки нуля мініматора 43 цієї комірки 37. При ється в регістр 45 блока 65 порогового обробленвиконанні умови (3) після виконання N етапів обня. Після цього відбувається порівняння в суматорі роблення у регістрі 39 блока 67 порогового оброб- віднімачі 40 блока 65 порогового оброблення лення формується результат | -S| оброблення, зовнішнього порогу , що надходить по його пряякий з'являється на виході 35 алгебраїчного сумамому входу 48 з регістра 39, та часткової суми S1, тора, тільки коли на обидва входи елемента І 67 що надходить по його інверсному входу 50 з вихонадходять одиничні сигнали, які формують одиниду регістра 45. Порівняння відбувається в процесі чний сигнал на керувальному вході комутатора 68 віднімання на першому етапі оброблення від зовблока 65 порогового оброблення. В іншому випадку на виході комутатора 68, тобто на вході 35 алнішнього порогу часткової суми S1 згідно з вирагебраїчного суматора присутній нульовий сигнал, зом (6). Різниця ∆1, записується з виходу 51 сумащо відповідає виразу (1). тора - віднімача 40 блока 65 порогового Запропонований пристрій для моделювання оброблення через мультиплексор 38 у регістр 39 нейрона має спрощену структуру завдяки тому, що по його входу 49 за наявністю нульового сигналу у нього введено адаптивний суматор, який має на вході 21 керування пристрою. розширені функціональні можливості, а саме, моСигнали з виходу 52 знака і виходу 69 ознаки жливість одночасно з підсумовуванням формувати нуля суматора - віднімача 40 блока 65 порогового результат порогового оброблення певної залежоброблення подаються через елемент АБО 66 на ності, що дозволяє відмовитись від адитивного D - вхід D - тригера 42 блока 65 порогового обробсуматора і порогового блока. лення. При цьому при наявності одиничного сигналу на одному з виходів: виході 52 знака або виході 69 ознаки нуля суматора - віднімана 40 одиничний сигнал з прямого виходу D – тригера 42 подається на один з входів елемента І 67. 13 52771 14 15 Комп’ютерна верстка М. Мацело 52771 Підписне 16 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for neuron simulation

Автори англійськоюMartyniuk Tetiana Borysivna, Khaimzon Ihor Izevych, Kupershtein Leonid Mykhailovych, Sydoruk Lesia Volodymyrivna

Назва патенту російськоюУстройство для моделирования нейрона

Автори російськоюМартынюк Татьяна Борисовна, Хаимзон Игорь Изевич, Куперштейн Леонид Михайлович, Сидорук Леся Владимировна

МПК / Мітки

МПК: G06G 7/60

Мітки: пристрій, моделювання, нейрона

Код посилання

<a href="https://ua.patents.su/8-52771-pristrijj-dlya-modelyuvannya-nejjrona.html" target="_blank" rel="follow" title="База патентів України">Пристрій для моделювання нейрона</a>

Попередній патент: Двотактний симетричний підсилювач струму

Наступний патент: Спосіб діагностики стану шийки матки

Випадковий патент: Роторний двигун внутрішнього згорання