Логічний елемент

Номер патенту: 101020

Опубліковано: 25.08.2015

Автори: Кичак Василь Мартинович, Стронський Віктор Володимирович

Формула / Реферат

Логічний елемент, що містить джерело постійної напруги, перший, другий входи, вихід пристрою, вхідний двоемітерний транзистор, перший, другий вхідні діоди, перший проміжний транзистор, транзистор першого фазорозподільчого каскаду, перший, другий вхідні транзистори, проміжний і вихідний діоди, перший вхідний резистор, перший, другий резистори першого фазорозподільчого каскаду, проміжний резистор, вихідний резистор, перший і другий вихідні транзистори, причому база вхідного двоемітерного транзистора через перший вхідний резистор підключена до додатного полюса джерела постійної напруги, перший емітер з'єднаний з катодом першого вхідного діода, анод якого підключений до загальної шини джерела постійної напруги, другий емітер з'єднаний з катодом проміжного діода і катодом другого вхідного діода, анод якого підключений до загальної шини джерела постійної напруги, колектор з'єднаний з базою транзистора першого фазорозподільчого каскаду, емітер якого через другий резистор першого фазорозподільчого каскаду підключений до загальної шини джерела постійної напруги і з'єднаний з базою другого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор підключений до виходу пристрою і з'єднаний з катодом вихідного діода, анод якого з'єднаний з емітером першого вихідного транзистора, колектор якого через вихідний резистор підключено до додатного полюса джерела постійної напруги, а база з'єднана з анодом проміжного діода і колектором транзистора першого фазорозподільчого каскаду та через перший резистор першого фазорозподільчого каскаду підключений до додатного полюса джерела постійної напруги, а також емітер першого проміжного транзистора підключений до загальної шини джерела постійної напруги, база з'єднана з першим входом проміжного резистора, який відрізняється тим, що в нього введено вхідний транзистор, перший, другий транзистори інвертуючого каскаду, транзистор другого фазорозподільчого каскаду, третій вихідний транзистор, другий вхідний резистор, перший, другий резистори інвертуючого каскаду, резистор другого фазорозподільчого каскаду, причому другий вивід першого проміжного резистора підключений до першого ходу пристрою і з'єднаний з емітером вхідного транзистора, катодом першого вхідного діода і катодом проміжного діода, анод якого підключений через резистор другого фазорозподільчого каскаду до додатного полюса джерела постійної напруги і з'єднаний з базою третього вихідного транзистора, колектор якого через вихідний транзистор підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з емітером першого вихідного транзистора і анодом вихідного діода, а також анод проміжного діода з'єднаний з колектором транзистора другого фазорозподільчого каскаду, емітер якого з'єднаний з емітером транзистора першого фазорозподільчого каскаду, базою другого вихідного транзистора і через другий резистор першого фазорозподільчого каскаду підключений до загальної шини джерела постійної напруги, база транзистора другого фазорозподільчого каскаду через другий резистор інвертуючого каскаду підключена до додатного полюса джерела постійної напруги і з'єднана з колекторами першого і другого транзисторів інвертуючого каскаду, емітер другого транзистора інвертуючого каскаду підключений до загальної шини джерела постійної напруги, база через перший резистор інвертуючого каскаду підключена до загальної шини джерела постійної напруги і з'єднана з емітером першого транзистора інвертуючого каскаду, база якого з'єднана з колектором вхідного двоемітерного транзистора, а колектор вхідного транзистора з'єднаний з базою транзистора першого фазорозподільчого каскаду, база через другий вхідний резистор підключена до додатного полюса джерела постійної напруги.

Текст

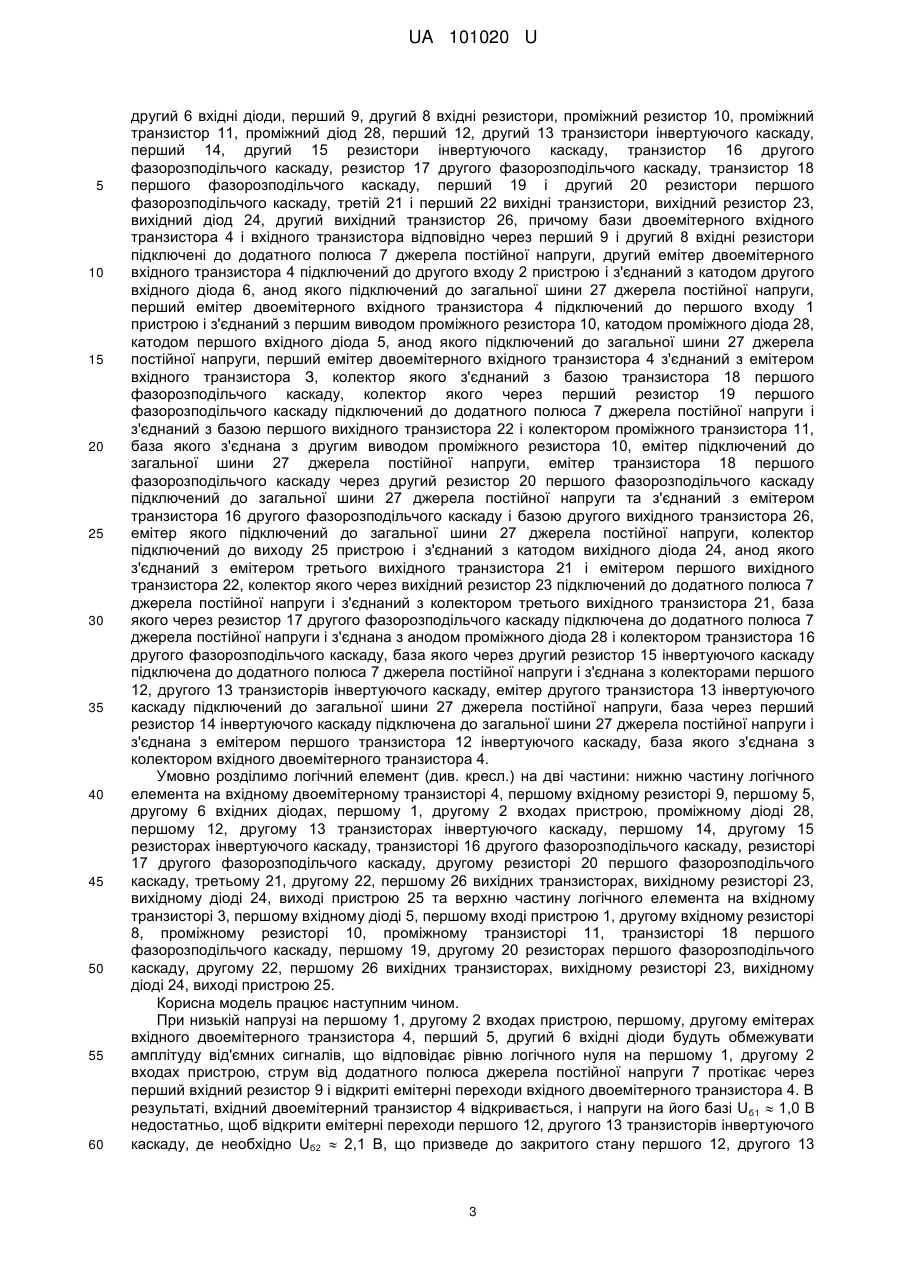

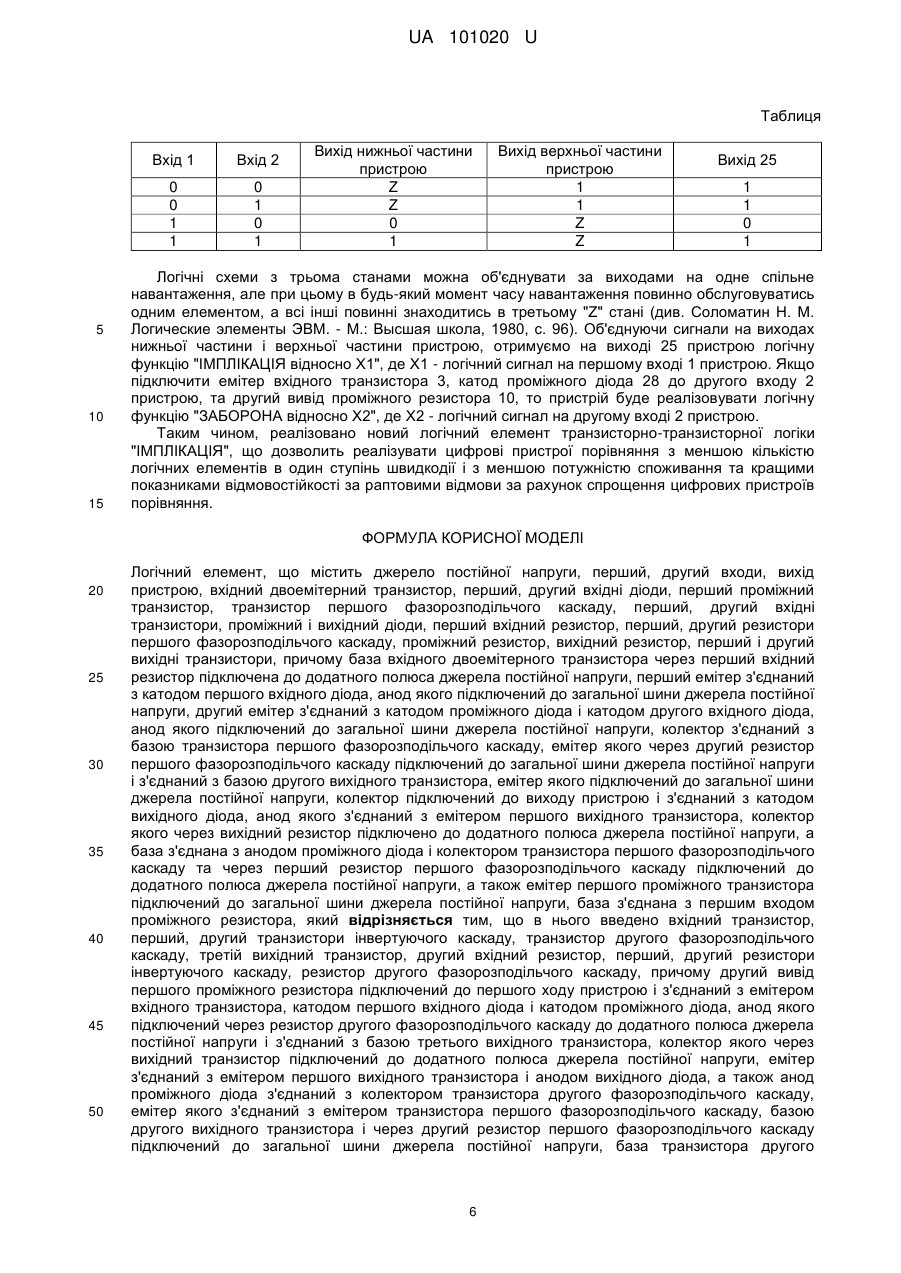

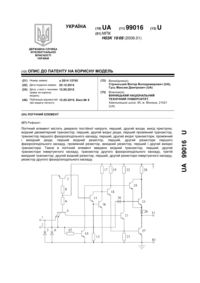

Реферат: UA 101020 U UA 101020 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до галузі мікроелектроніки і обчислювальної техніки та призначена для побудови цифрових пристроїв порівняння. Відомим аналогом є неінвертуючий вентиль містить звичайний інвертуючий вентиль, до якого доданий інвертуючий каскад за схемою Дарлінгтона і в підсумку пристрій виконує логічну операцію І-НІ-НІ, містить джерело постійної напруги та має перший, другий входи, вихід та складається з вхідного резистора, вхідного двоемітерного транзистора, першого, другого транзисторів інвертуючого каскаду, першого, другого резисторів інвертуючого каскаду, транзистора фазорозподільчого каскаду, першого, другого резисторів фазорозподільчого каскаду, першого, другого, третього вихідних транзисторів, вихідного резистора, першого, другого додаткових вихідних резисторів, причому перший, другий емітери вхідного двоемітерного транзистора підключені до першого, другого входів пристрою, база через вхідний резистор підключена до додатного полюса джерела постійної напруги, колектор з'єднаний з базою першого транзистора інвертуючого каскаду, емітер якого через перший резистор інвертуючого каскаду підключений до загальної шини джерела постійної напруги і з'єднаний з базою другого транзистора інвертуючого каскаду, емітер якого підключений до загальної шини джерела постійної напруги, колектор через другий резистор інвертуючого каскаду підключений до додатного полюса джерела постійної напруги та з'єднаний з колектором першого транзистора інвертуючого каскаду і базою транзистора фазорозподільчого каскаду, емітер якого через другий резистор фазорозподільчого каскаду підключений до загальної шини джерела постійної напруги і з'єднаний з базою другого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор через другий додатковий вихідний резистор з'єднаний з емітером транзистора фазорозподільчого каскаду та підключений до виходу пристрою і з'єднаний з емітером першого вихідного транзистора, база якого через перший додатковий вихідний резистор підключена до загальної шини джерела постійної напруги і з'єднана з емітером третього вихідного транзистора, колектор першого вихідного транзистора через вихідний резистор підключений до додатного полюса джерела постійної напруги і з'єднаний з колектором третього вихідного транзистора, база якого через перший резистор фазорозподільчого каскаду підключена до додатного полюса джерела постійної напруги і з'єднана з колектором транзистора фазорозподільчого каскаду [див. Скарлетт Дж. Транзисторно-транзисторные логические интегральные схемы и их применение. Пер. с англ. В.Л.Левина и Л.С.Ходоша. Под ред. Б.И.Ермолаева. - М.: Мир, 1974, фиг. 7.1, с. 73]. Недоліком аналога є те, що він реалізує логічну функцію "І" і в цифрових пристроях порівняння цей елемент може застосовуватись в парі з логічним елементом "АБО-НІ", що вдвічі збільшує кількість логічних елементів в цифрових пристроях порівняння, а це в свою чергу збільшує потужність споживання і показники відмовостійкості за раптовими відмовами цифрового пристрою порівняння. Найближчим аналогом до корисної моделі є логічний елемент [див. Соломатин Н.М. Логические элементы ЭВМ. - Μ.: Высшая школа, 1980, рис. 3.6д, с. 92], який містить вхідний двоемітерний транзистор, два вхідних діода, вхідний резистор, проміжний резистор, проміжний транзистор, проміжний діод, транзистор першого фазорозподільчого каскаду, перший, другий резистори фазорозподільчого каскаду, вихідний резистор, вихідний діод, перший, другий вихідні транзистори, причому джерело постійної напруги, перший, другий, третій входи пристрою та його вихід утворені вхідним двоемітерний транзистором, першим, другим вхідними діодами, першим вхідним резистором, проміжним резистором, проміжним транзистором, проміжним діодом, транзистором першого фазорозподільчого каскаду, першим, другим резисторами першого фазорозподільчого каскаду, вихідним резистором, першим, другим вихідними транзисторами, вихідним діодом, причому перший емітер вхідного двоемітерного транзистора підключений до першого входу пристрою і з'єднаний з катодом першого вхідного діода, анод якого підключений до загальної шини джерела постійної напруги, другий емітер вхідного двоемітерного транзистора підключений до другого входу пристрою і з'єднаний з катодом проміжного діода та катодом другого вхідного діода, катод якого підключений до загальної шини джерела постійної напруги, база вхідного двоемітерного транзистора через вхідний резистор підключена до додатного полюса джерела постійної напруги, колектор з'єднаний з базою транзистора першого фазорозподільчого каскаду, емітер якого через другий резистор першого фазорозподільчого каскаду підключений до загальної шини джерела постійної напруги та з'єднаний з базою другого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор підключений до виходу пристрою і з'єднаний з катодом вихідного діода, анод якого з'єднаний з емітером першого вихідного транзистора, колектор якого через вихідний резистор підключений до додатного полюса джерела постійної напруги, база через перший резистор першого фазорозподільчого каскаду підключена до додатного 1 UA 101020 U 5 10 15 20 25 30 35 40 45 50 55 60 полюса джерела постійної напруги і з'єднана з анодом проміжного діода, колектором транзистора першого фазорозподільчого каскаду і колектором проміжного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, база з'єднана з першим виводом проміжного резистора, другий вивід якого підключений до третього входу пристрою. Недоліком найближчого аналога є те, що він реалізує логічну функцію "І-НІ" і в цифрових пристроях порівняння цей елемент може застосовуватись в парі з логічним елементом "АБО", що вдвічі збільшує кількість логічних елементів в цифрових пристроях порівняння, а це в свою чергу підвищує потужність споживання цифрового пристрою порівняння і знижує показники відмовостійкості за раптовими відмовами. В основу корисної моделі поставлена задача створення такого логічного елемента, в якому за рахунок введення нових елементів і зв'язків між ними реалізовано логічну функцію "ЗАБОРОНА" в один ступінь швидкодії, що дозволяє спростити цифрові пристрої за рахунок зменшення кількості логічних елементів, а це призводить до підвищення відмовостійкості цих цифрових пристроїв за раптовими відмовами. Поставлена задача вирішується тим, що в логічний елемент, який містить джерело постійної напруги, перший, другий входи, вихід пристрою, вхідний двоемітерний транзистор, перший, другий вхідні діоди, перший проміжний транзистор, транзистор першого фазорозподільчого каскаду, перший, другий вхідні транзистори, проміжний і вихідний діоди, перший вхідний резистор, перший, другий резистори першого фазорозподільчого каскаду, проміжний резистор, вихідний резистор, перший і другий вихідні транзистори, причому база вхідного двоемітерного транзистора через перший вхідний резистор підключена до додатного полюса джерела постійної напруги, перший емітер з'єднаний з катодом першого вхідного діода, анод якого підключений до загальної шини джерела постійної напруги, другий емітер з'єднаний з катодом проміжного діода і катодом другого вхідного діода, анод якого підключений до загальної шини джерела постійної напруги, колектор з'єднаний з базою транзистора першого фазорозподільчого каскаду, емітер якого через другий резистор першого фазорозподільчого каскаду підключений до загальної шини джерела постійної напруги і з'єднаний з базою другого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор підключений до виходу пристрою і з'єднаний з катодом вихідного діода, анод якого з'єднаний з емітером першого вихідного транзистора, колектор якого через вихідний резистор підключено до додатного полюса джерела постійної напруги, а база з'єднана з анодом проміжного діода і колектором транзистора першого фазорозподільчого каскаду та через перший резистор першого фазорозподільчого каскаду підключений до додатного полюса джерела постійної напруги, а також емітер першого проміжного транзистора підключений до загальної шини джерела постійної напруги, база з'єднана з першим входом проміжного резистора, згідно з корисною моделлю, додатково введено вхідний транзистор, перший, другий транзистори інвертуючого каскаду, транзистор другого фазорозподільчого каскаду, третій вихідний транзистор, другий вхідний резистор, перший, другий резистори інвертуючого каскаду, резистор другого фазорозподільчого каскаду, причому другий вивід першого проміжного резистора підключений до першого ходу пристрою і з'єднаний з емітером вхідного транзистора, катодом першого вхідного діода і катодом проміжного діода, анод якого підключений через резистор другого фазорозподільчого каскаду до додатного полюса джерела постійної напруги і з'єднаний з базою третього вихідного транзистора, колектор якого через вихідний транзистор підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з емітером першого вихідного транзистора і анодом вихідного діода, а також анод проміжного діода з'єднаний з колектором транзистора другого фазорозподільчого каскаду, емітер якого з'єднаний з емітером транзистора першого фазорозподільчого каскаду, базою другого вихідного транзистора і через другий резистор першого фазорозподільчого каскаду підключений до загальної шини джерела постійної напруги, база транзистора другого фазорозподільчого каскаду через другий резистор інвертуючого каскаду підключена до додатного полюса джерела постійної напруги і з'єднана з колекторами першого і другого транзисторів інвертуючого каскаду, емітер другого транзистора інвертуючого каскаду підключений до загальної шини джерела постійної напруги, база через перший резистор інвертуючого каскаду підключена до загальної шини джерела постійної напруги і з'єднана з емітером першого транзистора інвертуючого каскаду, база якого з'єднана з колектором вхідного двоемітерного транзистора, а колектор вхідного транзистора з'єднаний з базою транзистора першого фазорозподільчого каскаду, база через другий вхідний резистор підключена до додатного полюса джерела постійної напруги. Корисна модель пояснюється кресленням, де зображена схема логічного елемента. Пристрій містить додатний полюс 7 і загальну шину 27 джерела постійної напруги, перший 1, другий 2 входи і вихід 25 пристрою, вхідний 3 і вхідний двоемітерний 4 транзистори, перший 5 і 2 UA 101020 U 5 10 15 20 25 30 35 40 45 50 55 60 другий 6 вхідні діоди, перший 9, другий 8 вхідні резистори, проміжний резистор 10, проміжний транзистор 11, проміжний діод 28, перший 12, другий 13 транзистори інвертуючого каскаду, перший 14, другий 15 резистори інвертуючого каскаду, транзистор 16 другого фазорозподільчого каскаду, резистор 17 другого фазорозподільчого каскаду, транзистор 18 першого фазорозподільчого каскаду, перший 19 і другий 20 резистори першого фазорозподільчого каскаду, третій 21 і перший 22 вихідні транзистори, вихідний резистор 23, вихідний діод 24, другий вихідний транзистор 26, причому бази двоемітерного вхідного транзистора 4 і вхідного транзистора відповідно через перший 9 і другий 8 вхідні резистори підключені до додатного полюса 7 джерела постійної напруги, другий емітер двоемітерного вхідного транзистора 4 підключений до другого входу 2 пристрою і з'єднаний з катодом другого вхідного діода 6, анод якого підключений до загальної шини 27 джерела постійної напруги, перший емітер двоемітерного вхідного транзистора 4 підключений до першого входу 1 пристрою і з'єднаний з першим виводом проміжного резистора 10, катодом проміжного діода 28, катодом першого вхідного діода 5, анод якого підключений до загальної шини 27 джерела постійної напруги, перший емітер двоемітерного вхідного транзистора 4 з'єднаний з емітером вхідного транзистора З, колектор якого з'єднаний з базою транзистора 18 першого фазорозподільчого каскаду, колектор якого через перший резистор 19 першого фазорозподільчого каскаду підключений до додатного полюса 7 джерела постійної напруги і з'єднаний з базою першого вихідного транзистора 22 і колектором проміжного транзистора 11, база якого з'єднана з другим виводом проміжного резистора 10, емітер підключений до загальної шини 27 джерела постійної напруги, емітер транзистора 18 першого фазорозподільчого каскаду через другий резистор 20 першого фазорозподільчого каскаду підключений до загальної шини 27 джерела постійної напруги та з'єднаний з емітером транзистора 16 другого фазорозподільчого каскаду і базою другого вихідного транзистора 26, емітер якого підключений до загальної шини 27 джерела постійної напруги, колектор підключений до виходу 25 пристрою і з'єднаний з катодом вихідного діода 24, анод якого з'єднаний з емітером третього вихідного транзистора 21 і емітером першого вихідного транзистора 22, колектор якого через вихідний резистор 23 підключений до додатного полюса 7 джерела постійної напруги і з'єднаний з колектором третього вихідного транзистора 21, база якого через резистор 17 другого фазорозподільчого каскаду підключена до додатного полюса 7 джерела постійної напруги і з'єднана з анодом проміжного діода 28 і колектором транзистора 16 другого фазорозподільчого каскаду, база якого через другий резистор 15 інвертуючого каскаду підключена до додатного полюса 7 джерела постійної напруги і з'єднана з колекторами першого 12, другого 13 транзисторів інвертуючого каскаду, емітер другого транзистора 13 інвертуючого каскаду підключений до загальної шини 27 джерела постійної напруги, база через перший резистор 14 інвертуючого каскаду підключена до загальної шини 27 джерела постійної напруги і з'єднана з емітером першого транзистора 12 інвертуючого каскаду, база якого з'єднана з колектором вхідного двоемітерного транзистора 4. Умовно розділимо логічний елемент (див. кресл.) на дві частини: нижню частину логічного елемента на вхідному двоемітерному транзисторі 4, першому вхідному резисторі 9, першому 5, другому 6 вхідних діодах, першому 1, другому 2 входах пристрою, проміжному діоді 28, першому 12, другому 13 транзисторах інвертуючого каскаду, першому 14, другому 15 резисторах інвертуючого каскаду, транзисторі 16 другого фазорозподільчого каскаду, резисторі 17 другого фазорозподільчого каскаду, другому резисторі 20 першого фазорозподільчого каскаду, третьому 21, другому 22, першому 26 вихідних транзисторах, вихідному резисторі 23, вихідному діоді 24, виході пристрою 25 та верхню частину логічного елемента на вхідному транзисторі 3, першому вхідному діоді 5, першому вході пристрою 1, другому вхідному резисторі 8, проміжному резисторі 10, проміжному транзисторі 11, транзисторі 18 першого фазорозподільчого каскаду, першому 19, другому 20 резисторах першого фазорозподільчого каскаду, другому 22, першому 26 вихідних транзисторах, вихідному резисторі 23, вихідному діоді 24, виході пристрою 25. Корисна модель працює наступним чином. При низькій напрузі на першому 1, другому 2 входах пристрою, першому, другому емітерах вхідного двоемітерного транзистора 4, перший 5, другий 6 вхідні діоди будуть обмежувати амплітуду від'ємних сигналів, що відповідає рівню логічного нуля на першому 1, другому 2 входах пристрою, струм від додатного полюса джерела постійної напруги 7 протікає через перший вхідний резистор 9 і відкриті емітерні переходи вхідного двоемітерного транзистора 4. В результаті, вхідний двоемітерний транзистор 4 відкривається, і напруги на його базі U б1 1,0 В недостатньо, щоб відкрити емітерні переходи першого 12, другого 13 транзисторів інвертуючого каскаду, де необхідно Uб2 2,1 В, що призведе до закритого стану першого 12, другого 13 3 UA 101020 U 5 10 15 20 25 30 35 40 45 50 55 60 транзисторів інвертуючого каскаду. На колекторах закритих першого 12, другого 13 транзисторів інвертуючого каскаду високий потенціал, і в базу транзистора 16 другого фазорозподільчого каскаду від додатного полюса 7 джерела постійної напруги через другий резистор 15 інвертуючого каскаду протікає струм. При цьому, колекторний перехід транзистора 16 другого фазорозподільчого каскаду і прямо включений проміжний діод 28, що підключений до першого 1 входу пристрою, відкриваються, і на колекторі транзистора 16 другого фазорозподільчого каскаду буде потенціал Uк1 1,0 В, якого недостатньо, щоб відкрити другий вихідний транзистор 26, де необхідний потенціал Uк2 1,4 В, а також відкрити емітерний перехід третього вихідного транзистора 21 і вихідний діод 24, де необхідний потенціал U к3 1,4 В. В результаті, третій вихідний транзистор 21, вихідний діод 24, другий вихідний транзистор 26 переходять в закритий стан і на виході 25 пристрою "Z" стан з нескінченно високим опором, коли логічний елемент повністю відключений від навантаження і не споживає та не віддає вихідний струм. При низькій напрузі на першому 1 вході і високій напрузі на другому вході 2 пристрою перший вхідний діод 5 буде обмежувати амплітуду від'ємних сигналів, що відповідає рівню логічного нуля на першому 1 вході пристрою, струм від додатного полюса 7 джерела постійної напруги протікає через перший вхідний резистор 9 і відкритий перший емітерний перехід вхідного двоемітерного транзистора 4. В результаті, вхідний двоемітерний транзистор відкривається і напруги на його базі Uб1 1,0 В недостатньо, щоб відкрити перший 12, другий 13 транзистори інвертуючого каскаду, де необхідний потенціал U б2 2,1 В, що призводить до закритого стану першого 12, другого 13 транзисторів інвертуючого каскаду. Далі нижня частина логічного елемента працює аналогічно вищерозглянутому випадку, коли на перший 1, другий 2 входи пристрою подані логічні "0". В результаті, на виході 25 пристрою маємо "Z" стан з нескінченно високим опором. При високій напрузі на першому 1 вході і низькій на другому 2 вході пристрою, другий вхідний діод 6 буде обмежувати амплітуду від'ємних сигналів, що відповідає рівню логічного нуля на другому вході 2 пристрою, струм від додатного полюса джерела постійної напруги 7 протікає через перший вхідний резистор 9 і відкритий другий емітерний перехід вхідного двоемітерного транзистора 4. В результаті, вхідний двоемітерний транзистор відкривається і на його базі Uб1 1,0 В недостатньо, щоб відкрити перший 12, другий 13 транзистори інвертуючого каскаду, де необхідний потенціал Uб2 2,1 В, що призводить до закритого стану першого 12, другого 13 транзисторів інвертуючого каскаду. На колекторах закритого першого 12, другого 13 транзисторів інвертуючого каскаду високий потенціал і в базу транзистора 16 другого фазорозподільчого каскаду від додатного полюса 7 джерела постійної напруги через другий резистор 15 другого інвертуючого каскаду протікає струм, що призводить до відкритого стану транзистора 16 другого фазорозподільчого каскаду і закритого стану транзистора зворотно включеного проміжного діода 28, катод якого підключений до високого рівня вхідного сигналу на вході 1 пристрою. В базу другого вихідного транзистора 26 надходить емітерний струм відкритого транзистора 16 другого фазорозподільчого каскаду, і це призводить до відкритого стану другого вихідного транзистора 26. На колекторі відкритого транзистора 16 другого фазорозподільчого каскаду низький потенціал Uк3 1,0 В, якого недостатньо для того, щоб відкрити третій вихідний транзистор 21 і вихідний діод 24. В результаті, третій вихідний транзистор 21, вихідний діод 24 закриваються, і на виході пристрою 25 встановлюється логічний "0" за рахунок відкритого стану другого вихідного транзистора 26, який малим опором колекторемітер підключає вихід 25 пристрою до загальної шини 27 джерела постійної напруги. Якщо на перший 1, другий 2 входи пристрою подано високу напругу, що відповідає рівню логічної "1" на входах 1, 2, то перший 5, другий 6 вхідні діоди при цьому зворотно включені, що призводить до закритого стану вхідних діодів 5, 6. При цьому вхідний двоемітерний транзистор 4 працює в інверсному активному режимі і напруги на його базі Uб2 2,1 В достатньо для відкриття колекторного переходу вхідного двоемітерного транзистора 4, емітерних переходів першого 12, другого 13 транзисторів інвертуючого каскаду. Це призводить до відкритого стану першого 12, другого 13 транзисторів інвертуючого каскаду, на колекторах яких низький потенціал Uк1 1,0 В, якого недостатньо для того, щоб відкрити транзистор 16 другого фазорозподільчого каскаду, де необхідний потенціал Uк2 1,4 В. Це обумовлює закритий стан транзистора 16 другого фазорозподільчого каскаду. Проміжний діод 28 знаходиться в закритому стані, оскільки його катод підключений до високого рівня логічної "1" на першому 1 вході пристрою. В базу другого вихідного транзистора 26 не надходить струм емітера транзистора 16 другого фазорозподільчого каскаду, що знаходиться в закритому стані, і тому другий вихідний транзистор 26 закривається. На колекторі закритого транзистора 16 другого фазорозподільчого каскаду високий потенціал і в базу третього вихідного транзистора 21 протікає струм від додатного полюса 7 джерела постійної напруги через резистор 17 другого фазорозподільчого 4 UA 101020 U 5 10 15 20 25 30 35 40 45 50 55 каскаду, що призводить до відкритого стану третього вихідного транзистора 21, вихідного діода 24. Вихід пристрою 25 через відкритий вихідний діод 24, малий опір переходу колектор-емітер відкритого третього вихідного транзистора 21 і вихідний резистор 23 підключений до додатного полюса 7 джерела постійної напруги та через великий опір закритого другого вихідного транзистора 26 підключений до загальної шини 27 джерела постійної напруги, що відповідає рівню логічної "1" на виході 25 пристрою. Таким чином, нижня частина логічного елемента в разі подачі логічної одиниці на перший вхід 1 пристрою реалізує логічну операцію І, а в разі подачі логічного нуля на перший вхід 1 пристрою на виході 25 пристрою буде "Z" стан з нескінченно високим опором. При низькій напрузі на першому вході 1 пристрою перший вхідний діод 5 буде обмежувати амплітуду від'ємних сигналів, що відповідає рівню логічного нуля на першому вході 1 пристрою, струм від додатного полюса 7 джерела постійної напруги протікає через другий вхідний резистор 8 і відкритий перший емітерний перехід вхідного двоемітерного транзистора 4. В результаті, вхідний двоемітерний транзистор 4 відкривається, і напруги на його базі Uб1 1,0 В недостатньо для того, щоб відкрити емітерний перехід транзистора 18 першого фазорозподільчого каскаду і другого вихідного транзистора 26. В результаті, транзистор 18 першого фазорозподільчого каскаду і другий вихідний транзистор 26 закриваються. Проміжний транзистор 11 знаходиться в закритому стані і не впливає на роботу верхньої частини пристрою тому, що його база через проміжний резистор 10 підключена до першого входу 1 пристрою, на який подано низьку напругу логічного "0". На колекторі закритого транзистора 18 першого фазорозподільчого каскаду високий потенціал і в базу першого вихідного транзистора 22 протікає струм від додатного полюса 7 джерела постійної напруги через перший резистор 19 першого фазорозподільчого каскаду, що обумовлює відкритий стан першого вихідного транзистора 22. Струм емітера відкритого першого вихідного транзистора 22 надходить в анод прямо включеного вихідного діода 24, що обумовлює відкритий стан вихідного діода 24. Вихід пристрою 25 через малий опір відкритого діода 24, малий опір переходу колектор-емітер відкритого першого вихідного транзистора 22, вихідний резистор 23 підключений до додатного полюса 7 джерела постійної напруги та через великий опір закритого другого вихідного транзистора 26 не підключений до загальної шини 27 джерела постійної напруги, а це відповідає рівню логічної "1" на виході 25 пристрою. Вихідний резистор 23 запобігає перевантаженню першого вихідного транзистора 22, вихідний діод 24 обмежує вихідний струм в разі короткого замикання виходу 25 пристрою та при перемиканнях логічного елемента з логічної "1" в "0", або з логічного "0" в "1". Другий резистор 20 першого фазорозподільчого каскаду забезпечує закритий стан другого вихідного транзистора 26. Слід додати, що перший вихідний транзистор 22, вихідний діод 24, перший резистор 19 першого фазорозподільчого каскаду утворюють емітерний повторювач, який забезпечує передачу рівня напруги логічної "1" на вихід 25 пристрою. Якщо на перший вхід 1 пристрою подано високу напругу, що відповідає рівню логічної "1" на вході 1 пристрою, то в цьому випадку перший вхідний діод 5 зворотно включений, що призводить до закритого стану першого вхідного діода 5. При цьому, вхідний транзистор 3 працює в інверсному активному режимі і напруги на його базі Uб2 1,7 В достатньо для того, щоб відкрити колекторний перехід вхідного транзистора 3. В базу проміжного транзистора 11 протікає струм від першого входу 1 пристрою, на який поданий сигнал логічної "1" через проміжний резистор 10, що обмежує струм бази проміжного транзистора 11, це призводить до відкритого стану проміжного транзистора 11. На колекторі відкритого проміжного транзистора 11 і колекторі транзистора 18 першого фазорозподільчого каскаду низький потенціал, що обумовлює відкритий стан колекторного переходу транзистора 18 першого фазорозподільчого каскаду. В базу другого вихідного транзистора 26 не надходить струм через закритий емітерний перехід транзистора 18 першого фазорозподільчого каскаду, що призводить до закритого стану другого вихідного транзистора 26. На колекторах проміжного транзистора 11, транзистора 18 першого фазорозподільчого каскаду низький потенціал Uк1 1,0 В, якого недостатньо для того, щоб відкрити перший вихідний транзистор 22, вихідний діод 24, де необхідний потенціал U к2 1,4 В. В зв'язку з цим, перший вихідний транзистор 21, вихідний діод 24 переходять в закритий стан. На виході 25 пристрою "Z" стан з нескінченно високим опором. Таким чином, верхня частина логічного елемента в разі подачі на перший вхід 1 пристрою логічної "1" реалізує на виході 25 пристрою "Z" стан з нескінченно високим опором, а в разі подачі логічного "0" на перший вхід 1 пристрою інвертує вхідний сигнал (логічна "1") на виході 25 пристрою. Стани входів і виходів пристрою подані в таблиці. 60 5 UA 101020 U Таблиця Вхід 1 0 0 1 1 5 10 15 Вхід 2 0 1 0 1 Вихід нижньої частини пристрою Ζ Ζ 0 1 Вихід верхньої частини пристрою 1 1 Ζ Z Вихід 25 1 1 0 1 Логічні схеми з трьома станами можна об'єднувати за виходами на одне спільне навантаження, але при цьому в будь-який момент часу навантаження повинно обслуговуватись одним елементом, а всі інші повинні знаходитись в третьому "Z" стані (див. Соломатин Н. М. Логические элементы ЭВМ. - Μ.: Высшая школа, 1980, с. 96). Об'єднуючи сигнали на виходах нижньої частини і верхньої частини пристрою, отримуємо на виході 25 пристрою логічну функцію "ІМПЛІКАЦІЯ відносно X1", де X1 - логічний сигнал на першому вході 1 пристрою. Якщо підключити емітер вхідного транзистора 3, катод проміжного діода 28 до другого входу 2 пристрою, та другий вивід проміжного резистора 10, то пристрій буде реалізовувати логічну функцію "ЗАБОРОНА відносно Х2", де Х2 - логічний сигнал на другому вході 2 пристрою. Таким чином, реалізовано новий логічний елемент транзисторно-транзисторної логіки "ІМПЛІКАЦІЯ", що дозволить реалізувати цифрові пристрої порівняння з меншою кількістю логічних елементів в один ступінь швидкодії і з меншою потужністю споживання та кращими показниками відмовостійкості за раптовими відмови за рахунок спрощення цифрових пристроїв порівняння. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 20 25 30 35 40 45 50 Логічний елемент, що містить джерело постійної напруги, перший, другий входи, вихід пристрою, вхідний двоемітерний транзистор, перший, другий вхідні діоди, перший проміжний транзистор, транзистор першого фазорозподільчого каскаду, перший, другий вхідні транзистори, проміжний і вихідний діоди, перший вхідний резистор, перший, другий резистори першого фазорозподільчого каскаду, проміжний резистор, вихідний резистор, перший і другий вихідні транзистори, причому база вхідного двоемітерного транзистора через перший вхідний резистор підключена до додатного полюса джерела постійної напруги, перший емітер з'єднаний з катодом першого вхідного діода, анод якого підключений до загальної шини джерела постійної напруги, другий емітер з'єднаний з катодом проміжного діода і катодом другого вхідного діода, анод якого підключений до загальної шини джерела постійної напруги, колектор з'єднаний з базою транзистора першого фазорозподільчого каскаду, емітер якого через другий резистор першого фазорозподільчого каскаду підключений до загальної шини джерела постійної напруги і з'єднаний з базою другого вихідного транзистора, емітер якого підключений до загальної шини джерела постійної напруги, колектор підключений до виходу пристрою і з'єднаний з катодом вихідного діода, анод якого з'єднаний з емітером першого вихідного транзистора, колектор якого через вихідний резистор підключено до додатного полюса джерела постійної напруги, а база з'єднана з анодом проміжного діода і колектором транзистора першого фазорозподільчого каскаду та через перший резистор першого фазорозподільчого каскаду підключений до додатного полюса джерела постійної напруги, а також емітер першого проміжного транзистора підключений до загальної шини джерела постійної напруги, база з'єднана з першим входом проміжного резистора, який відрізняється тим, що в нього введено вхідний транзистор, перший, другий транзистори інвертуючого каскаду, транзистор другого фазорозподільчого каскаду, третій вихідний транзистор, другий вхідний резистор, перший, другий резистори інвертуючого каскаду, резистор другого фазорозподільчого каскаду, причому другий вивід першого проміжного резистора підключений до першого ходу пристрою і з'єднаний з емітером вхідного транзистора, катодом першого вхідного діода і катодом проміжного діода, анод якого підключений через резистор другого фазорозподільчого каскаду до додатного полюса джерела постійної напруги і з'єднаний з базою третього вихідного транзистора, колектор якого через вихідний транзистор підключений до додатного полюса джерела постійної напруги, емітер з'єднаний з емітером першого вихідного транзистора і анодом вихідного діода, а також анод проміжного діода з'єднаний з колектором транзистора другого фазорозподільчого каскаду, емітер якого з'єднаний з емітером транзистора першого фазорозподільчого каскаду, базою другого вихідного транзистора і через другий резистор першого фазорозподільчого каскаду підключений до загальної шини джерела постійної напруги, база транзистора другого 6 UA 101020 U 5 фазорозподільчого каскаду через другий резистор інвертуючого каскаду підключена до додатного полюса джерела постійної напруги і з'єднана з колекторами першого і другого транзисторів інвертуючого каскаду, емітер другого транзистора інвертуючого каскаду підключений до загальної шини джерела постійної напруги, база через перший резистор інвертуючого каскаду підключена до загальної шини джерела постійної напруги і з'єднана з емітером першого транзистора інвертуючого каскаду, база якого з'єднана з колектором вхідного двоемітерного транзистора, а колектор вхідного транзистора з'єднаний з базою транзистора першого фазорозподільчого каскаду, база через другий вхідний резистор підключена до додатного полюса джерела постійної напруги. Комп’ютерна верстка Л. Ціхановська Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 7

ДивитисяДодаткова інформація

Автори англійськоюKychak Vasyl Martynovych, Stronskyy Viktor Volodymyrovych

Автори російськоюКичак Василий Мартынович, Стронский Виктор Владирович

МПК / Мітки

МПК: H03K 19/08

Код посилання

<a href="https://ua.patents.su/9-101020-logichnijj-element.html" target="_blank" rel="follow" title="База патентів України">Логічний елемент</a>

Попередній патент: Робоче обладнання драглайна

Наступний патент: Борошняний виріб тороподібної форми з начинкою

Випадковий патент: Спосіб ендоваскулярно-хірургічного лікування аневризм черевної аорти самофіксівним ендопротезом