Перетворювач двійково-к-значного коду у двійковий код

Номер патенту: 111884

Опубліковано: 25.11.2016

Автори: Литвинова Євгенія Іванівна, Какурін Микола Яковлевич, Хаханов Володимир Іванович, Вареца Віталій Вікторович, Макаренко Ганна Миколаївна

Формула / Реферат

Перетворювач двійково-Κ-значного коду в двійковий код, який містить n-1 лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що вміщує прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, групу з n елементів І, групу з n елементів І-НІ, в кожному розряді дешифратор нуля, дешифратора рівняння або перевищення кроку а, в кожному розряді кодовий шифратор, що на виході формує значення коду, зменшене на значення другого кроку а, у разі рівняння або перевищення кроку а відповідним лічильником, формувач еквівалентів ФЕ, що складається з першого і другого дешифраторів, шифратора, n груп елементів АБО для запису розрядів коду зі входів перетворювача у лічильники відповідних розрядів, причому другі входи кожної з n груп елементів АБО є інформаційними входами для запису значень відповідних розрядів, а перші входи кожної з n групи елементів АБО з'єднані з відповідними виходами відповідних кодових шифраторів, входи яких в кожному розряді з'єднані з відповідними виходами лічильника цього розряду, а також з відповідними входами дешифратора нуля і дешифратора перевищення цього розряду, виходи дешифраторів нуля з'єднані з відповідними інформаційними D-входами першої групи тригерів, а виходи дешифраторів перевищення з'єднані з відповідними інформаційними D-входами другої групи тригерів, входи синхронізації тригерів обох груп з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів першої групи з'єднані з відповідними першими входами елементів групи І, прямі виходи тригерів другої групи з'єднані з відповідними першими входами елементів групи І-НІ, треті входи елементів групи І і другі входи елементів групи І-НІ з'єднані з першим затриманим виходом генератора імпульсів, інверсні виходи елементів групи І з'єднані з входом віднімання -1 у лічильнику відповідного розряду, виходи переповнення усіх лічильників, за винятком самого найстаршого, з'єднані з входом +1 лічильника наступного розряду, входи +1 та -1 лічильника молодшого розряду є входами запису числа для перетворення у число-імпульсному коді, інверсний вхід синхронізації другого дешифратора у формувачі еквівалентів з'єднано з землею, виходи першого дешифратора з'єднані з відповідними входами шифратора у формувачі еквівалентів, управляючий вхід накопичувального суматора з'єднаний з другим затриманим виходом генератора імпульсів, а виходи накопичувального суматора з'єднані з інформаційними виходами перетворювача коду, який відрізняється тим, що в перетворювач коду додатково введена третя група CD-тригерів стану, друга група елементів І, друга група елементів І-НІ, в кожний розряд введено по другому дешифратору рівняння і перевищення кроку b, дві групи із n елементів І на входах першого і другого дешифраторів і третій дешифратор у формувач еквівалентів, два додаткових (другий і третій) шифратори та два комбінаційних суматори, інверсні входи синхронізації першого і третього дешифраторів у формувачі еквівалентів з'єднані з землею, а інверсні виходи другого і третього дешифраторів з'єднані з відповідними входами другого і третього шифраторів, інверсні виходи яких з'єднані з відповідними входами першої і другої групи входів першого комбінаційного суматора у формувачі еквівалентів, виходи першого комбінаційного суматора з'єднані з відповідними входами другої групи входів другого комбінаційного суматора, перші входи якого з'єднані з відповідними виходами першого шифратора у формувачі еквівалентів, виходи другого комбінаційного суматора з'єднані з відповідними входами накопичувального суматора, виходи другого дешифратора рівняння і перевищення кроку b з'єднані з відповідними інформаційними D-входами третьої групи тригерів стану, входи синхронізації яких з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів стану третьої групи з'єднані з відповідними першими входами елементів І-НІ другої групи, другі входи яких з'єднані з першим затриманим імпульсом генератора імпульсів, інверсні виходи елементів І-НІ другої групи з'єднані з відповідними другими входами елементів І другої групи, виходи яких з'єднані з інверсним входом V у відповідному розрядному лічильнику, прямі виходи тригерів стану другої групи з'єднані з відповідними входами елементів НІ першої групи, виходи яких з'єднані з відповідними другими входами елементів І першої групи, прямі виходи тригерів стану третьої групи з'єднані з відповідними входами елементів НІ другої групи, виходи яких з'єднані з відповідними другими входами елементів І-НІ першої групи, інверсні виходи яких з'єднані з відповідними першими входами елементів І другої групи, перші входи елементів І на входах першого дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом тригера першого регістра стану, другі входи елементів І на входах першого дешифратора з'єднані з відповідним інверсним виходом тригера цього розряду, але другого регістра стану, виходи елементів І на входах першого дешифратора з'єднано з відповідним входом цього дешифратора, перші входи елементів І на входах другого дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом тригера другого регістра стану, другі входи елементів І на входах другого дешифратора з'єднані з відповідним інверсним виходом тригера цього розряду, але третього регістра стану, виходи елементів І на входах другого дешифратора з'єднано з відповідним входом другого дешифратора.

Текст

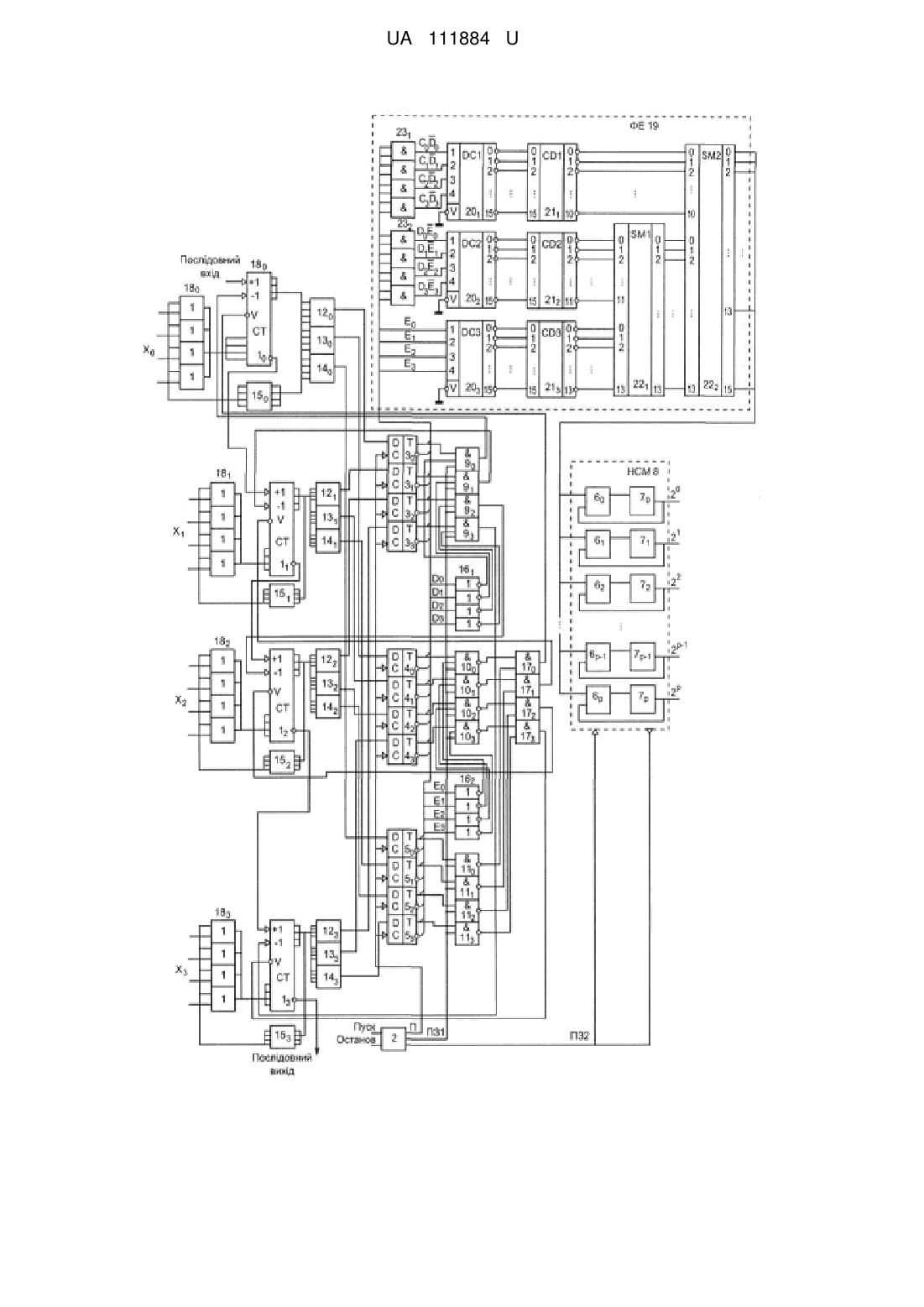

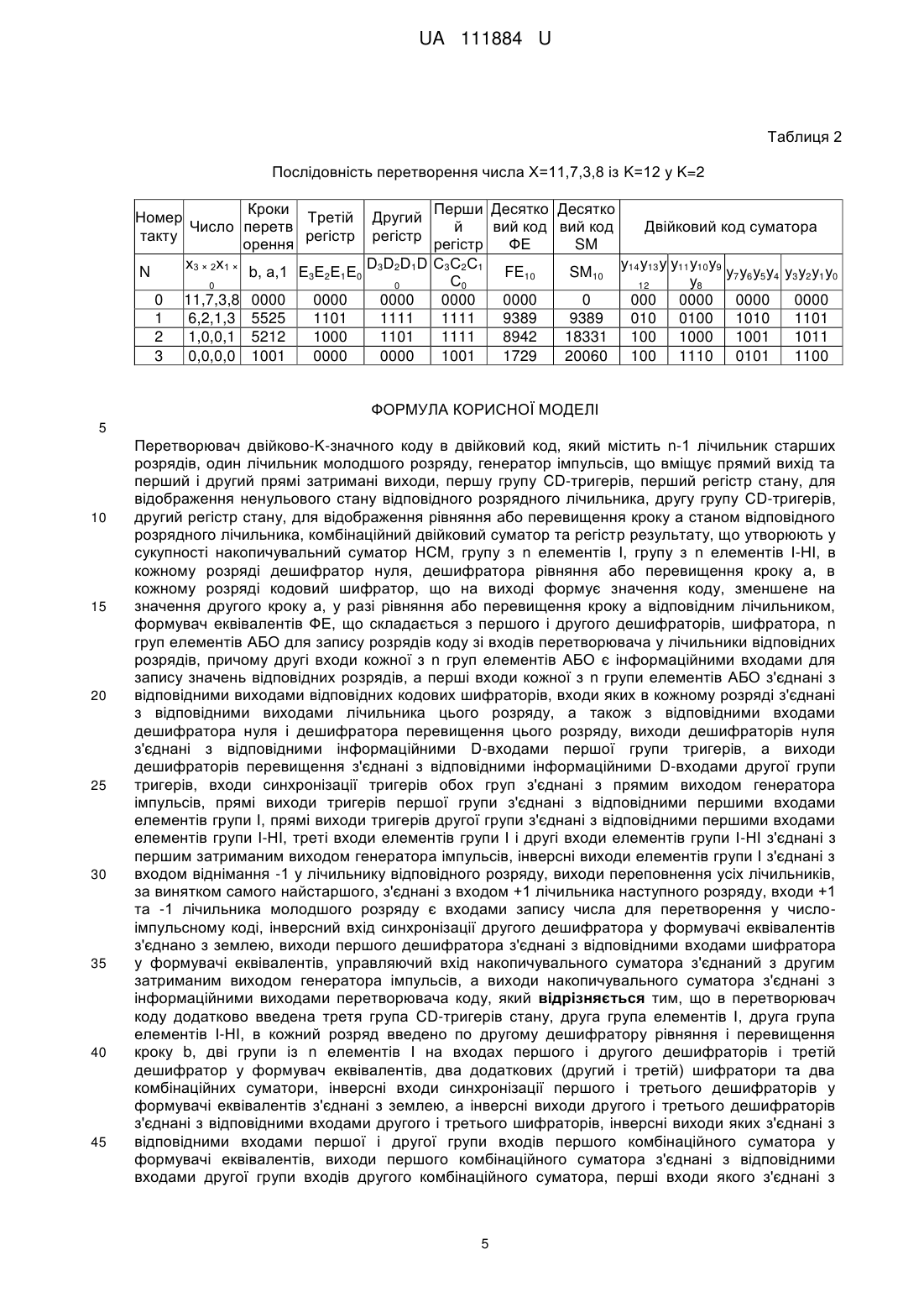

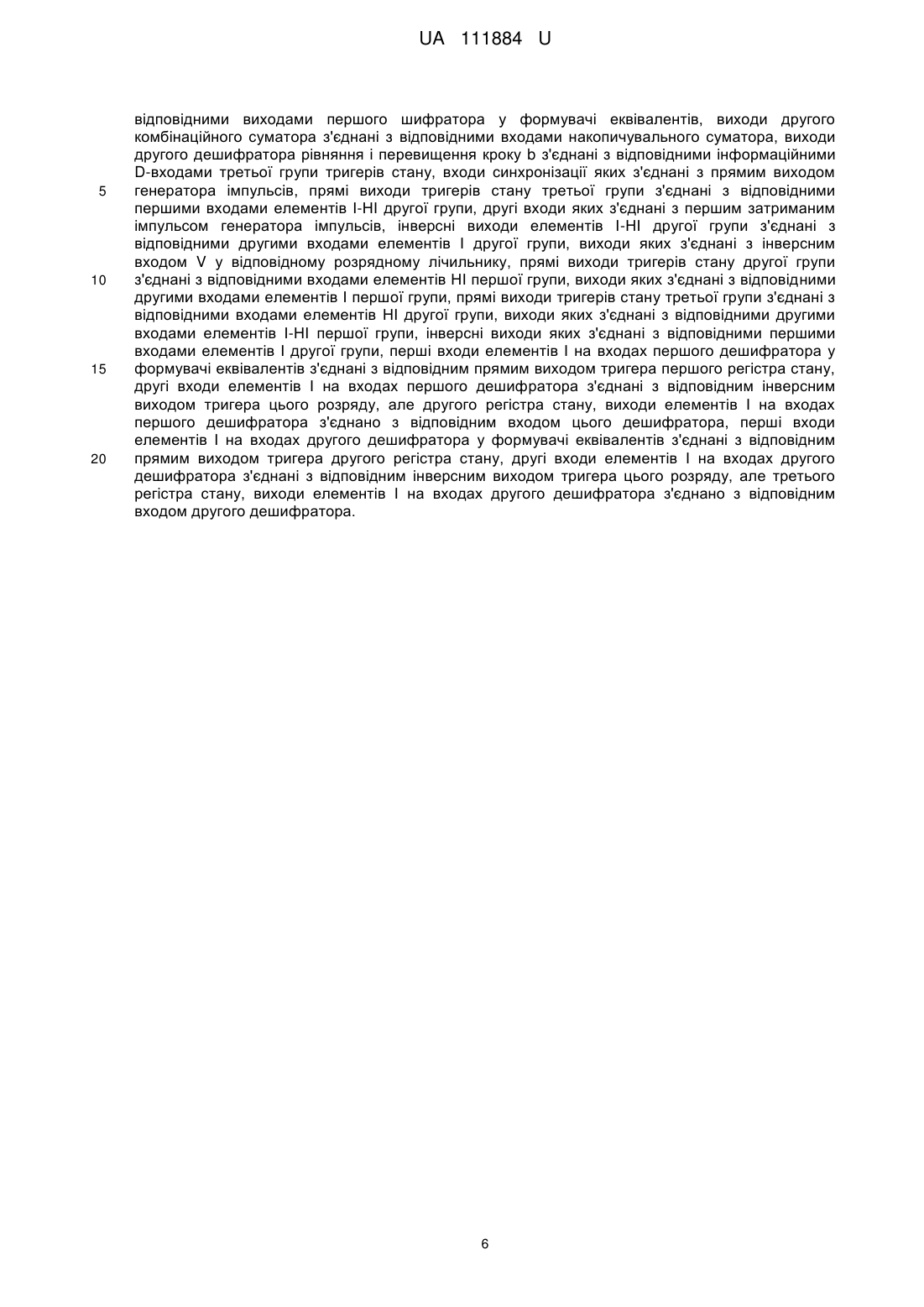

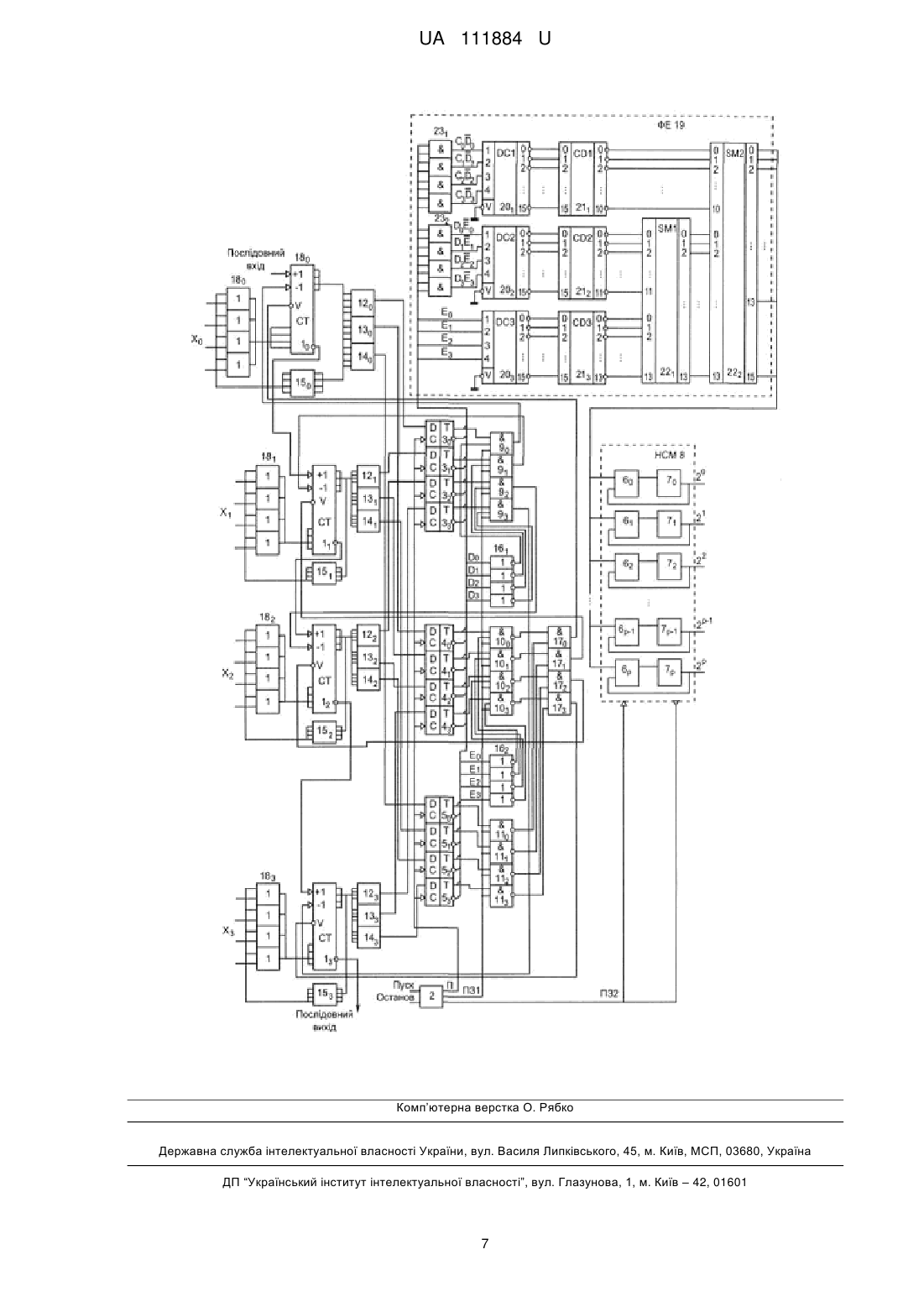

Реферат: Перетворювач двійково-Κ-значного коду в двійковий код містить n-1 лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що вміщує прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, групу з n елементів І, групу з n елементів І-НІ, в кожному розряді дешифратор нуля, дешифратора рівняння або перевищення кроку а, в кожному розряді кодовий шифратор, що на виході формує значення коду, зменшене на значення другого кроку а, у разі рівняння або перевищення кроку а відповідним лічильником, формувач еквівалентів ФЕ, що складається з першого і другого дешифраторів, шифратора, n груп елементів АБО для запису розрядів коду зі входів перетворювача у лічильники відповідних розрядів. В перетворювач коду додатково введена третя група CD-тригерів стану, друга група елементів І, друга група елементів І-НІ, в кожний розряд введено по другому дешифратору рівняння і перевищення кроку b, дві групи із n елементів І на входах першого і другого дешифраторів і третій дешифратор у формувач еквівалентів, два додаткових (другий і третій) шифратори та два комбінаційних суматори. UA 111884 U (54) ПЕРЕТВОРЮВАЧ ДВІЙКОВО-K-ЗНАЧНОГО КОДУ У ДВІЙКОВИЙ КОД UA 111884 U UA 111884 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до автоматики і обчислювальної техніки і може бути використана при побудові пристроїв обробки і перетворення інформації. Відомий трикроковий перетворювач двійково-К-значного коду у двійковий код послідовним використанням трьох кроків перетворення: b - старшого кроку, а - середнього кроку і молодшого кроку, що дорівнює одиниці, (А. с. СССР 1783618, МКИ Η 03 Μ 7/12. Преобразователь двоичноК-ичного кода в двоичный код. Опубл. Бюл. Изобретения. 1992. № 47) і що вміщує групу з n розрядних лічильників (СТ) для зберігання цифр К-значного коду n-1 лічильник старших розрядів і один лічильник молодшого розряду), генератор імпульсів, що вміщує прямий (П), прямий затриманий (ПЗ) і інверсний (І) виходи, три групи CD-тригерів: першу групу CD-тригерів (перший регістр стану) для відображення ненульового стану кожного старшого розрядного лічильника, другу групу CD-тригерів (другий регістр стану) для відображення рівняння або перевищення кроку а станом відповідного старшого розрядного лічильника, третю групу CDтригерів для відображення рівняння або перевищення кроку b станом відповідного старшого розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють в сукупності накопичувальний суматор (НСМ), першу групу елементів І та дві групи елементів І-НІ, три групи дешифраторів: першу групу дешифраторів нуля для відображення ненульового стану кожного старшого розрядного лічильника, першу групу дешифраторів перевищення для аналізу значень старших розрядів на рівняння або перевищення значення кроку а, другу групу дешифраторів перевищення для аналізу значень старших розрядів на рівняння або перевищення значення кроку b, групу кодових шифраторів, що видають на виході двійковий код, зменшений на значення кроку b, коли стан відповідного старшого розрядного лічильника дорівнює або перевищує крок b, видають на виході двійковий код, зменшений на значення кроку а, коли стан відповідного старшого розрядного лічильника дорівнює або перевищує крок а та має значення, менше кроку b, у випадку, коли стан відповідного старшого розрядного лічильника має значення, менше кроку а, кодовий шифратор передає код зі входу на вихід без зміни, а також містить другу групу елементів І, n-1 групу елементів АБО для запису значень коду у старші розрядні лічильники, два елементи АБО-НІ та формувач еквівалентів ФЕ. Формувач еквівалентів ФЕ виконують звичайно у вигляді послідовного з'єднання трьох дешифраторів DC з шифратором CD, у склад якого входять три групи елементів І та група елементів АБО. Функціонування перетворювача коду виконується наступним чином За допомогою других дешифраторів рівняння або перевищення кроку b станом відповідного старшого розрядного лічильника виконується аналіз значень старших розрядів і їх ненульові значення записуються в третій регістр стану з CD-тригерів. За допомогою перших дешифраторів рівняння або перевищення кроку а станом відповідного старшого розрядного лічильника виконується аналіз значень старших розрядів і їх ненульові значення записуються в другий регістр стану з CDтригерів. За допомогою дешифраторів нуля виконується аналіз значень старших розрядів на нуль. Двійкові показники ненульових значень старших розрядів записуються в перший регістр стану з CD-тригерів. Завдяки послідовній стратегії використання кроків перетворення за допомогою ФЕ спочатку двійковий код третього регістра стану, потім двійковий код другого регістра стану і нарешті двійковий код першого регістра стану перетворюються в двійковий код еквіваленту, який по задньому фронту прямого затриманого імпульсу (ПЗ2) додається до накопиченої суми еквівалентів у двійковому суматорі (НСМ). На перших двох етапах перетворення коду при використанні кроку b, потім кроку а, по задньому фронту інверсного імпульсу (І) і сигналів з виходів елементів І другої групи виконується запис коду з виходів кодових шифраторів у відповідні старші розрядні лічильники. На третьому етапі при використанні кроку 1 по задньому фронту інверсного імпульсу (І) виконується відрахування одиниць із значень тих старших розрядних лічильників, значення яких не дорівнюють нулю. Після обнуління усіх старших розрядів на четвертому етапі виконується трансляція (додавання) молодшого розряду до накопиченої суми еквівалентів. Завдяки послідовній стратегії використання кроків перетворення коду числа виконується за чотири етапи. Перший етап перетворення старших розрядів потребує] (К-1)/b [тактів, тому що найбільш можливе значення старшого розряду дорівнює К-1, де дужки] [означають округлення до меншого цілого, другий етап потребує] (b-1)/а [тактів, тому що найбільш можливе значення старшого розряду на другому етапі дорівнює b-1, третій етап потребує а-1 тактів, на четвертому етапі трансляція молодшого розряду додає ще один такт. Таким чином, загальна кількість тактів перетворення числа в трикроковому перетворювачі кодів становить N1=](K-1)/b[+](b-1)/a[+a (1) тактів, де Κ модуль (основа)системи числення. При Κ=12, b=5, а=2 маємо Ν1=6, а при Κ=12, b=4 та а=2 маємо Ν1=5. Найближчим аналогом по сукупності ознак до корисної моделі, що заявляється, є перетворювач двійково-Κ-значного коду в двійковий код з паралельним використанням двох 1 UA 111884 U 5 10 15 20 25 30 35 40 45 50 55 60 різних кроків перетворення (Патент України на корисну модель № 102262, МПК Н03М 7/00. Перетворювач двійково-Κ-значного коду в двійковий код. Опубл. 26.10.2015, Бюл. № 20), що містить (n-1) лічильник СТ старших розрядів і один лічильник СТ молодшого розряду для зберігання цифр Κ-значного коду (всього n лічильників), генератор імпульсів, що вміщує прямий П, прямі затримані ПЗ1 і ПЗ2 виходи, дві групи CD-тригерів (перший та другий регістри стану), комбінаційний двійковий суматор та регістр результату стану, що утворюють у сукупності накопичувальний суматор НСМ, групу з n елементів І та групу з n елементів І-НІ, групу з n дешифраторів нуля, групу з n дешифраторів перевищення, групу з n кодових шифраторів CD, що на виході формують значення коду зменшене на значення другого кроку а (у разі рівняння або перевищення кроку а відповідним лічильником), формувач еквівалентів ФЕ, що складається з двох дешифраторів DC1 і DC2, шифратора CD, елемента АБО-НІ та n груп елементів АБО для паралельного запису розрядів коду зі входів перетворювача у розрядні лічильники СТ. Розряди двійково-Κ-значного коду числа для перетворення записуються через перші бітові входи груп елементів АБО у лічильники. Перетворення числа виконується за два етапи наступним чином. За допомогою дешифраторів нуля виконується аналіз значень старших розрядів на нуль, а також за допомогою дешифраторів перевищення виконується аналіз значень розрядів на рівняння або перевищення значення кроку а. Двійкові показники ненульових значень усіх розрядів з виходів дешифраторів ненульових значень записуються в перший регістр стану, ненульові значення з дешифраторів перевищення усіх розрядів записуються в другий регістр стану. Коли на першому етапі перетворення числа у якомусь розряді (у яких то розрядах) присутні ненульові значення з дешифраторів перевищення розрядів (в цих розрядах при перетворенні використовується крок а), то використання кроку 1 у цих розрядах забороняється нульовим сигналом з виходу елемента АБО-НІ, що подається на всі перші входи групи елементів І. За допомогою ФЕ двійковий код другої групи тригерів перетворюється в двійковий код еквіваленту, який по задньому фронту прямого затриманого імпульсу ПЗ2 додається до накопиченої суми еквівалентів у накопичувальному суматорі НСМ. На першому етапі перетворення потрібно] (К-1)/а[тактів, де дужки] [означають округлення до меншого цілого, на другому етапі - (а-1) такт. Таким чином, максимальна кількість кроків для перетворення двійково-Κ-значного коду у двійковий код не перевищує значення N2=([(K-1)/a[+, (а-1) (2). При К=12 та а=2 маємо N2=6, а при Κ=12 та а=4 маємо N2=5. В основу корисної моделі поставлена задача підвищення швидкодії двокрокового перетворювача двійково-Κ-значного коду у двійковий код за рахунок використання паралельної стратегії трьох різних кроків перетворення у різних розрядах та нового схемного рішення. Поставлена задача вирішується тим, що перетворювач двійково-Κ-значного коду в двійковий код, який містить (n-1) лічильник старших розрядів, один лічильник молодшого розряду, генератор імпульсів, що вміщує прямий вихід та перший і другий прямі затримані виходи, першу групу CD-тригерів, перший регістр стану, для відображення ненульового стану відповідного розрядного лічильника, другу групу CD-тригерів, другий регістр стану, для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника, комбінаційний двійковий суматор та регістр результату, що утворюють у сукупності накопичувальний суматор НСМ, групу з n елементів І, групу з n елементів І-НІ, в кожному розряді дешифратор нуля, дешифратора рівняння або перевищення кроку а, в кожному розряді кодовий шифратор, що на виході формує значення коду зменшене на значення другого кроку а, у разі рівняння або перевищення кроку а відповідним лічильником, формувач еквівалентів ФЕ, що складається з першого і другого дешифраторів, шифратора, n груп елементів АБО для запису розрядів коду зі входів перетворювача у лічильники відповідних розрядів, причому другі входи кожної з n груп елементів АБО є інформаційними входами для запису значень відповідних розрядів, а перші входи кожної з n групи елементів АБО з'єднані з відповідними виходами відповідних кодових шифраторів, входи яких в кожному розряді з'єднані з відповідними виходами лічильника цього розряду, а також з відповідними входами дешифратора нуля і дешифратора перевищення цього розряду, виходи дешифраторів нуля з'єднані з відповідними інформаційними D-входами першої групи тригерів, а виходи дешифраторів перевищення з'єднані з відповідними інформаційними D-входами другої групи тригерів, входи синхронізації тригерів обох груп з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів першої групи з'єднані з відповідними першими входами елементів групи І, прямі виходи тригерів другої групи з'єднані з відповідними першими входами елементів групи I-НІ, треті входи елементів групи І і другі входи елементів групи І-НІ з'єднані з першим затриманим виходом генератора імпульсів, інверсні виходи елементів групи І з'єднані з входом віднімання -1 у лічильнику відповідного розряду, виходи переповнення усіх лічильників, за винятком самого найстаршого, з'єднані з входом +1 лічильника наступного розряду, входи +1 2 UA 111884 U 5 10 15 20 25 30 35 40 45 50 55 60 та -1 лічильника молодшого розряду є входами запису числа для перетворення у числоімпульсному коді, інверсний вхід синхронізації другого дешифратора у формувачі еквівалентів з'єднано з землею, виходи першого дешифратора з'єднані з відповідними входами шифратора у формувачі еквівалентів, управляючий вхід накопичувального суматора з'єднаний з другим затриманим виходом генератора імпульсів, а виходи накопичувального суматора з'єднані з інформаційними виходами перетворювача коду, згідно з корисною моделлю, в перетворювач коду додатково введена третя група CD-тригерів стану, друга група елементів І, друга група елементів І-НІ, в кожний розряд введено по другому дешифратору рівняння і перевищення кроку b, дві групи із n елементів І на входах першого і другого дешифраторів та третій дешифратор у формувач еквівалентів, два додаткових (другий і третій) шифратори та два комбінаційних суматора, інверсні входи синхронізації першого і третього дешифраторів у формувачі еквівалентів з'єднані з землею, а інверсні виходи другого і третього дешифраторів з'єднані з відповідними входами другого і третього шифраторів, інверсні виходи яких з'єднані з відповідними входами першої і другої групи входів першого комбінаційного суматора у формувачі еквівалентів, виходи першого комбінаційного суматора з'єднані з відповідними входами другої групи входів другого комбінаційного суматора, перші входи якого з'єднані з відповідними виходами першого шифратора у формувачі еквівалентів, виходи другого комбінаційного суматора з'єднані з відповідними входами накопичувального суматора, виходи другого дешифратора рівняння і перевищення кроку b з'єднані з відповідними інформаційними D-входами третьої групи тригерів стану, входи синхронізації яких з'єднані з прямим виходом генератора імпульсів, прямі виходи тригерів стану третьої групи з'єднані з відповідними першими входами елементів І-НІ другої групи, другі входи яких з'єднані з першим затриманим імпульсом генератора імпульсів, інверсні виходи елементів І-НІ другої групи з'єднані з відповідними другими входами елементів І другої групи, виходи яких з'єднані з інверсним входом V у відповідному розрядному лічильнику, прямі виходи тригерів стану другої групи з'єднані з відповідними входами елементів НІ першої групи, виходи з'єднані з відповідними другими входами елементів І першої групи, прямі виходи тригерів стану третьої групи з'єднані з відповідними входами елементів НІ другої групи, виходи яких з'єднані з відповідними другими входами елементів І-НІ першої групи, інверсні виходи яких з'єднані з відповідними першими входами елементів І другої групи, перші входи елементів І на входах першого дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом тригера першого регістра стану, другі входи елементів І на входах першого дешифратора з'єднані з відповідним інверсним виходом тригера цього розряду, але другого регістра стану, виходи елементів І на входах першого дешифратора з'єднано з відповідним входом першого дешифратора, перші входи елементів І на входах другого дешифратора у формувачі еквівалентів з'єднані з відповідним прямим виходом тригера другого регістра стану, другі входи елементів І на входах другого дешифратора з'єднані з відповідним інверсним виходом тригера цього розряду, але третього регістра стану, виходи елементів І на входах другого дешифратора з'єднано з відповідним входом другого дешифратора. Таким чином, завдяки введенню в перетворювач коду третьої групи тригерів стану, другої групи елементів І, другої групи елементів І-НІ, двох груп із n елементів НІ, в кожний розряд по другому дешифратору рівняння і перевищення кроку b, двох груп із n елементів І на входах першого і другого дешифраторів та третього дешифратора в формувачі еквівалентів, двох додаткових шифраторів (другого і третього), двох комбінаційних суматорів та новим зв'язкам створено перетворювач коду, що дозволяє за рахунок нового схемного рішення виконувати перетворення усіх розрядів, зокрема і молодшого, паралельно. Вибір оптимального значення кількості тактів перетворення N2 згідно з формулою (2) N2= [](K-1)/b[,] (b-1)/a[, (a-1)], де дужки [] означають вибір більшої складової, дає при К=12, b=5 та а=2 мінімальне значення Ν2=3. У таблиці 1 наведена послідовність перетворення цифр 12-річної системи числення, з якої витікає, що для цього достатньо всього 3 такти. У таблиці 2 наведена послідовність перетворення числа Х=11,7,3,8 із Κ=12 у Κ=2 при b=5 і а=2. На кресленні зображена структурна схема перетворювача двійково-Κ-значного коду в двійковий код для узагальненої кількості розрядів n=4. Перетворювач коду містить в кожному розряді лічильник 1 (СТ), генератор імпульсів 2, що вміщує прямий вихід (П), перший прямий затриманий (ПЗ1) і другий прямий затриманий (ПЗ2) виходи, групу з n CD-тригерів 3 для відображення ненульового стану кожного відповідного розрядного лічильника 1, групу з n CD-тригерів 4 для відображення рівняння або перевищення кроку а станом відповідного розрядного лічильника 1, групу з n CD-тригерів 5 для відображення рівняння або перевищення кроку b станом відповідного розрядного лічильника 1, комбінаційний 3 UA 111884 U 5 10 15 20 25 30 35 40 45 двійковий суматор 6 та регістр результату 7, що утворюють у сукупності накопичувальний суматор 8 (НСМ), виходи якого є виходами перетворювача коду, першу групу з n елементів І 9 та дві групи з n елементів І-НІ 10 і І-НІ 11, групу з n дешифраторів нуля 12, першу групу з n дешифраторів перевищення кроку а 13, другу групу з n дешифраторів перевищення кроку b 14, групу з n кодових шифраторів 15, дві групи інверторів 16 1 і 16 2 по n елементів НІ в кожній, другу групу з n елементів І 17, n груп елементів АБО 18, формувач еквівалентів 19 (ФЕ), що складається з першого, другого і третього дешифраторів з інверсними виходами 20 (DC1), (DC2), (DC3), трьох шифраторів 21 (CD1), (CD2), (CD3), двох комбінаційних суматорів 22 1 (SM1) і 22 2 (SM2) та двох груп із n елементів І в кожній 23 1 і 23 2. Пристрій працює наступним чином. Розглянемо послідовність перетворення числа Х=х 3 × 2x1 =11,7,3,8 з Κ=12 у Κ=2 при b=5 і а=2. Після запису коду у лічильники 1 двійкові значення з × 0 дешифраторів нуля 12, першого 13 і другого 14 дешифраторів перевищення на кожному такті перетворення записуються у відповідні розряди тригерів групи 3 С3 С2 С1 C0, групи 4 D3 D2 D1 D0 та групи 5 Е3 Е2 E1 E0. Спочатку (на першому такті) перетворення числа виконується з кроком b=5 у 3,2 і 0 розрядах числа та з кроком а=2 у розряді 1 (стовбець 3 у Табл. 2). В результаті у суматорі одержимо десяткове число 9389. На другому такті перетворення числа в розрядах 3,2,1.0 застосовуються відповідно кроки 5,2,1,2. Значення коду еквівалентів, що видає на виході формувач еквівалентів ФЕ 19, залежить від кодів на входах дешифраторів DC3 21, DC2 21, DC1 21 та настройки шифраторів CD3 22., CD2 22, CD1 22. Загальний вигляд виразу на виході старшого дешифратора DC3 21 може змінюватися від S(DC3)=0 до 3 2 1 0 S(DC3)=bK +bK +bK +bK . i Компонент b·K входить у повний вираз S(DC3) у разі, коли хi≥b. Аналогічно загальний вираз на виході середнього шифратора S(DC2) може змінюватися від 3 2 1 0 i S(DC2)=0 до S(DC2)=aK +аК +аК +аК . Компонент а•K входить у повний вираз у разі, коли а≤хi

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03M 7/00

Мітки: двійковий, перетворювач, коду, код, двійково-к-значного

Код посилання

<a href="https://ua.patents.su/9-111884-peretvoryuvach-dvijjkovo-k-znachnogo-kodu-u-dvijjkovijj-kod.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійково-к-значного коду у двійковий код</a>

Попередній патент: Пристрій для аналого-цифрового перетворення

Наступний патент: Циліндричне сітчасте склепіння

Випадковий патент: Удосконалений доїльний апарат