Приймальна розріджена адаптивна антенна решітка

Номер патенту: 55415

Опубліковано: 10.12.2010

Автори: Ільченко Михайло Юхимович, Якорнов Євгеній Аркадійович, Мазуренко Олександр Вікторович

Формула / Реферат

Приймальна розріджена адаптивна антенна решітка, що містить три рознесені у просторі антенні елементи, три фільтри, дільник потужності, суматор, детектор та препроцесор, що містить два фазообертачі, два аналого-цифрових перетворювачі, дільник потужності, фазометр, причому до виходу кожного з трьох антенних елементів приєднаний вхід відповідного фільтра, перший вихід дільника потужності препроцесора приєднаний до першого входу фазометра препроцесора, вихід якого приєднано до входу першого аналого-цифрового перетворювача препроцесора, вихід детектора приєднаний до четвертого входу препроцесора, яка відрізняється тим, що антенні елементи розміщені на одній лінії з однаковою відстанню між ними, яка може бути довільною, всі фільтри виконані смугопропускаючими та узгодженими за спектром з сигналом, що приймається, і в неї введені три підсилювачі високої частоти, два багатоканальні дільники потужності з одним входом та S+1виходами, де S = [log3 d'] S Î Z - кількість додаткових каналів обробки, де d' - відстань між антенними елементами у довжинах хвиль, всі дільники потужності виконані багатоканальними, багатоканальний генератор високочастотних коливань, 3xS множників частоти, S суматорів додаткового каналу, суматор виконано суматором основного каналу, S множників сигналів, спрямований відгалужувач, також в препроцесор введені три блоки дискретних прецизійних атенюаторів, три блоки дискретних прецизійних ліній затримок, блок дискретних прецизійних фазообертачів, всі фазообертачі виконані блоками дискретних прецизійних фазообертачів, три спрямованих відгалужувачі, п'ять дільників потужності, три амплітудних детектори, чотири аналого-цифрових перетворювачі, всі аналого-цифрові перетворювачі виконуються аналогічними, два блоки широкодіапазонних фазометрів, всі фазометри виконані широкодіапазонними, мікропроцесор, дві вхідних шини передачі даних, три вихідних шини передачі даних, причому до кожного з виходів трьох антенних елементів каскадно приєднані смугопропускаючий фільтр, підсилювач високої частоти, який приєднаний до відповідного сигнального входу препроцесора, кожен з яких приєднаний до сигнального входу блока дискретних прецизійних атенюаторів, сигнальний вихід кожного з яких приєднаний до сигнального входу блока дискретних прецизійних ліній затримок, сигнальний вихід кожної з яких приєднаний до сигнального входу блока дискретних прецизійних фазообертачів, сигнальний вихід кожного з яких приєднаний до входу відповідного спрямованого відгалужувача, перші виходи яких відповідно приєднані до входів перших трьох дільників потужності, їх другі виходи відповідно приєднані до трьох виходів препроцесора, а у третіх виходах в усіх трьох спрямованих відгалужувачів розміщені узгоджені навантаження, перші виходи перших трьох дільників потужності приєднані до відповідних каскадно з'єднаних амплітудного детектора та аналого-цифрового перетворювача, другі виходи - з входами четвертого, п'ятого і шостого дільників потужності, а у третіх виходах в усіх шести дільників потужності розміщені узгоджені навантаження, перші виходи четвертого і шостого дільників потужності з'єднані з першими входами першого і третього широкодіапазонного фазометра, їх другі виходи - з входами другого широкодіапазонного фазометра, а виходи п'ятого дільника потужності - з другими входами першого і третього широкодіапазонного фазометра, виходи усіх трьох широкодіапазонних фазометрів з'єднані відповідно з входами четвертого, п'ятого і шостого аналого-цифрових перетворювачів, дві шини вводу цифрових даних у мікропроцесор через перший і другий вхід з'єднані відповідно з виходами першого, другого і третього аналого-цифрових перетворювачів та четвертого, п'ятого і шостого, четвертий вхід препроцесора приєднаний до третього входу мікропроцесора, перша шина виводу цифрових даних від першого виходу мікропроцесора з'єднана з керуючими входами трьох блоків дискретних прецизійних атенюаторів, друга та третя шини з другого та третього виходу мікропроцесора - відповідно з керуючими входами блоків дискретних прецизійних ліній затримок та фазообертачів, кожен з трьох виходів препроцесора приєднаний до відповідного багатоканального дільника потужності, перші S виходів яких приєднані до перших входів відповідних S груп по три множники частоти, до других входів яких приєднані виходи багатоканального генератора високочастотних коливань, останні виходи багатоканальних дільників потужності приєднані до входу суматора основного каналу, виходи кожного з трьох певної групи множників частот приєднані до відповідного суматора додаткового каналу, виходи першого суматора додаткового каналу та суматора основного каналу приєднані до входів першого множника сигналів, вихід якого та вихід наступного суматора додаткового каналу приєднані до входів наступного множника сигналів, і так до останнього суматора додаткового каналу, тобто до входів S-ого множника сигналів приєднані виходи S-ого суматора додаткового каналу та S-1-ого множника сигналів, вихід S-ого множника сигналів приєднаний до входу спрямованого відгалужувача, перший вихід якого приєднаний до входу детектора, вихід детектора приєднаний до четвертого входу препроцесора.

Текст

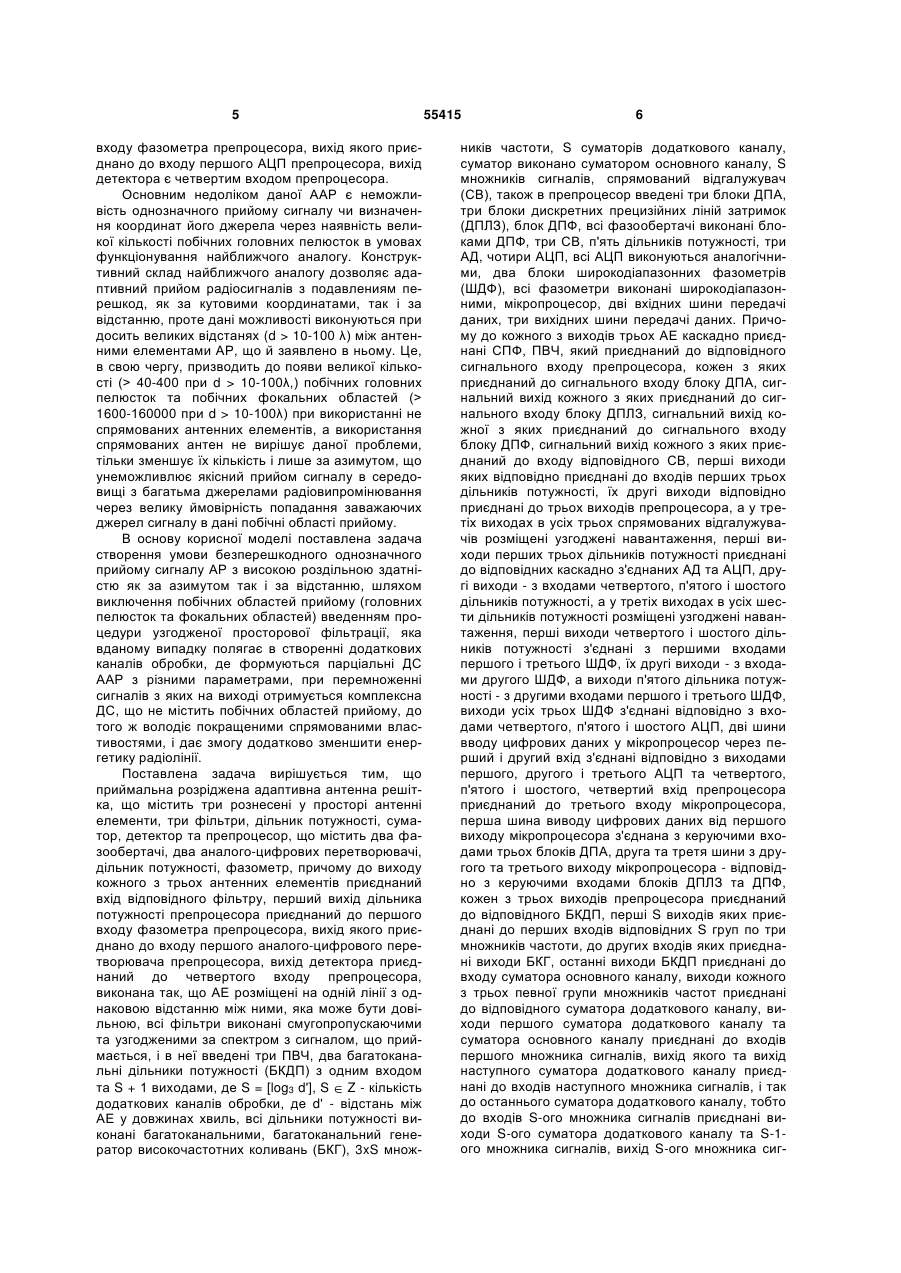

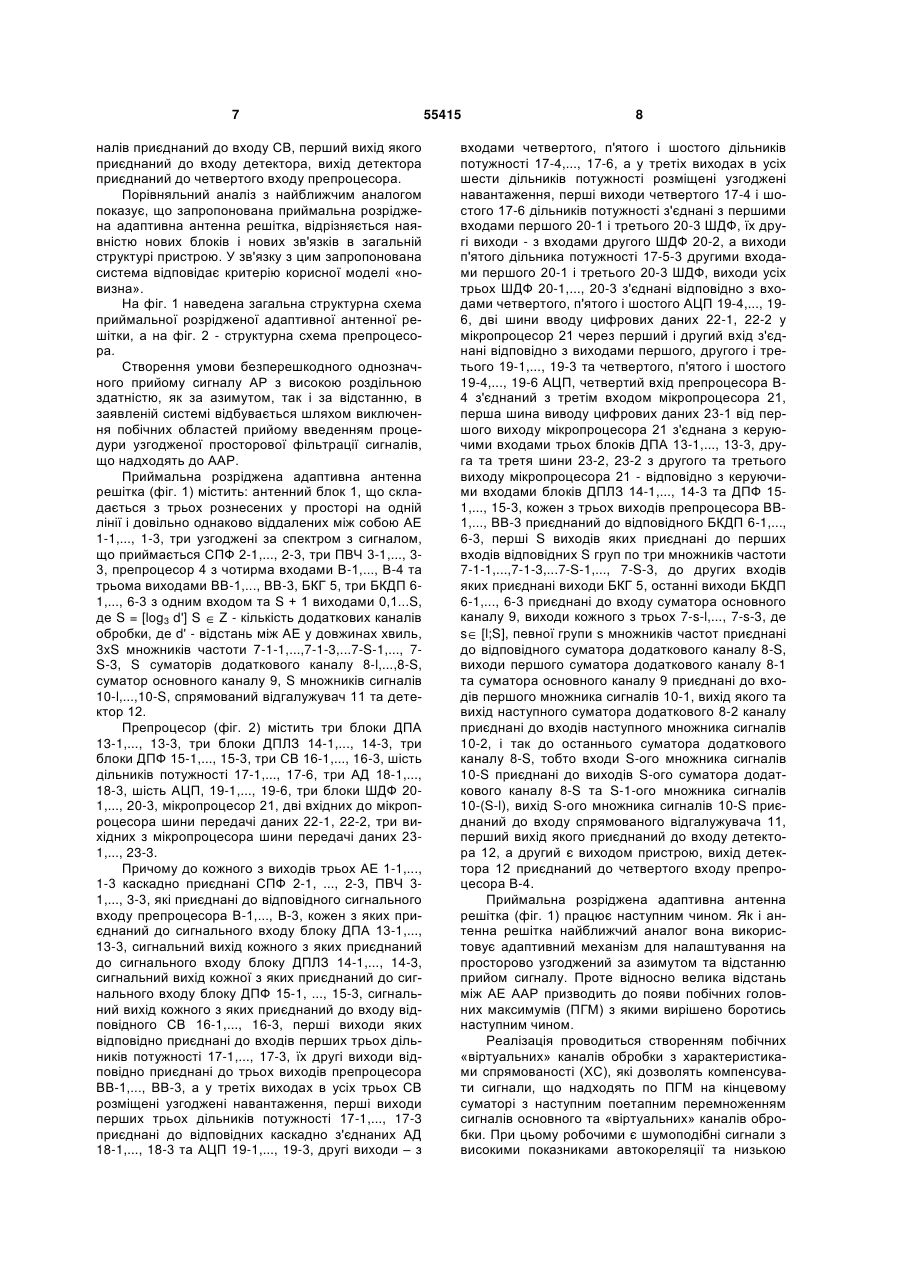

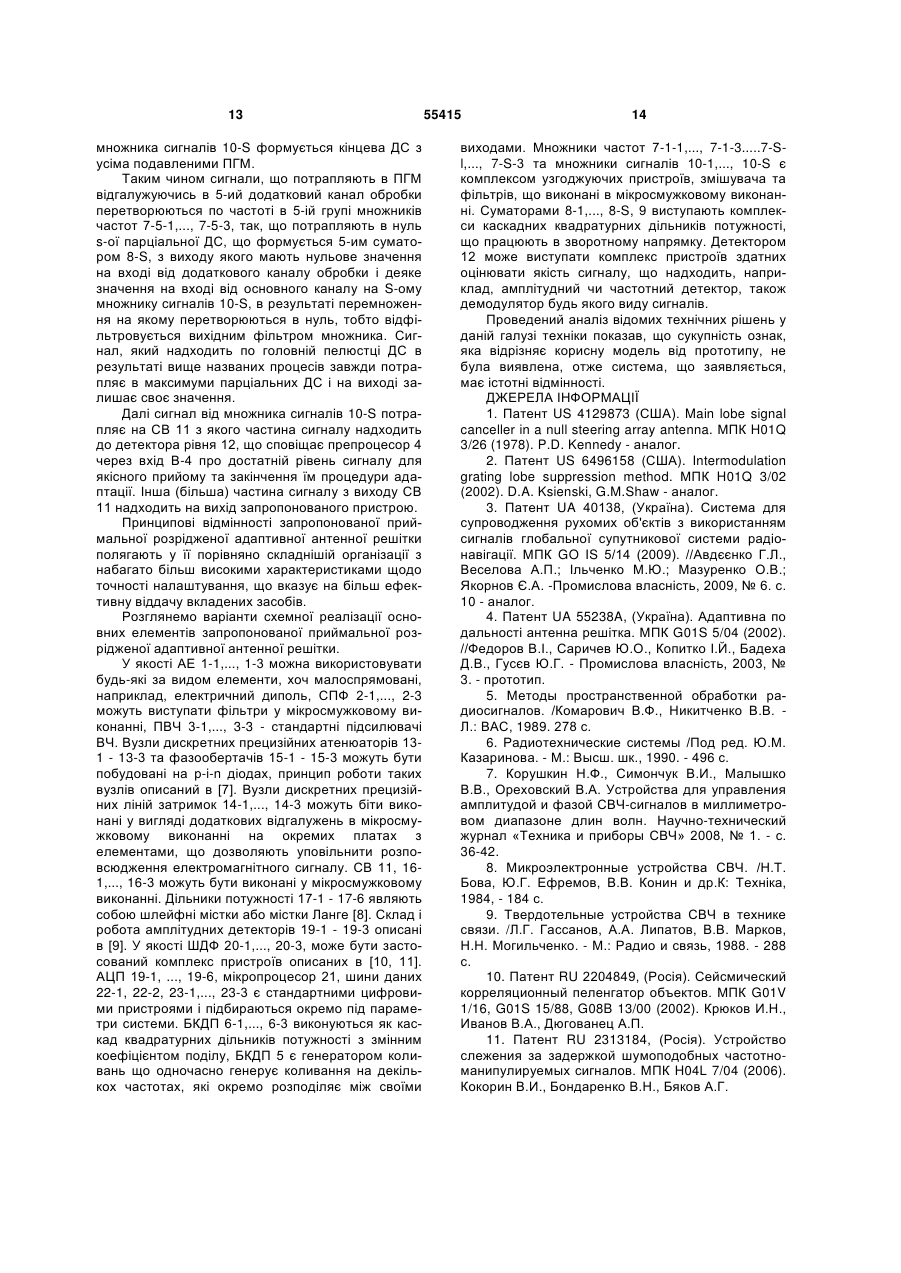

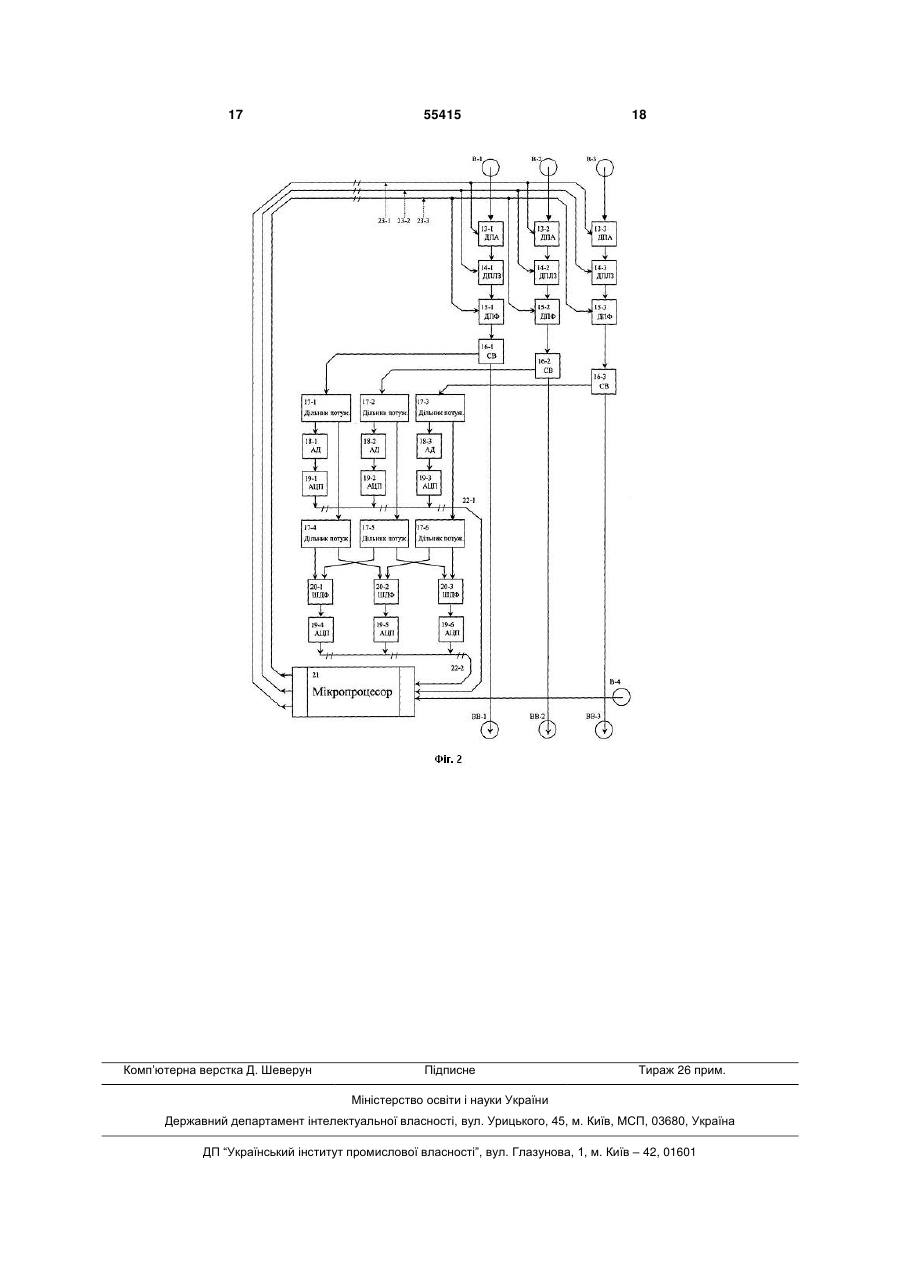

Приймальна розріджена адаптивна антенна решітка, що містить три рознесені у просторі антенні елементи, три фільтри, дільник потужності, суматор, детектор та препроцесор, що містить два фазообертачі, два аналого-цифрових перетворювачі, дільник потужності, фазометр, причому до виходу кожного з трьох антенних елементів приєднаний вхід відповідного фільтра, перший вихід дільника потужності препроцесора приєднаний до першого входу фазометра препроцесора, вихід якого приєднано до входу першого аналогоцифрового перетворювача препроцесора, вихід детектора приєднаний до четвертого входу препроцесора, яка відрізняється тим, що антенні елементи розміщені на одній лінії з однаковою відстанню між ними, яка може бути довільною, всі фільтри виконані смугопропускаючими та узгодженими за спектром з сигналом, що приймається, і в неї введені три підсилювачі високої частоти, два багатоканальні дільники потужності з одним входом та S+1 виходами, де S = [log3 d'] S Z - кількість додаткових каналів обробки, де d' - відстань між антенними елементами у довжинах хвиль, всі дільники потужності виконані багатоканальними, багатоканальний генератор високочастотних коливань, 3xS множників частоти, S суматорів додаткового каналу, суматор виконано суматором основного каналу, S множників сигналів, спрямований відгалужувач, також в препроцесор введені три блоки дискретних прецизійних атенюаторів, три блоки дискретних прецизійних ліній затримок, блок дискретних прецизійних фазообертачів, всі фазообертачі виконані блоками дискретних прецизійних фазообертачів, три спрямованих відгалужувачі, п'ять дільників потужності, три амплітудних детектори, чотири аналого-цифрових перетворювачі, всі аналого-цифрові перетворюва 2 (19) 1 3 55415 4 шини з другого та третього виходу мікропроцесора - відповідно з керуючими входами блоків дискретних прецизійних ліній затримок та фазообертачів, кожен з трьох виходів препроцесора приєднаний до відповідного багатоканального дільника потужності, перші S виходів яких приєднані до перших входів відповідних S груп по три множники частоти, до других входів яких приєднані виходи багатоканального генератора високочастотних коливань, останні виходи багатоканальних дільників потужності приєднані до входу суматора основного каналу, виходи кожного з трьох певної групи множників частот приєднані до відповідного суматора додаткового каналу, виходи першого суматора додаткового каналу та суматора основного каналу приєднані до входів першого множника сигналів, вихід якого та вихід наступного суматора додаткового каналу приєднані до входів наступного множника сигналів, і так до останнього суматора додаткового каналу, тобто до входів S-ого множника сигналів приєднані виходи S-ого суматора додаткового каналу та S-1-ого множника сигналів, вихід S-ого множника сигналів приєднаний до входу спрямованого відгалужувача, перший вихід якого приєднаний до входу детектора, вихід детектора приєднаний до четвертого входу препроцесора. Корисна модель відноситься до радіотехніки, зокрема до антенних вузлів систем прийому радіосигналів та реєстрації інформації про їх параметри та зміст, і може бути застосований як елемент станцій радіолокації, радіоастрономії, зв'язку, в особливості зв'язку на великі відстані або зв'язку, що використовує кероване просторове розділення сигналу як за кутовими координатами, так і за відстанню. Відома адаптивна антенна система (АС) з придушенням перешкод в головній пелюстці діаграми спрямованості (ДС) [1], принцип дії якої заснований на формуванні мінімумів у напрямку дії перешкод, якщо ті надходять з головної пелюстки ДС, при цьому зберігається значення ДС у напрямку приходу корисного сигналу. Основним недоліком цієї адаптивної АС (ААС) є необхідність розрізняння кутових координат джерела корисного сигналу і перешкоди в межах головного пелюстка ДС. У цьому випадку, якщо напрямок головного пелюстка ДС приймальної АС на зазначені джерела знаходяться поблизу однієї прямої, такі ААС непрацездатні. Розв'язання даної проблеми збільшенням відстані між антенними елементами є неприпустимим через появу побічних головних пелюсток ДС. Відомий інтермодуляційний подавлювач побічних головних пелюсток для ААС [2], принцип дії якого заснований на формуванні декількох сумарно-різницевих парціальних ДС на різних частотах таким чином, щоб на виході ААС кінцева ДС не мала в своєму складі побічних головних пелюсток. Недоліками даного пристрою є необхідність використання узгодженого за конструкцією до даного пристрою приймача, що не описаний, а також широкого спектру частот, відсутня можливість подавити всі побічні головні пелюстки при великій (d > 10-100λ, λ - довжина робочої хвилі радіосигналу) відстані між антенними елементами (АЕ), а також керованого розділення сигналів за відстанню. Відома система для супроводження рухомих об'єктів з використанням сигналів глобальної супутникової системи радіонавігації [3], що містить виявник, який містить лінійну антенну решітку (АР) з трьох елементів, три смугопропускаючі фільтри (СПФ), узгоджених за АЧХ з сигналом радіомаяка, три підсилювачі високої частоти (ПВЧ), три вузли дискретних прецизійних атенюаторів (ДПА), три вузли дискретних прецизійних фазообертачів (ДПФ), шість квадратурних дільників потужності, три амплітудних детектори (АД), шість аналогоцифрових перетворювачі (АЦП), три фазометри, мікропроцесор, дві шини вводу цифрових даних до мікропроцесора, дві шини виводу цифрових даних від мікропроцесора. Причому до кожного з виходів трьох антен лінійної АР каскадно під'єднані СПФ, ПВЧ, вузли ДПА та ДПФ, перші три дільники потужності, перший вихід кожного з трьох з'єднаний з каскадно з'єднаними АД та АЦП, другі виходи - з входами четвертого, п'ятого і шостого дільників потужності, а у третіх виходах в усіх шести дільників потужності розміщені узгоджені навантаження; перші виходи четвертого і шостого дільників потужності з'єднані з першими входами першого і третього фазометрів, їх другі виходи - з входами другого фазометра, а виходи п'ятого дільника потужності з другими входами першого і третього фазометрів, виходи усіх трьох фазометрів з'єднані відповідно з входами четвертого, п'ятого і шостого АЦП; дві шини вводу цифрових даних у мікропроцесор з'єднані відповідно з виходами першого, другого і третього та четвертого, п'ятого і шостого АЦП; перша та друга шина виводу цифрових даних від мікропроцесора відповідно з'єднана з вузлами ДПА та ДПФ. Недоліками даної системи є неможливість прийому сигналу, що містить дані з подальшою їх екстракцією (демодуляцією сигналу), а лише можливість визначати координати розміщення його джерела, неможливість однозначного визначення координат джерела (азимут, відстань між ААС та джерелом) при великій (d > 10-100λ) відстані між антенними елементами для вірного спрацювання механізму адаптації ДС ААС. Найбільш близькою за технічною сутністю і функціональністю до запропонованої є адаптивна по дальності антенна решітка [4]. Відома адаптивна антенна решітка (ААР), обрана в якості найближчого аналогу, містить три рознесені у просторі АЕ, три фільтри, дільник потужності, суматор, детектор та препроцесор, що містить два фазообертачі, два АЦП, дільник потужності, фазометр, причому до виходу кожного з трьох АЕ приєднаний вхід відповідного фільтру, перший вихід дільника потужності препроцесора приєднаний до першого 5 входу фазометра препроцесора, вихід якого приєднано до входу першого АЦП препроцесора, вихід детектора є четвертим входом препроцесора. Основним недоліком даної ААР є неможливість однозначного прийому сигналу чи визначення координат його джерела через наявність великої кількості побічних головних пелюсток в умовах функціонування найближчого аналогу. Конструктивний склад найближчого аналогу дозволяє адаптивний прийом радіосигналів з подавлениям перешкод, як за кутовими координатами, так і за відстанню, проте дані можливості виконуються при досить великих відстанях (d > 10-100 λ) між антенними елементами АР, що й заявлено в ньому. Це, в свою чергу, призводить до появи великої кількості (> 40-400 при d > 10-100λ,) побічних головних пелюсток та побічних фокальних областей (> 1600-160000 при d > 10-100λ) при використанні не спрямованих антенних елементів, а використання спрямованих антен не вирішує даної проблеми, тільки зменшує їх кількість і лише за азимутом, що унеможливлює якісний прийом сигналу в середовищі з багатьма джерелами радіовипромінювання через велику ймовірність попадання заважаючих джерел сигналу в дані побічні області прийому. В основу корисної моделі поставлена задача створення умови безперешкодного однозначного прийому сигналу АР з високою роздільною здатністю як за азимутом так і за відстанню, шляхом виключення побічних областей прийому (головних пелюсток та фокальних областей) введенням процедури узгодженої просторової фільтрації, яка вданому випадку полягає в створенні додаткових каналів обробки, де формуються парціальні ДС ААР з різними параметрами, при перемноженні сигналів з яких на виході отримується комплексна ДС, що не містить побічних областей прийому, до того ж володіє покращеними спрямованими властивостями, і дає змогу додатково зменшити енергетику радіолінії. Поставлена задача вирішується тим, що приймальна розріджена адаптивна антенна решітка, що містить три рознесені у просторі антенні елементи, три фільтри, дільник потужності, суматор, детектор та препроцесор, що містить два фазообертачі, два аналого-цифрових перетворювачі, дільник потужності, фазометр, причому до виходу кожного з трьох антенних елементів приєднаний вхід відповідного фільтру, перший вихід дільника потужності препроцесора приєднаний до першого входу фазометра препроцесора, вихід якого приєднано до входу першого аналого-цифрового перетворювача препроцесора, вихід детектора приєднаний до четвертого входу препроцесора, виконана так, що АЕ розміщені на одній лінії з однаковою відстанню між ними, яка може бути довільною, всі фільтри виконані смугопропускаючими та узгодженими за спектром з сигналом, що приймається, і в неї введені три ПВЧ, два багатоканальні дільники потужності (БКДП) з одним входом та S + 1 виходами, де S = [log3 d'], S Z - кількість додаткових каналів обробки, де d' - відстань між АЕ у довжинах хвиль, всі дільники потужності виконані багатоканальними, багатоканальний генератор високочастотних коливань (БКГ), 3xS множ 55415 6 ників частоти, S суматорів додаткового каналу, суматор виконано суматором основного каналу, S множників сигналів, спрямований відгалужувач (СВ), також в препроцесор введені три блоки ДПА, три блоки дискретних прецизійних ліній затримок (ДПЛЗ), блок ДПФ, всі фазообертачі виконані блоками ДПФ, три СВ, п'ять дільників потужності, три АД, чотири АЦП, всі АЦП виконуються аналогічними, два блоки широкодіапазонних фазометрів (ШДФ), всі фазометри виконані широкодіапазонними, мікропроцесор, дві вхідних шини передачі даних, три вихідних шини передачі даних. Причому до кожного з виходів трьох АЕ каскадно приєднані СПФ, ПВЧ, який приєднаний до відповідного сигнального входу препроцесора, кожен з яких приєднаний до сигнального входу блоку ДПА, сигнальний вихід кожного з яких приєднаний до сигнального входу блоку ДПЛЗ, сигнальний вихід кожної з яких приєднаний до сигнального входу блоку ДПФ, сигнальний вихід кожного з яких приєднаний до входу відповідного СВ, перші виходи яких відповідно приєднані до входів перших трьох дільників потужності, їх другі виходи відповідно приєднані до трьох виходів препроцесора, а у третіх виходах в усіх трьох спрямованих відгалужувачів розміщені узгоджені навантаження, перші виходи перших трьох дільників потужності приєднані до відповідних каскадно з'єднаних АД та АЦП, другі виходи - з входами четвертого, п'ятого і шостого дільників потужності, а у третіх виходах в усіх шести дільників потужності розміщені узгоджені навантаження, перші виходи четвертого і шостого дільників потужності з'єднані з першими входами першого і третього ШДФ, їх другі виходи - з входами другого ШДФ, а виходи п'ятого дільника потужності - з другими входами першого і третього ШДФ, виходи усіх трьох ШДФ з'єднані відповідно з входами четвертого, п'ятого і шостого АЦП, дві шини вводу цифрових даних у мікропроцесор через перший і другий вхід з'єднані відповідно з виходами першого, другого і третього АЦП та четвертого, п'ятого і шостого, четвертий вхід препроцесора приєднаний до третього входу мікропроцесора, перша шина виводу цифрових даних від першого виходу мікропроцесора з'єднана з керуючими входами трьох блоків ДПА, друга та третя шини з другого та третього виходу мікропроцесора - відповідно з керуючими входами блоків ДПЛЗ та ДПФ, кожен з трьох виходів препроцесора приєднаний до відповідного БКДП, перші S виходів яких приєднані до перших входів відповідних S груп по три множників частоти, до других входів яких приєднані виходи БКГ, останні виходи БКДП приєднані до входу суматора основного каналу, виходи кожного з трьох певної групи множників частот приєднані до відповідного суматора додаткового каналу, виходи першого суматора додаткового каналу та суматора основного каналу приєднані до входів першого множника сигналів, вихід якого та вихід наступного суматора додаткового каналу приєднані до входів наступного множника сигналів, і так до останнього суматора додаткового каналу, тобто до входів S-ого множника сигналів приєднані виходи S-ого суматора додаткового каналу та S-1ого множника сигналів, вихід S-ого множника сиг 7 налів приєднаний до входу СВ, перший вихід якого приєднаний до входу детектора, вихід детектора приєднаний до четвертого входу препроцесора. Порівняльний аналіз з найближчим аналогом показує, що запропонована приймальна розріджена адаптивна антенна решітка, відрізняється наявністю нових блоків і нових зв'язків в загальній структурі пристрою. У зв'язку з цим запропонована система відповідає критерію корисної моделі «новизна». На фіг. 1 наведена загальна структурна схема приймальної розрідженої адаптивної антенної решітки, а на фіг. 2 - структурна схема препроцесора. Створення умови безперешкодного однозначного прийому сигналу АР з високою роздільною здатністю, як за азимутом, так і за відстанню, в заявленій системі відбувається шляхом виключення побічних областей прийому введенням процедури узгодженої просторової фільтрації сигналів, що надходять до ААР. Приймальна розріджена адаптивна антенна решітка (фіг. 1) містить: антенний блок 1, що складається з трьох рознесених у просторі на одній лінії і довільно однаково віддалених між собою АЕ 1-1,..., 1-3, три узгоджені за спектром з сигналом, що приймається СПФ 2-1,..., 2-3, три ПВЧ 3-1,..., 33, препроцесор 4 з чотирма входами В-1,..., В-4 та трьома виходами ВВ-1,..., ВВ-3, БКГ 5, три БКДП 61,..., 6-3 з одним входом та S + 1 виходами 0,1...S, де S = [log3 d'] S Z - кількість додаткових каналів обробки, де d' - відстань між АЕ у довжинах хвиль, 3xS множників частоти 7-1-1,...,7-1-3,...7-S-1,..., 7S-3, S суматорів додаткового каналу 8-l,...,8-S, суматор основного каналу 9, S множників сигналів 10-l,...,10-S, спрямований відгалужувач 11 та детектор 12. Препроцесор (фіг. 2) містить три блоки ДПА 13-1,..., 13-3, три блоки ДПЛЗ 14-1,..., 14-3, три блоки ДПФ 15-1,..., 15-3, три СВ 16-1,..., 16-3, шість дільників потужності 17-1,..., 17-6, три АД 18-1,..., 18-3, шість АЦП, 19-1,..., 19-6, три блоки ШДФ 201,..., 20-3, мікропроцесор 21, дві вхідних до мікропроцесора шини передачі даних 22-1, 22-2, три вихідних з мікропроцесора шини передачі даних 231,..., 23-3. Причому до кожного з виходів трьох АЕ 1-1,..., 1-3 каскадно приєднані СПФ 2-1, ..., 2-3, ПВЧ 31,..., 3-3, які приєднані до відповідного сигнального входу препроцесора В-1,..., В-3, кожен з яких приєднаний до сигнального входу блоку ДПА 13-1,..., 13-3, сигнальний вихід кожного з яких приєднаний до сигнального входу блоку ДПЛЗ 14-1,..., 14-3, сигнальний вихід кожної з яких приєднаний до сигнального входу блоку ДПФ 15-1, ..., 15-3, сигнальний вихід кожного з яких приєднаний до входу відповідного СВ 16-1,..., 16-3, перші виходи яких відповідно приєднані до входів перших трьох дільників потужності 17-1,..., 17-3, їх другі виходи відповідно приєднані до трьох виходів препроцесора ВВ-1,..., ВВ-3, а у третіх виходах в усіх трьох СВ розміщені узгоджені навантаження, перші виходи перших трьох дільників потужності 17-1,..., 17-3 приєднані до відповідних каскадно з'єднаних АД 18-1,..., 18-3 та АЦП 19-1,..., 19-3, другі виходи – з 55415 8 входами четвертого, п'ятого і шостого дільників потужності 17-4,..., 17-6, а у третіх виходах в усіх шести дільників потужності розміщені узгоджені навантаження, перші виходи четвертого 17-4 і шостого 17-6 дільників потужності з'єднані з першими входами першого 20-1 і третього 20-3 ШДФ, їх другі виходи - з входами другого ШДФ 20-2, а виходи п'ятого дільника потужності 17-5-3 другими входами першого 20-1 і третього 20-3 ШДФ, виходи усіх трьох ШДФ 20-1,..., 20-3 з'єднані відповідно з входами четвертого, п'ятого і шостого АЦП 19-4,..., 196, дві шини вводу цифрових даних 22-1, 22-2 у мікропроцесор 21 через перший і другий вхід з'єднані відповідно з виходами першого, другого і третього 19-1,..., 19-3 та четвертого, п'ятого і шостого 19-4,..., 19-6 АЦП, четвертий вхід препроцесора В4 з'єднаний з третім входом мікропроцесора 21, перша шина виводу цифрових даних 23-1 від першого виходу мікропроцесора 21 з'єднана з керуючими входами трьох блоків ДПА 13-1,..., 13-3, друга та третя шини 23-2, 23-2 з другого та третього виходу мікропроцесора 21 - відповідно з керуючими входами блоків ДПЛЗ 14-1,..., 14-3 та ДПФ 151,..., 15-3, кожен з трьох виходів препроцесора ВВ1,..., ВВ-3 приєднаний до відповідного БКДП 6-1,..., 6-3, перші S виходів яких приєднані до перших входів відповідних S груп по три множників частоти 7-1-1,...,7-1-3,...7-S-1,..., 7-S-3, до других входів яких приєднані виходи БКГ 5, останні виходи БКДП 6-1,..., 6-3 приєднані до входу суматора основного каналу 9, виходи кожного з трьох 7-s-l,..., 7-s-3, де s [l;S], певної групи s множників частот приєднані до відповідного суматора додаткового каналу 8-S, виходи першого суматора додаткового каналу 8-1 та суматора основного каналу 9 приєднані до входів першого множника сигналів 10-1, вихід якого та вихід наступного суматора додаткового 8-2 каналу приєднані до входів наступного множника сигналів 10-2, і так до останнього суматора додаткового каналу 8-S, тобто входи S-ого множника сигналів 10-S приєднані до виходів S-ого суматора додаткового каналу 8-S та S-1-ого множника сигналів 10-(S-l), вихід S-ого множника сигналів 10-S приєднаний до входу спрямованого відгалужувача 11, перший вихід якого приєднаний до входу детектора 12, а другий є виходом пристрою, вихід детектора 12 приєднаний до четвертого входу препроцесора В-4. Приймальна розріджена адаптивна антенна решітка (фіг. 1) працює наступним чином. Як і антенна решітка найближчий аналог вона використовує адаптивний механізм для налаштування на просторово узгоджений за азимутом та відстанню прийом сигналу. Проте відносно велика відстань між АЕ ААР призводить до появи побічних головних максимумів (ПГМ) з якими вирішено боротись наступним чином. Реалізація проводиться створенням побічних «віртуальних» каналів обробки з характеристиками спрямованості (ХС), які дозволять компенсувати сигнали, що надходять по ПГМ на кінцевому суматорі з наступним поетапним перемноженням сигналів основного та «віртуальних» каналів обробки. При цьому робочими є шумоподібні сигнали з високими показниками автокореляції та низькою 9 55415 взаємною кореляцією з іншими сигналами. Для досягнення вищенаведеної умови ХС «віртуальних» каналів повинні мати нулі в координатах відповідного розміщення ПГМ. Для простих схем просторово часової обробки сигналу (ПЧОС), відповідно [5, 6], даний ефект досягається пониженням частоти у «віртуальних» каналах обробки кратно основній частоті. Кути розташування головних максимумів, нулів та максимумів бокових пелюсток є аргументами функції ХС АР: N d sin sin sin N d' sin 2 F d sin N sin d' sin N sin 2 , (1) де N- кількість АЕ, β = 2π/λ - хвильовий коефіцієнт. Головні максимуми розташовані в кутах θгол.макс., де періодичний сигнал приймається синфазно від всіх АЕ не зважаючи на їх відстань до фазового центру АР. Вираз (1) матиме максимум при значеннях аргументу, коли його знаменник прямує до нуля. Тобто, коли sin(πk sin(θ)) = 0. Тоді в області дійсних значень аргументу гол. макс. arcsin( n ) d' ,n d' ; d' або n d'; d' 0, n Z , (2) Кількість головних максимумів (головного, заднього, побічних) визначається кількістю періодів сигналу, що проходять через сусідні АЕ АР в усьому діапазоні сканування, тобто K ГМ 4 max n 2sign d' max n , n d'; d' 0, n Z . (3) Нулі ХС АР матиме в значеннях аргументу θ0 виразу (1) коли: sin N d' sin 0 sin d' sin 0 , де перший вираз даної системи визначає всі можливі значення, а другий область допустимих значень, або, як відомо (2), розміщення головних максимумів. Тоді 0 arcsin( m ) Nd ' ,m Nd '; Nd ' / N n або m Nd '; d' 0, m Z , (4) Кількість нулів в усьому діапазоні сканування визначається як K0 4 max m 2sign Nd ' max m K , m Nd '; m Z ГМ . (5) Загальна область значень нулів і головних максимумів спільна, що вказує на математичну доцільність використання даного методу боротьби з ПГМ. Тобто перенесення сигналу в каналах обробки на частоту кратну частоті основного каналу дозволить на виході подавити всі ПГМ. Тому наступною є задача узгодження областей значень нулів і ПГМ для якнайбільшого їх подавления. Дослідивши спільну область значень нулів та головних максимумів (2, 4) виразу (1) слід зробити висновок, що в області реальних значень вони слідують від головного максимуму як за часовою стрілкою, так і проти наступним чином: головний максимум, N - 1 нулів (N - 2 бокових пелюсток), побічний головний максимум, N - 1 нулів, і т.д. до заднього головного максимуму. 10 Таким чином, для подавления якомога більшої кількості ПГМ необхідно в каналі обробки понизити частоту настільки, щоб область значень нулів або їх номерів m [- Nd'; Nd'], у якій кожним N-им елементом є головний максимум, співпала з областю значень головних максимумів або їх номерів n [d';d']. Тобто понижати частоту необхідно в стільки разів з скількох елементів N складається еквідистантна прямолінійна АР (ЕПЛАР). При цьому кожен N-й ПГМ якщо d' > N залишиться не подавленим, інакше всі ПГМ подавлюються. При інших частотних перетвореннях в каналах обробки не вдається подавити більшу кількість ПГМ та зменшити їх рівень, тому даний випадок є найоптимальнішим. При d' > N необхідно використовувати більше одного каналу обробки в запропонованому схематичному рішенні, згідно фіг. 1. Тому знайдемо необхідну кількість каналів для повного подавления ПГМ. З вище згаданого відомо, що при d' > N з одним каналом обробки залишається кожен N-й ПГМ, тому аналогічно підходу, що використаний для визначення частоти перетворення в першому каналі обробки в другому каналі обробки частоту треба понизити, ще в N раз, тобто в N2 раз відносно основного каналу. При цьому кожен N2 -й ПГМ якщо d' > N2 залишиться не подавленим, інакше всі ПГМ подавлюються. Для подальшого подавления потрібно додавати необхідну кількість каналів понижуючи в кожному з них частоту в N разів відносно попереднього. Тобто для подавления всіх ПГМ необхідно S1 каналів обробки з частотами в NS, s [1;S], s N раз меншими ніж в основному каналі, так, щоб d' ≤ NS. Тоді необхідна кількість каналів визначається як більше ціле (округлене вверх) виразу S logN d' , S Z . (6) Слід зауважити, що ширина смуги сигналу Δf та основна робоча частота f0 вносять обмеження на кількість каналів виразом f0 d f0 NS d' f f . (7) Звідси видно, що оптимальним для такого схематичного рішення є випадок, коли k = NS, s N. Наприклад, для 3-х (N = 3) елементної ЕПЛАР з d' = 1000 (d = 1000λ,) необхідно S = [log31000] = [6,29] = 7 каналів з частотами в Ns, s [і;7] раз меншими відносно основного каналу. Також до функціонального недоліку ААР прототипу слід віднести схему адаптації, що реалізовано в препроцесорі. В схемі не враховані особливості узгодженого просторового прийому за відстанню, тобто властивості функціонування ААР в зоні дифракції Френеля, а саме різна амплітуда в каналах від кожного АЕ та велика різниця фаз (запізнення) сигналів. Тому процес реалізований в схемі препроцесора ААР прототипу, що полягав в поступовому підборі параметрів адаптації з контролюючим зворотним зв'язком через детектор на виході є недоцільним через тривалий період адаптації, і в запропонованій схемі замінений на безпосереднє визначення амплітуди та повної різниці фаз (затримки) сигналів від різних АЕ з наступною 11 обробкою даних параметрів і налаштуванні відповідних атенюаторів, ліній затримок та фазообертачів для якісного прийому сигналу. Також виконання дільників потужності 17-1 17-6 квадратурними і розміщення у третіх виходах в усіх шести дільників потужності узгоджених навантажень зменшує вплив на роботу препроцесора відбитих сигналів від вузлів, що стоять після дільників, та шумів, що генеруватимуться елементами узгодження. Виходячи з вище наведених тверджень принцип роботи запропонованого конструктивного рішення наступний. Сигнали що надійшли на три АЕ 1-1,..., 1-3 надходять в смугопропускаючі фільтри 2-1,..., 2-3, далі в підсилювачі високої частоти 31,..., 3-3, на виході яких отримуємо сигнали готові до ПЧОС. Далі сигнали надходять до відповідного сигнального входу препроцесора В-1,..., В-3, з яких потрапляють до сигнального входу блоку ДПА 131,..., 13-3, далі до сигнального входу блоку ДПЛЗ 14-1,..., 14-3, далі до сигнального входу блоку ДПФ 15-1,..., 15-3, причому поки ще процес адаптивного налаштування не почався блоки ДПА, ДПЛЗ та ДПФ знаходяться в початковому (нульовому) стані. Далі сигнали потрапляють входу відповідного СВ 16-1,..., 16-3, з перших виходів яких відповідно надходять до квадратурних дільників 17-1 - 17-3 з яких половина сигналів надходить у АД 18-1 ... 183 з яких інформація про амплітуди сигналів у каналах виділяється АЦП 19-1 ... 19-3 і надходить в мікропроцесор 21 через шину вводу 22-1, а інша частина сигналів з дільників 17-1 ... 17-3 надходить до дільників 17-4 ... 17-3, які розподіляють сигнали між ШДФ 20-1 ... 20-3 з яких інформація про затримку сигналів в каналах виділяється в АЦП 19-4 ... 19-6 і надходить в мікропроцесор 21 через шину вводу 22-2. Далі мікропроцесор 21 аналізує інформацію про амплітуди в каналах від АЕ і в разі їх не ідентичності, визначає дані для корекції, при цьому дає команду на припинення визначення затримки сигналу до тих пір поки амплітуда на входах всіх АД 18-1 ... 18-3 не буде однаковою. Корекція амплітуд сигналів відбувається, шляхом їх зменшення відносно каналу у якому сигнал найслабший, під дією команд які надсилає мікропроцесор 21 до блоків ДПА 13-1 ... 13-3 через вивідну шину 23-1. Після встановлення блоків ДПА 13-1 ... 13-3 у відповідні значення та вичікування певного відрізку часу, що визначається часом проходження сигналу від ДПА 13-1 ... 13-3 до мікропроцесора 21 через ланку дільників 17-1 ... 17-6 та АД 18-1 ... 18-3, він знову починає процедуру визначення амплітуд у каналах, у разі рівності яких знімає блокування з процедури визначення затримки між сигналами, що надходять від різних АЕ 1-1 ... 1-3, інакше процедура повторюється. Далі мікропроцесор переходить до процесу визначення затримки між каналами від АЕ 1-1 ... 13, проте спостерігає за зміною амплітуд сигналів у каналах і у разі наявності даного процесу знову проводить процедуру корекції з блокуванням процедури визначення затримки. Процес визначення затримки полягає в визначенні ШДФ 20-1 - 20-3 повної фазової затримки з визначенням фазової 55415 12 затримки у межах періоду коливань та кількості періодів понад, інформація про що виділяється в АЦП 19-4 ... 19-6 і надходить в мікропроцесор 21 через шину вводу 22-2. Далі мікропроцесор 21 проводить обробку даної інформації, що включає процедуру перевірки на рівність суми різниці фаз між крайніми 1-1, 1-3 і центральним 1-2 АЕ до різниці фаз між крайніми елементами 1-1, 1-3, де у разі нерівності за правильні значення визначаємо середнє арифметичне значень, що прирівнюються, і до значення різниці фаз між крайніми 1-1, 1-3 і центральним 1-2 АЕ програмно додається четверть абсолютної похибки ((Δφ12+Δφ23-Δφ13)/4). Далі мікропроцесор 21 передає дані про компенсацію затримки в каналах від АЕ 1-1 ... 1-3 через шини 23-2, 23-3 до ДПЛЗ 14-1,..., 14-3 та ДПФ 151,..., 15-3 та вичікуючи необхідний час надходження сигналу від них назад знову проводить процедуру визначення та корекції затримки, до тих пір поки затримка в каналах буде близькою до нуля. Після корекції амплітуди та затримки мікропроцесор 21 все ще відслідковує стан амплітуд та затримки між каналами від АЕ 1-1 ... 1-3 до тих пір поки на його вхід не надійде сигнал через вхід препроцесора В-4 від детектора сигналу 12 який визначає його рівень на виході запропонованого пристрою про достатній для якісного прийому. Після корекції сигнали з ДПА 13-1,..., 13-3, через ДПЛЗ 14-1,..., 14-3, через ДПФ 15-1,..., 15-3, через СВ 16-1,..., 16-3 надходять на виходи препроцесора ВВ-1,..., ВВ-3 з яких потрапляють до БКДП 6-1,..., 6-3, що однаково розподіляють сигнали між своїми 5+1 виходами, кількість яких задовольняє умові подавления всіх ПГМ, згідно (6). З перших 5 виходів БКДП 6-1,..., 6-3, сигнали надходять до перших входів відповідних 5 груп по три множників частоти 7-1-1,...,7-1-3,...,7-S-l,..., 7-S-3, до других входів яких сигнали від БКГ 5, з останніх виходів БКДП 6-1,..., 6-3 сигнали надходять до входу суматора основного каналу 9. В кожній 5-ій групі множників частот 7-s-1,..., 7-s-3, де s є [1;S], s N, сигнал понижується по частоті в TV* раз, тобто сигнал з перших виходів БКДП 6-1,..., 6-3 надходить до множників частот 7-1-1,...,7-1-3, де понижується по частоті в N раз, а сигнал з 5-их виходів БКДП 6-1,..., 6-3 надходить до множників частот 7-S-l,...,7-S-3, де понижується по частоті в Ns раз. Далі з виходів кожного з трьох 7-5-1,..., 7-53, де s [1;S], певної групи 5 множників частот сигнали надходять до відповідного суматора додаткового каналу 8-5, де формуються відповідні парціальні ДС. Далі з виходу першого суматора додаткового каналу 8-1 та суматора основного каналу 9 сигнали надходять до першого множника сигналів 10-1, де сигнали перемножуючись утворюють ДС з виключеною першою групою ПГМ, далі сигнал від якого та виходу наступного суматора додаткового каналу 8-2 надходить на вхід наступного множника сигналів 10-2, де відбувається процедура перемноження сигналів з аналогічним попередньому множнику ефектом, і так до останнього суматора додаткового каналу 8-S, тобто на вхід S-ого множника сигналів 10-S надходять сигнали S-ого суматора додаткового каналу 8-S та S-1-ого множника сигналів 10-(S-l). На виході 5-ого 13 множника сигналів 10-S формується кінцева ДС з усіма подавленими ПГМ. Таким чином сигнали, що потрапляють в ПГМ відгалужуючись в 5-ий додатковий канал обробки перетворюються по частоті в 5-ій групі множників частот 7-5-1,..., 7-5-3, так, що потрапляють в нуль s-ої парціальної ДС, що формується 5-им суматором 8-S, з виходу якого мають нульове значення на вході від додаткового каналу обробки і деяке значення на вході від основного каналу на S-ому множнику сигналів 10-S, в результаті перемноження на якому перетворюються в нуль, тобто відфільтровується вихідним фільтром множника. Сигнал, який надходить по головній пелюстці ДС в результаті вище названих процесів завжди потрапляє в максимуми парціальних ДС і на виході залишає своє значення. Далі сигнал від множника сигналів 10-S потрапляє на СВ 11 з якого частина сигналу надходить до детектора рівня 12, що сповіщає препроцесор 4 через вхід В-4 про достатній рівень сигналу для якісного прийому та закінчення їм процедури адаптації. Інша (більша) частина сигналу з виходу СВ 11 надходить на вихід запропонованого пристрою. Принципові відмінності запропонованої приймальної розрідженої адаптивної антенної решітки полягають у її порівняно складнішій організації з набагато більш високими характеристиками щодо точності налаштування, що вказує на більш ефективну віддачу вкладених засобів. Розглянемо варіанти схемної реалізації основних елементів запропонованої приймальної розрідженої адаптивної антенної решітки. У якості АЕ 1-1,..., 1-3 можна використовувати будь-які за видом елементи, хоч малоспрямовані, наприклад, електричний диполь, СПФ 2-1,..., 2-3 можуть виступати фільтри у мікросмужковому виконанні, ПВЧ 3-1,..., 3-3 - стандартні підсилювачі ВЧ. Вузли дискретних прецизійних атенюаторів 131 - 13-3 та фазообертачів 15-1 - 15-3 можуть бути побудовані на р-i-n діодах, принцип роботи таких вузлів описаний в [7]. Вузли дискретних прецизійних ліній затримок 14-1,..., 14-3 можуть біти виконані у вигляді додаткових відгалужень в мікросмужковому виконанні на окремих платах з елементами, що дозволяють уповільнити розповсюдження електромагнітного сигналу. СВ 11, 161,..., 16-3 можуть бути виконані у мікросмужковому виконанні. Дільники потужності 17-1 - 17-6 являють собою шлейфні містки або містки Ланге [8]. Склад і робота амплітудних детекторів 19-1 - 19-3 описані в [9]. У якості ШДФ 20-1,..., 20-3, може бути застосований комплекс пристроїв описаних в [10, 11]. АЦП 19-1, ..., 19-6, мікропроцесор 21, шини даних 22-1, 22-2, 23-1,..., 23-3 є стандартними цифровими пристроями і підбираються окремо під параметри системи. БКДП 6-1,..., 6-3 виконуються як каскад квадратурних дільників потужності з змінним коефіцієнтом поділу, БКДП 5 є генератором коливань що одночасно генерує коливання на декількох частотах, які окремо розподіляє між своїми 55415 14 виходами. Множники частот 7-1-1,..., 7-1-3.....7-Sl,..., 7-S-3 та множники сигналів 10-1,..., 10-S є комплексом узгоджуючих пристроїв, змішувача та фільтрів, що виконані в мікросмужковому виконанні. Суматорами 8-1,..., 8-S, 9 виступають комплекси каскадних квадратурних дільників потужності, що працюють в зворотному напрямку. Детектором 12 може виступати комплекс пристроїв здатних оцінювати якість сигналу, що надходить, наприклад, амплітудний чи частотний детектор, також демодулятор будь якого виду сигналів. Проведений аналіз відомих технічних рішень у даній галузі техніки показав, що сукупність ознак, яка відрізняє корисну модель від прототипу, не була виявлена, отже система, що заявляється, має істотні відмінності. ДЖЕРЕЛА ІНФОРМАЦІЇ 1. Патент US 4129873 (США). Main lobe signal canceller in a null steering array antenna. МПК H01Q 3/26 (1978). P.D. Kennedy - аналог. 2. Патент US 6496158 (США). Intermodulation grating lobe suppression method. МПК H01Q 3/02 (2002). D.A. Ksienski, G.M.Shaw - аналог. 3. Патент UA 40138, (Україна). Система для супроводження рухомих об'єктів з використанням сигналів глобальної супутникової системи радіонавігації. МПК GO IS 5/14 (2009). //Авдєєнко Г.Л., Веселова А.П.; Ільченко М.Ю.; Мазуренко О.В.; Якорнов Є.А. -Промислова власність, 2009, № 6. с. 10 - аналог. 4. Патент UA 55238A, (Україна). Адаптивна по дальності антенна решітка. МПК G01S 5/04 (2002). //Федоров В.І., Саричев Ю.О., Копитко І.Й., Бадеха Д.В., Гусєв Ю.Г. - Промислова власність, 2003, № 3. - прототип. 5. Методы пространственной обработки радиосигналов. /Комарович В.Ф., Никитченко В.В. Л.: ВАС, 1989. 278 с. 6. Радиотехнические системы /Под ред. Ю.М. Казаринова. - М.: Высш. шк., 1990. - 496 с. 7. Корушкин Н.Ф., Симончук В.И., Малышко В.В., Ореховский В.А. Устройства для управления амплитудой и фазой СВЧ-сигналов в миллиметровом диапазоне длин волн. Научно-технический журнал «Техника и приборы СВЧ» 2008, № 1. - с. 36-42. 8. Микроэлектронные устройства СВЧ. /Н.Т. Бова, Ю.Г. Ефремов, В.В. Конин и др.К: Техніка, 1984, - 184 с. 9. Твердотельные устройства СВЧ в технике связи. /Л.Г. Гассанов, А.А. Липатов, В.В. Марков, Н.Н. Могильченко. - М.: Радио и связь, 1988. - 288 с. 10. Патент RU 2204849, (Росія). Сейсмический корреляционный пеленгатор объектов. МПК G01V 1/16, G01S 15/88, G08B 13/00 (2002). Крюков И.Н., Иванов В.А., Дюгованец А.П. 11. Патент RU 2313184, (Росія). Устройство слежения за задержкой шумоподобных частотноманипулируемых сигналов. МПК H04L 7/04 (2006). Кокорин В.И., Бондаренко В.Н., Бяков А.Г. 15 55415 16 17 Комп’ютерна верстка Д. Шеверун 55415 Підписне 18 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюReceiving distributed adaptive antenna array

Автори англійськоюIlchenko Mykhailo Yukhymovych, Mazurenko Oleksandr Viktorovych, Yakornov Yevhenii Arkadiiovych

Назва патенту російськоюПриемная разреженная адаптивная антенная решетка

Автори російськоюИльченко Михаил Ефимович, Мазуренко Александр Викторович, Якорнов Евгений Аркадиевич

МПК / Мітки

Мітки: адаптивна, решітка, антенна, приймальна, розріджена

Код посилання

<a href="https://ua.patents.su/9-55415-prijjmalna-rozridzhena-adaptivna-antenna-reshitka.html" target="_blank" rel="follow" title="База патентів України">Приймальна розріджена адаптивна антенна решітка</a>

Попередній патент: Спосіб диференційної діагностики соматоформних розладів

Наступний патент: Гнучкий шланг

Випадковий патент: Пристрій для передачі руху