Обчислювальний пристрій для множення нечітких чисел

Номер патенту: 65213

Опубліковано: 25.11.2011

Автори: Кондратенко Юрій Пантелійович, Кондратенко Володимир Юрійович, Кондратенко Ніна Юріївна

Формула / Реферат

Обчислювальний пристрій для множення нечітких чисел, що містить задавальний елемент для введення експертних оцінок відповідного нечіткого параметра, багатоканальний блок пам'яті з шістьма виходами для введення і зберігання даних, що характеризують нечітку інформацію у вигляді нечітких множин з трикутною формою функцій належності, багатофункціональний обчислювальний блок та блок відображення обробленої інформації, багатофункціональний обчислювальний блок виконаний у вигляді арифметико-логічного пристрою, що містить перший, другий, третій, четвертий, п'ятий, шостий, сьомий, восьмий та дев'ятий суматори, перший, другий, третій і четвертий керовані ключі, перший, другий і третій порогові елементи, перший і другий елементи І, перший і другий блоки ділення, а також перший і другий елементи заперечення, перший прямий вхід першого суматора підключений до першого входу багатофункціонального обчислювального блока і до інформаційних входів першого та другого керованих ключів, а вихід - до входу першого порогового елемента, вихід якого з'єднаний з першим входом першого елемента І та з керованим входом першого керованого ключа, вихід якого підключений до першого прямого входу другого суматора, вихід якого з'єднаний з входом другого порогового елемента, вихід якого з'єднаний з першим входом другого елемента І, з входом першого елемента заперечення та з керованим входом другого керованого ключа, вихід якого підключений до першого прямого входу третього суматора, вихід якого з'єднаний з входом третього порогового елемента, вихід якого з'єднаний через другий елемент заперечення з другим входом другого елемента І, вихід якого підключений до керованого входу четвертого керованого ключа, підключеного своїм виходом до другого інвертованого входу шостого суматора, вихід якого з'єднаний з виходом багатофункціонального обчислювального блока, а перший прямий вхід - з виходом третього керованого ключа, керуючий вхід якого з'єднаний з виходом першого елемента І, другий вхід якого підключений до виходу першого елемента заперечення, вихід п'ятого суматора з'єднаний з другим входом другого блока ділення, а вихід четвертого суматора – з другим входом першого блока ділення, вихід задавального елемента з'єднаний з першим входом багатофункціонального обчислювального блока, вихід якого підключений до входу блока відображення обробленої інформації, перші входи сьомого та восьмого суматорів підключені відповідно до першого і другого виходів багатоканального блока пам'яті, який відрізняється тим, що введено додатково сім суматорів, чотири масштабні блоки, два квадратори, два блоки обчислення квадратного кореня, одинадцять помножувачів та два блоки ділення, перший інвертований вхід сьомого суматора підключений до другого входу багатофункціонального обчислювального блока та перших входів першого і четвертого помножувачів, другий прямий вхід - до третього входу багатофункціонального обчислювального блока, перших входів другого і дев'ятого помножувачів та першого прямого входу восьмого суматора, а вихід - до перших входів п'ятого і шостого помножувачів, другий інвертований вхід восьмого суматора підключений до третього виходу багатоканального блока пам'яті, четвертого входу багатофункціонального обчислювального блока та першого входу третього помножувача, а вихід восьмого суматора - до перших входів восьмого і десятого помножувачів, перший інвертований вхід дев'ятого суматора підключений до четвертого виходу багатоканального блока пам'яті, п'ятого входу багатофункціонального обчислювального блока та других входів першого і п'ятого помножувачів, другий прямий вхід - до п'ятого виходу багатоканального блока пам'яті, шостого входу багатофункціонального обчислювального блока, других входів другого і восьмого помножувачів та першого прямого входу десятого суматора, а вихід - до других входів четвертого і шостого помножувачів, другий інвертований вхід десятого суматора підключений до шостого виходу багатоканального блока пам'яті, сьомоговходу багатофункціонального обчислювального блока та другого входу третього помножувача, а вихід десятого суматора - до другого входу дев'ятого помножувача і через третій масштабний блок до другого входу десятого помножувача, перший прямий вхід четвертого суматора з'єднаний з виходом четвертого помножувача та першим інвертованим входом одинадцятого суматора, другий прямий вхід - з виходом п'ятого помножувача та другим прямим входом одинадцятого суматора, вихід якого через перший квадратор підключений до першого прямого входу п'ятнадцятого суматора, вихід якого з'єднаний через перший блок обчислення квадратного кореня з першим входом третього блока ділення, вихід шостого помножувача підключений через перший масштабний блок до першого входу першого блока ділення, другого входу третього блока ділення та першого входу сьомого помножувача, другий вхід якого підключений через другий масштабний блок до першого прямого входу першого суматора, виходи першого, другого і третього помножувачів з'єднані відповідно з другими інвертованими входами першого, другого і третього суматорів, перший прямий вхід тринадцятого суматора з'єднаний з виходом третього блока ділення, другий інвертований вхід - з виходом першого блока ділення, а вихід - з інформаційним входом третього керованого ключа, перший прямий вхід п'ятого суматора з'єднаний з виходом дев'ятого помножувача та першим інвертованим входом дванадцятого суматора, другий прямий вхід - з виходом восьмого помножувача та другим прямим входом дванадцятого суматора, вихід якого через другий квадратор підключений до першого прямого входу шістнадцятого суматора, вихід якого з'єднаний через другий блок обчислення квадратного кореня з першим входом четвертого блока ділення, вихід десятого помножувача підключений безпосередньо до першого входу другого блока ділення і другого входу четвертого блока ділення та через четвертий масштабний блок до першого входу одинадцятого помножувача, другий вхід якого з'єднаний з першим прямим входом першого суматора, а вихід - з другим прямим входом шістнадцятого суматора, перший інвертований вхід тринадцятого суматора з'єднаний з виходом четвертого блока ділення, другий інвертований вхід - з виходом другого блока ділення, а вихід - з інформаційним входом четвертого керованого ключа.

Текст

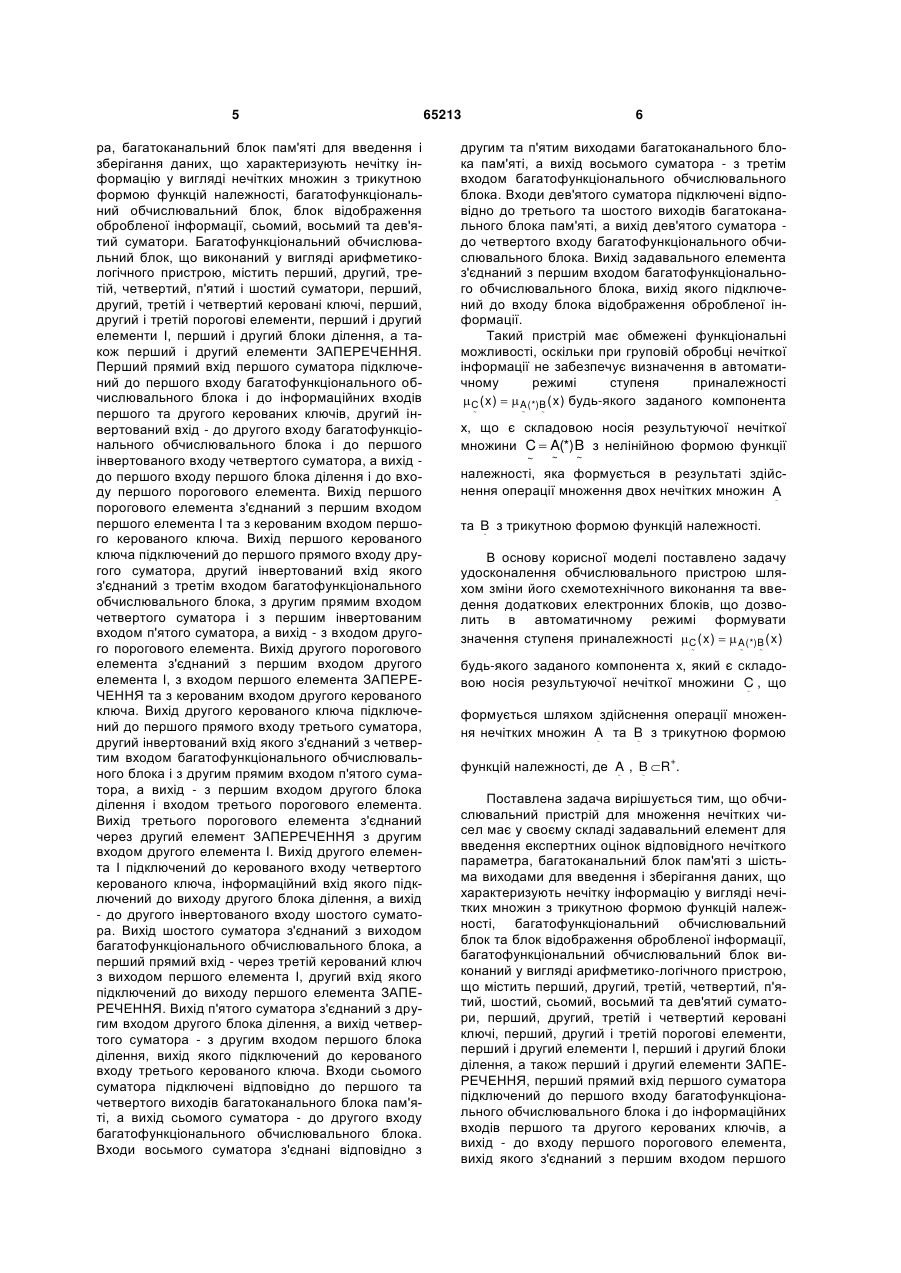

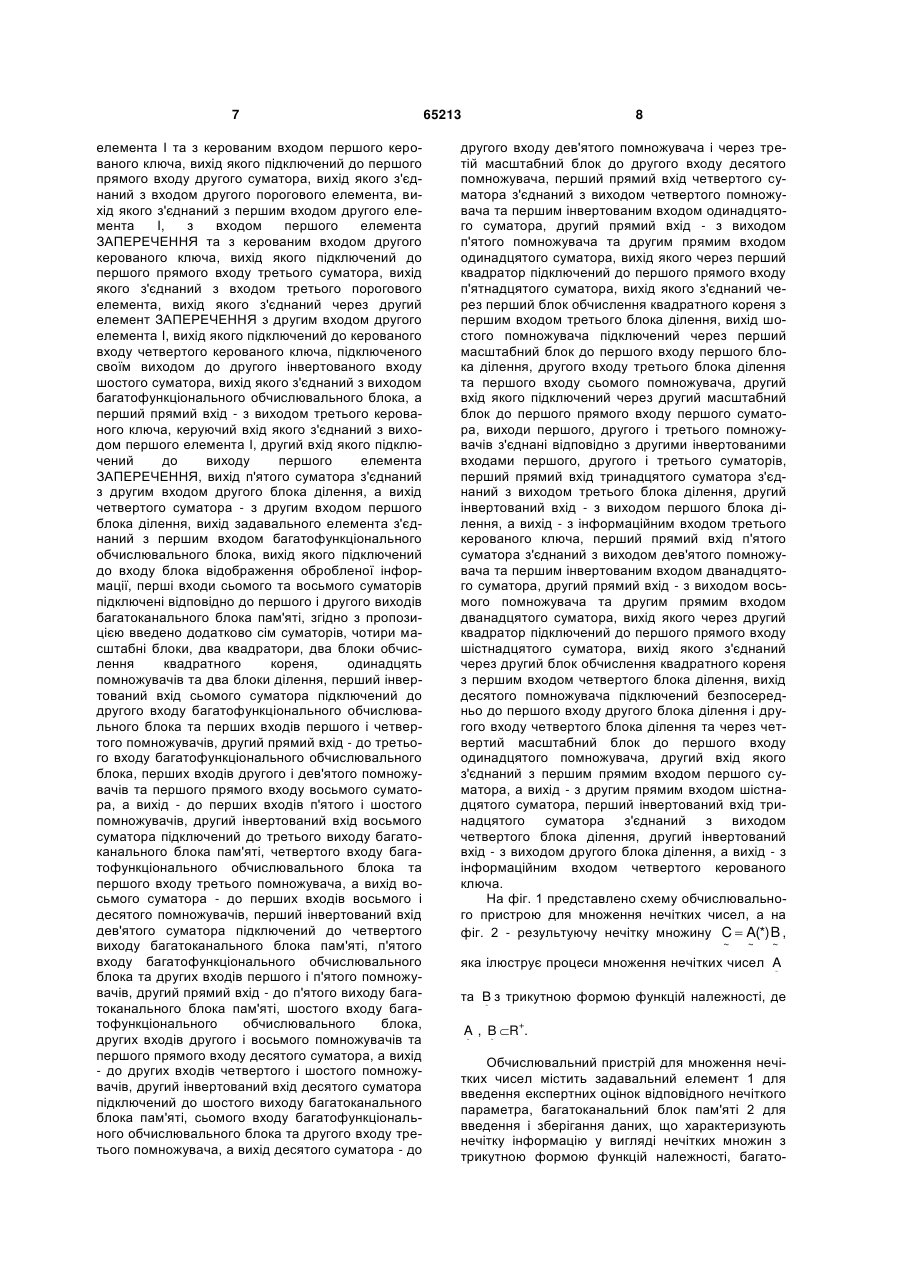

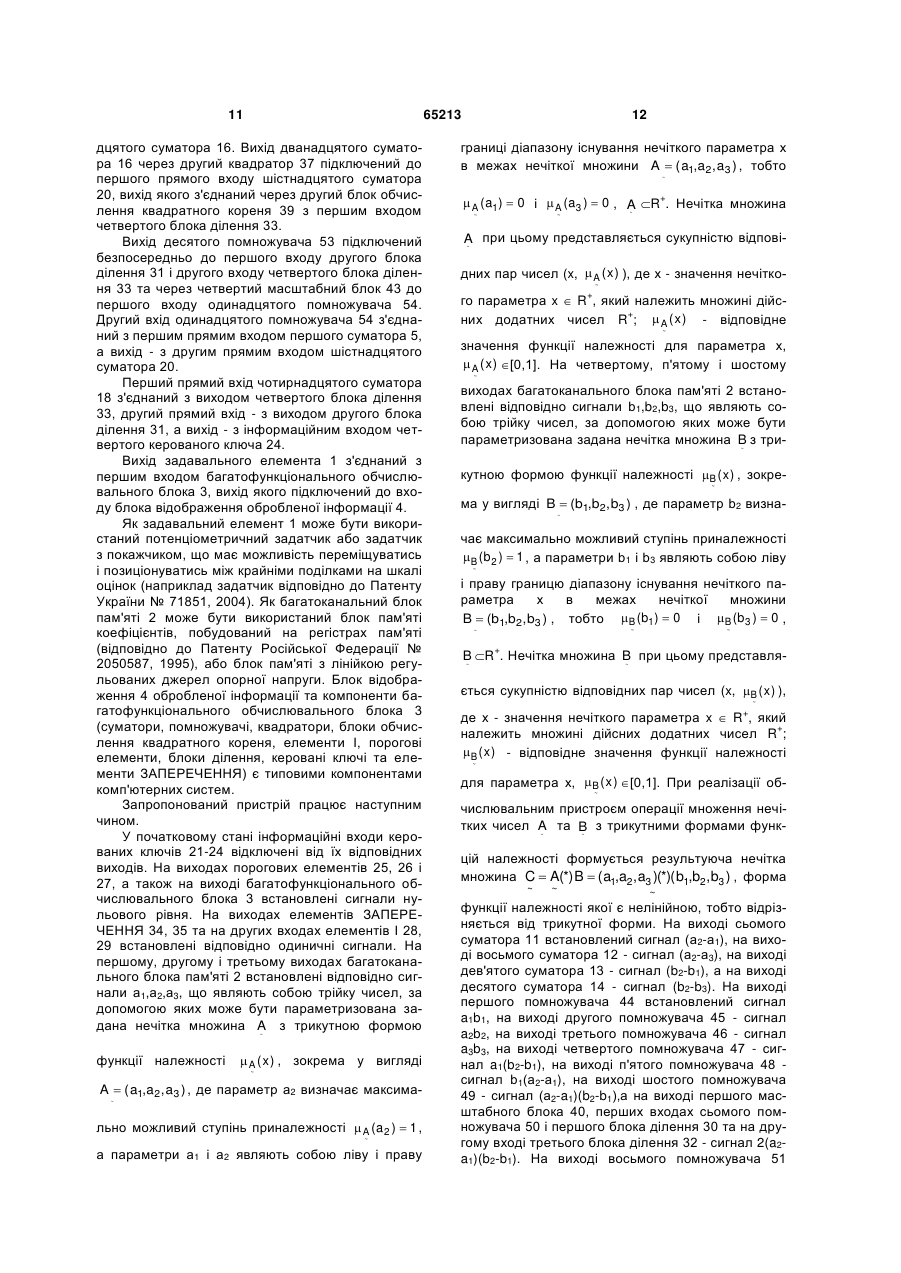

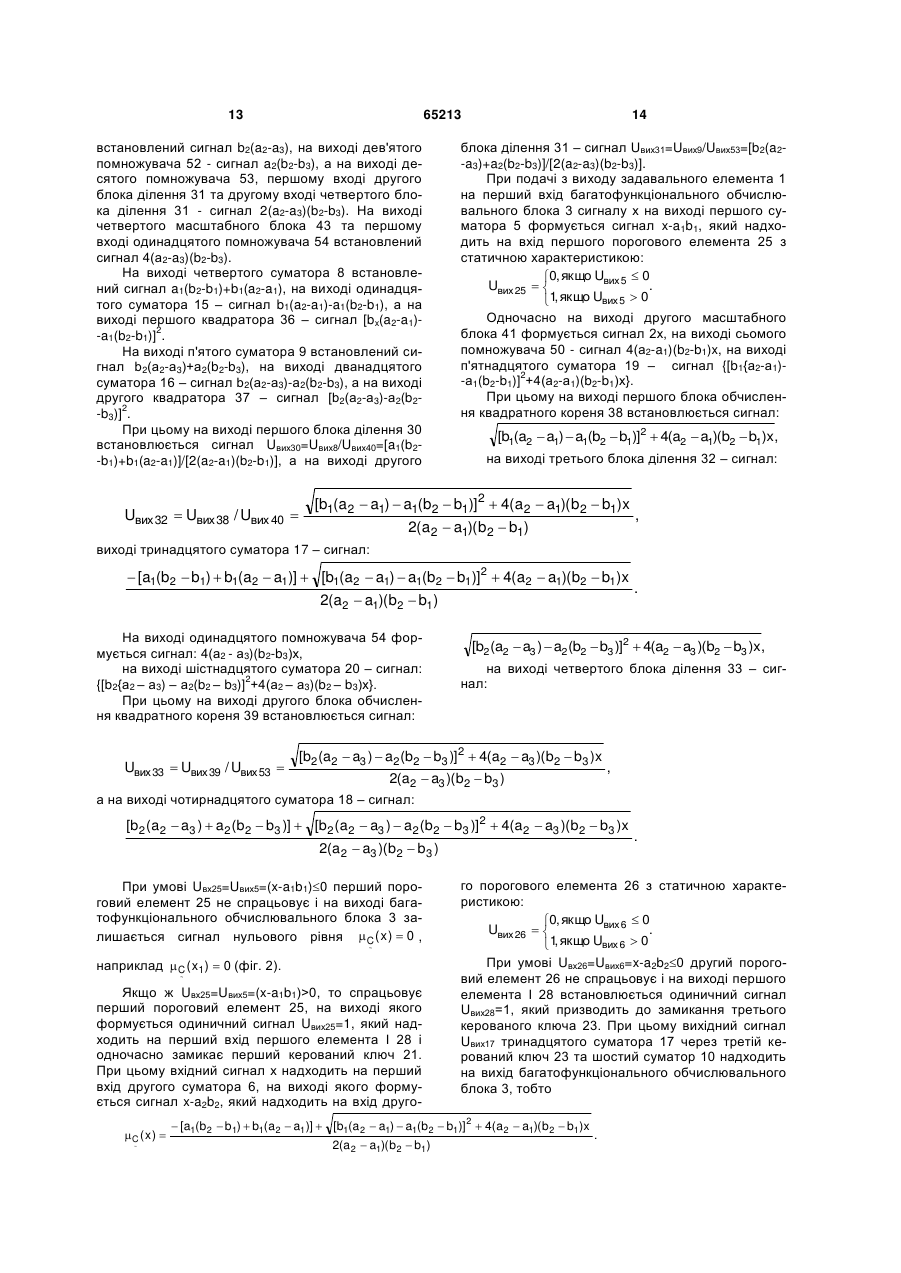

Обчислювальний пристрій для множення нечітких чисел, що містить задавальний елемент для введення експертних оцінок відповідного нечіткого параметра, багатоканальний блок пам'яті з шістьма виходами для введення і зберігання даних, що характеризують нечітку інформацію у вигляді нечітких множин з трикутною формою функцій належності, багатофункціональний обчислювальний блок та блок відображення обробленої інформації, багатофункціональний обчислювальний блок виконаний у вигляді арифметико-логічного пристрою, що містить перший, другий, третій, четвертий, п'ятий, шостий, сьомий, восьмий та дев'ятий суматори, перший, другий, третій і четвертий керовані ключі, перший, другий і третій порогові елементи, перший і другий елементи І, перший і другий блоки ділення, а також перший і другий елементи заперечення, перший прямий вхід першого суматора підключений до першого входу багатофункціонального обчислювального блока і до інформаційних входів першого та другого керованих ключів, а вихід - до входу першого порогового елемента, вихід якого з'єднаний з першим входом першого елемента І та з керованим входом першого керованого ключа, вихід якого підключений до першого прямого входу другого суматора, вихід якого з'єднаний з входом другого порогового елемента, вихід якого з'єднаний з першим входом другого елемента І, з входом першого елемента заперечення та з керованим входом другого керованого ключа, вихід якого підключений до першого прямого входу третього суматора, вихід якого з'єднаний з входом третього порогового елемента, вихід якого з'єднаний через другий елемент заперечення з другим входом другого елемента І, вихід якого підключений до керованого входу четвертого керованого ключа, підключеного своїм виходом до другого інвертованого входу шостого суматора, вихід якого з'єднаний з виходом багатофункціонального обчи 2 (19) 1 3 65213 4 сятого суматора - до другого входу дев'ятого помножувача і через третій масштабний блок до другого входу десятого помножувача, перший прямий вхід четвертого суматора з'єднаний з виходом четвертого помножувача та першим інвертованим входом одинадцятого суматора, другий прямий вхід - з виходом п'ятого помножувача та другим прямим входом одинадцятого суматора, вихід якого через перший квадратор підключений до першого прямого входу п'ятнадцятого суматора, вихід якого з'єднаний через перший блок обчислення квадратного кореня з першим входом третього блока ділення, вихід шостого помножувача підключений через перший масштабний блок до першого входу першого блока ділення, другого входу третього блока ділення та першого входу сьомого помножувача, другий вхід якого підключений через другий масштабний блок до першого прямого входу першого суматора, виходи першого, другого і третього помножувачів з'єднані відповідно з другими інвертованими входами першого, другого і третього суматорів, перший прямий вхід тринадцятого суматора з'єднаний з виходом третього блока ділення, другий інвертований вхід - з вихо дом першого блока ділення, а вихід - з інформаційним входом третього керованого ключа, перший прямий вхід п'ятого суматора з'єднаний з виходом дев'ятого помножувача та першим інвертованим входом дванадцятого суматора, другий прямий вхід - з виходом восьмого помножувача та другим прямим входом дванадцятого суматора, вихід якого через другий квадратор підключений до першого прямого входу шістнадцятого суматора, вихід якого з'єднаний через другий блок обчислення квадратного кореня з першим входом четвертого блока ділення, вихід десятого помножувача підключений безпосередньо до першого входу другого блока ділення і другого входу четвертого блока ділення та через четвертий масштабний блок до першого входу одинадцятого помножувача, другий вхід якого з'єднаний з першим прямим входом першого суматора, а вихід - з другим прямим входом шістнадцятого суматора, перший інвертований вхід тринадцятого суматора з'єднаний з виходом четвертого блока ділення, другий інвертований вхід - з виходом другого блока ділення, а вихід - з інформаційним входом четвертого керованого ключа. Корисна модель належить до обчислювальної техніки, а саме до моделювання керованих процесів і об'єктів, що функціонують в умовах невизначеності, й може бути використана для групової обробки нечіткої інформації, зокрема, для автоматичного визначення ступеня приналежності відповідних параметрів або показників до результуючих нелінійних нечітких множин, сформованих в результаті множення нечітких множин з трикутною формою функцій належності. Відомо про пристрої для групової обробки нечіткої інформації, що базуються на використанні задавальних елементів, багатофункціональних обчислювальних блоків, блоків відображення обробленої інформації та багатоканальних блоків пам'яті для зберігання значень нечіткого параметра та відповідних значень ступеня приналежності згідно з заданою формою функції належності досліджуваної нечіткої множини. Прикладом таких пристроїв є пристрій для обробки нечіткої інформації, що реалізує спосіб одержання якісних експертних оцінок при моделюванні економічних, соціальних, біологічних систем [патент України №71851,G06F 17/60, G06N 7/06 2004], що має у своєму складі задавальний елемент для введення експертних оцінок відповідного нечіткого параметра, виконаний у вигляді потенціометричного задатчика або задатчика з покажчиком, що має можливість переміщуватись і позиціонуватись між крайніми поділками на шкалі оцінок, багатоканальний блок пам'яті для введення і зберігання даних (min і max - границь числового відрізку [min max], на якому визначається значення нечіткого параметра х, а також n - цілого значення потенційної лінгвістичної потужності числового відрізку [min max], що характеризують нечітку інформацію у вигляді нечіткого числа, наприклад A , з трикут~ ною формою функції належності, багатофункціональний обчислювальний блок та блок відображення обробленої інформації, вихід задавального елемента та перший, другий і третій виходи багатоканального блока пам'яті з'єднані відповідно з першим, другим, третім і четвертим входами багатофункціонального обчислювального блока, вихід якого підключений до входу блока відображення обробленої інформації. Такий пристрій має наступні проблеми: - мають місце обмежені функціональні можливості, оскільки пристрій забезпечує формування відповідної до задавального сигналу нечіткої множини з трикутною формою функції належності, але не формує в автоматичному режимі ступінь приналежності A ( x ) будь-якого заданого компонента ~ х, що є складовою носія нечіткої множини A з ~ трикутною формою функції належності; - для реалізації компонентів пристрою з відповідними взаємозв'язками має місце застосування ПЕОМ, що ускладнює використання такого пристрою у складі вбудованих електронних систем (embedded systems), які широко використовуються в бортових обчислювальних комплексах різнотипного призначення. Найбільш близьким до запропонованого є пристрій для групової обробки нечіткої інформації [патент України № 48972,G06F17/20, Бюл. №7, 2010], що прийнятий як прототип. Цей пристрій для групової обробки нечіткої інформації має у своєму складі задавальний елемент для введення експертних оцінок відповідного нечіткого парамет 5 ра, багатоканальний блок пам'яті для введення і зберігання даних, що характеризують нечітку інформацію у вигляді нечітких множин з трикутною формою функцій належності, багатофункціональний обчислювальний блок, блок відображення обробленої інформації, сьомий, восьмий та дев'ятий суматори. Багатофункціональний обчислювальний блок, що виконаний у вигляді арифметикологічного пристрою, містить перший, другий, третій, четвертий, п'ятий і шостий суматори, перший, другий, третій і четвертий керовані ключі, перший, другий і третій порогові елементи, перший і другий елементи І, перший і другий блоки ділення, а також перший і другий елементи ЗАПЕРЕЧЕННЯ. Перший прямий вхід першого суматора підключений до першого входу багатофункціонального обчислювального блока і до інформаційних входів першого та другого керованих ключів, другий інвертований вхід - до другого входу багатофункціонального обчислювального блока і до першого інвертованого входу четвертого суматора, а вихід до першого входу першого блока ділення і до входу першого порогового елемента. Вихід першого порогового елемента з'єднаний з першим входом першого елемента І та з керованим входом першого керованого ключа. Вихід першого керованого ключа підключений до першого прямого входу другого суматора, другий інвертований вхід якого з'єднаний з третім входом багатофункціонального обчислювального блока, з другим прямим входом четвертого суматора і з першим інвертованим входом п'ятого суматора, а вихід - з входом другого порогового елемента. Вихід другого порогового елемента з'єднаний з першим входом другого елемента І, з входом першого елемента ЗАПЕРЕЧЕННЯ та з керованим входом другого керованого ключа. Вихід другого керованого ключа підключений до першого прямого входу третього суматора, другий інвертований вхід якого з'єднаний з четвертим входом багатофункціонального обчислювального блока і з другим прямим входом п'ятого суматора, а вихід - з першим входом другого блока ділення і входом третього порогового елемента. Вихід третього порогового елемента з'єднаний через другий елемент ЗАПЕРЕЧЕННЯ з другим входом другого елемента І. Вихід другого елемента І підключений до керованого входу четвертого керованого ключа, інформаційний вхід якого підключений до виходу другого блока ділення, а вихід - до другого інвертованого входу шостого суматора. Вихід шостого суматора з'єднаний з виходом багатофункціонального обчислювального блока, а перший прямий вхід - через третій керований ключ з виходом першого елемента І, другий вхід якого підключений до виходу першого елемента ЗАПЕРЕЧЕННЯ. Вихід п'ятого суматора з'єднаний з другим входом другого блока ділення, а вихід четвертого суматора - з другим входом першого блока ділення, вихід якого підключений до керованого входу третього керованого ключа. Входи сьомого суматора підключені відповідно до першого та четвертого виходів багатоканального блока пам'яті, а вихід сьомого суматора - до другого входу багатофункціонального обчислювального блока. Входи восьмого суматора з'єднані відповідно з 65213 6 другим та п'ятим виходами багатоканального блока пам'яті, а вихід восьмого суматора - з третім входом багатофункціонального обчислювального блока. Входи дев'ятого суматора підключені відповідно до третього та шостого виходів багатоканального блока пам'яті, а вихід дев'ятого суматора до четвертого входу багатофункціонального обчислювального блока. Вихід задавального елемента з'єднаний з першим входом багатофункціонального обчислювального блока, вихід якого підключений до входу блока відображення обробленої інформації. Такий пристрій має обмежені функціональні можливості, оскільки при груповій обробці нечіткої інформації не забезпечує визначення в автоматичному режимі ступеня приналежності С ( x ) A (*)B ( x ) будь-якого заданого компонента ~ ~ ~ х, що є складовою носія результуючої нечіткої множини C A(*) B з нелінійною формою функції ~ ~ ~ належності, яка формується в результаті здійснення операції множення двох нечітких множин A ~ та B з трикутною формою функцій належності. ~ В основу корисної моделі поставлено задачу удосконалення обчислювального пристрою шляхом зміни його схемотехнічного виконання та введення додаткових електронних блоків, що дозволить в автоматичному режимі формувати значення ступеня приналежності С ( x ) A (*)B ( x ) ~ ~ ~ будь-якого заданого компонента х, який є складовою носія результуючої нечіткої множини C , що ~ формується шляхом здійснення операції множення нечітких множин A та B з трикутною формою ~ ~ функцій належності, де A , B R . ~ ~ + Поставлена задача вирішується тим, що обчислювальний пристрій для множення нечітких чисел має у своєму складі задавальний елемент для введення експертних оцінок відповідного нечіткого параметра, багатоканальний блок пам'яті з шістьма виходами для введення і зберігання даних, що характеризують нечітку інформацію у вигляді нечітких множин з трикутною формою функцій належності, багатофункціональний обчислювальний блок та блок відображення обробленої інформації, багатофункціональний обчислювальний блок виконаний у вигляді арифметико-логічного пристрою, що містить перший, другий, третій, четвертий, п'ятий, шостий, сьомий, восьмий та дев'ятий суматори, перший, другий, третій і четвертий керовані ключі, перший, другий і третій порогові елементи, перший і другий елементи І, перший і другий блоки ділення, а також перший і другий елементи ЗАПЕРЕЧЕННЯ, перший прямий вхід першого суматора підключений до першого входу багатофункціонального обчислювального блока і до інформаційних входів першого та другого керованих ключів, а вихід - до входу першого порогового елемента, вихід якого з'єднаний з першим входом першого 7 елемента І та з керованим входом першого керованого ключа, вихід якого підключений до першого прямого входу другого суматора, вихід якого з'єднаний з входом другого порогового елемента, вихід якого з'єднаний з першим входом другого елемента І, з входом першого елемента ЗАПЕРЕЧЕННЯ та з керованим входом другого керованого ключа, вихід якого підключений до першого прямого входу третього суматора, вихід якого з'єднаний з входом третього порогового елемента, вихід якого з'єднаний через другий елемент ЗАПЕРЕЧЕННЯ з другим входом другого елемента І, вихід якого підключений до керованого входу четвертого керованого ключа, підключеного своїм виходом до другого інвертованого входу шостого суматора, вихід якого з'єднаний з виходом багатофункціонального обчислювального блока, а перший прямий вхід - з виходом третього керованого ключа, керуючий вхід якого з'єднаний з виходом першого елемента І, другий вхід якого підключений до виходу першого елемента ЗАПЕРЕЧЕННЯ, вихід п'ятого суматора з'єднаний з другим входом другого блока ділення, а вихід четвертого суматора - з другим входом першого блока ділення, вихід задавального елемента з'єднаний з першим входом багатофункціонального обчислювального блока, вихід якого підключений до входу блока відображення обробленої інформації, перші входи сьомого та восьмого суматорів підключені відповідно до першого і другого виходів багатоканального блока пам'яті, згідно з пропозицією введено додатково сім суматорів, чотири масштабні блоки, два квадратори, два блоки обчислення квадратного кореня, одинадцять помножувачів та два блоки ділення, перший інвертований вхід сьомого суматора підключений до другого входу багатофункціонального обчислювального блока та перших входів першого і четвертого помножувачів, другий прямий вхід - до третього входу багатофункціонального обчислювального блока, перших входів другого і дев'ятого помножувачів та першого прямого входу восьмого суматора, а вихід - до перших входів п'ятого і шостого помножувачів, другий інвертований вхід восьмого суматора підключений до третього виходу багатоканального блока пам'яті, четвертого входу багатофункціонального обчислювального блока та першого входу третього помножувача, а вихід восьмого суматора - до перших входів восьмого і десятого помножувачів, перший інвертований вхід дев'ятого суматора підключений до четвертого виходу багатоканального блока пам'яті, п'ятого входу багатофункціонального обчислювального блока та других входів першого і п'ятого помножувачів, другий прямий вхід - до п'ятого виходу багатоканального блока пам'яті, шостого входу багатофункціонального обчислювального блока, других входів другого і восьмого помножувачів та першого прямого входу десятого суматора, а вихід - до других входів четвертого і шостого помножувачів, другий інвертований вхід десятого суматора підключений до шостого виходу багатоканального блока пам'яті, сьомого входу багатофункціонального обчислювального блока та другого входу третього помножувача, а вихід десятого суматора - до 65213 8 другого входу дев'ятого помножувача і через третій масштабний блок до другого входу десятого помножувача, перший прямий вхід четвертого суматора з'єднаний з виходом четвертого помножувача та першим інвертованим входом одинадцятого суматора, другий прямий вхід - з виходом п'ятого помножувача та другим прямим входом одинадцятого суматора, вихід якого через перший квадратор підключений до першого прямого входу п'ятнадцятого суматора, вихід якого з'єднаний через перший блок обчислення квадратного кореня з першим входом третього блока ділення, вихід шостого помножувача підключений через перший масштабний блок до першого входу першого блока ділення, другого входу третього блока ділення та першого входу сьомого помножувача, другий вхід якого підключений через другий масштабний блок до першого прямого входу першого суматора, виходи першого, другого і третього помножувачів з'єднані відповідно з другими інвертованими входами першого, другого і третього суматорів, перший прямий вхід тринадцятого суматора з'єднаний з виходом третього блока ділення, другий інвертований вхід - з виходом першого блока ділення, а вихід - з інформаційним входом третього керованого ключа, перший прямий вхід п'ятого суматора з'єднаний з виходом дев'ятого помножувача та першим інвертованим входом дванадцятого суматора, другий прямий вхід - з виходом восьмого помножувача та другим прямим входом дванадцятого суматора, вихід якого через другий квадратор підключений до першого прямого входу шістнадцятого суматора, вихід якого з'єднаний через другий блок обчислення квадратного кореня з першим входом четвертого блока ділення, вихід десятого помножувача підключений безпосередньо до першого входу другого блока ділення і другого входу четвертого блока ділення та через четвертий масштабний блок до першого входу одинадцятого помножувача, другий вхід якого з'єднаний з першим прямим входом першого суматора, а вихід - з другим прямим входом шістнадцятого суматора, перший інвертований вхідтринадцятого суматора з'єднаний з виходом четвертого блока ділення, другий інвертований вхід - з виходом другого блока ділення, а вихід - з інформаційним входом четвертого керованого ключа. На фіг. 1 представлено схему обчислювального пристрою для множення нечітких чисел, а на фіг. 2 - результуючу нечітку множину C A(*) B , ~ ~ ~ яка ілюструє процеси множення нечітких чисел A ~ та B з трикутною формою функцій належності, де ~ A , B R . ~ ~ + Обчислювальний пристрій для множення нечітких чисел містить задавальний елемент 1 для введення експертних оцінок відповідного нечіткого параметра, багатоканальний блок пам'яті 2 для введення і зберігання даних, що характеризують нечітку інформацію у вигляді нечітких множин з трикутною формою функцій належності, багато 9 функціональний обчислювальний блок 3, блок відображення 4 обробленої інформації. Багатофункціональний обчислювальний блок 3 виконаний у вигляді арифметико-логічного пристрою. Блок 3 містить перший 5, другий 6, третій 7, четвертий 8, п'ятий 9, шостий 10, сьомий 11, восьмий 12, дев'ятий 13, десятий 14, одинадцятий 15, дванадцятий 16, тринадцятий 17, чотирнадцятий 18, п'ятнадцятий 19 та шістнадцятий 20 суматори, перший 21, другий 22, третій 23 і четвертий 24 керовані ключі, перший 25, другий 26 і третій 27 порогові елементи, перший 28 і другий 29 елементи І, перший 30, другий 31, третій 32 і четвертий 33 блоки ділення, перший 34 і другий 35 елементи ЗАПЕРЕЧЕННЯ, перший 36 та другий 37 квадратори, перший 38 і другий 39 блоки обчислення квадратного кореня, перший 40, другий 41, третій 42 і четвертий 43 масштабні блоки, а також перший 44, другий 45, третій 46, четвертий 47, п'ятий 48, шостий 49, сьомий 50, восьмий 51, дев'ятий 52, десятий 53 і одинадцятий 54 помножувачі. Перший прямий вхід першого суматора 5 підключений до першого входу багатофункціонального обчислювального блока 3 і до інформаційних входів першого 21 та другого 22 керованих ключів, а вихід - до входу першого порогового елемента 25. Вихід першого порогового елемента 25 з'єднаний з першим входом першого елемента І 28 та з керованим входом першого керованого ключа 21, вихід якого підключений до першого прямого входу другого суматора 6. Вихід другого суматора 6 з'єднаний з входом другого порогового елемента 26, вихід якого з'єднаний з першим входом другого елемента І 29, з входом першого елемента ЗАПЕРЕЧЕННЯ 34 та з керованим входом другого керованого ключа 22, вихід якого підключений до першого прямого входу третього суматора 7. Вихід третього суматора 7 з'єднаний з входом третього порогового елемента 27, вихід якого з'єднаний через другий елемент ЗАПЕРЕЧЕННЯ 35 з другим входом другого елемента І 29. Вихід другого елемента І 29 підключений до керованого входу четвертого керованого ключа 24, підключеного своїм виходом до другого інвертованого входу шостого суматора 10. Вихід шостого суматора 10 з'єднаний з виходом багатофункціонального обчислювального блока 3, а перший прямий вхід шостого суматора 10 - з виходом третього керованого ключа 23. Керований вхід третього керованого ключа 23 з'єднаний з виходом першого елемента І 28, другий вхід якого підключений до виходу першого елемента ЗАПЕРЕЧЕННЯ 34. Вихід п'ятого суматора 9 з'єднаний з другим входом другого блока ділення 31, а вихід четвертого суматора 8 - з другим входом першого блока ділення 30. Перші входи сьомого 11 та восьмого 12 суматорів підключені відповідно до першого і другого виходів багатоканального блока пам'яті 2. При цьому перший інвертований вхід сьомого суматора 11 підключений одночасно до першого виходу багатоканального блока пам'яті 2, другого входу багатофункціонального обчислювального блока 3 та перших входів першого 44 і четвертого 47 помножувачів, а другий прямий вхід - до другого виходу багатоканального блока пам'яті 2, третього входу багатофункціона 65213 10 льного обчислювального блока 3, перших входів другого 45 і дев'ятого 52 помножувачів та першого прямого входу восьмого суматора 12, а вихід сьомого суматора 11 - до перших входів п'ятого 48 і шостого 49 помножувачів. Другий інвертований вхід восьмого суматора 12 підключений до третього виходу багатоканального блока пам'яті 2, четвертого входу багатофункціонального обчислювального блока 3 та першого входу третього помножувача 46, а вихід восьмого суматора 12 до перших входів восьмого 51 і десятого 53 помножувачів. Перший інвертований вхід дев'ятого суматора 13 підключений до четвертого виходу багатоканального блока пам'яті 2, п'ятого входу багатофункціонального обчислювального блока 3 та других входів першого 44 і п'ятого 48 помножувачів, другий прямий вхід - до п'ятого виходу багатоканального блока пам'яті 2, шостого входу багатофункціонального обчислювального блока 3, других входів другого 45 і восьмого 51 помножувачів та першого прямого входу десятого суматора 14, а вихід дев'ятого суматора 13 - до других входів четвертого 47 і шостого 49 помножувачів. Другий інвертований вхід десятого суматора 14 підключений до шостого виходу багатоканального блока пам'яті 2, сьомого входу багатофункціонального обчислювального блока 3 та другого входу третього помножувача 46, а вихід десятого суматора 14 - до другого входу дев'ятого помножувача 52 і через третій масштабний блок 42 до другого входу десятого помножувача 53. Перший прямий вхід четвертого суматора 8 з'єднаний з виходом четвертого помножувача 47 та першим інвертованим входом одинадцятого суматора 15, другий прямий вхід - з виходом п'ятого помножувача 48 та другим прямим входом одинадцятого суматора 15. Вихід одинадцятого суматора 15 через перший квадратор 36 підключений до першого прямого входу п'ятнадцятого суматора 19, вихід якого з'єднаний через перший блок обчислення квадратного кореня 38 з першим входом третього блока ділення 32. Вихід шостого помножувача 49 підключений через перший масштабний блок 40 до першого входу першого блока ділення 30, другого входу третього блока ділення 32 та першого входу сьомого помножувача 50, другий вхід якого підключений через другий масштабний блок 41 до першого прямого входу першого суматора 5. Вихід першого помножувача 44 з'єднаний з другим інвертованим входом першого суматора 5, вихід другого помножувача 45 - з другим інвертованим входом другого суматора 6, а вихід третього помножувача 46 - з другим інвертованим входом третього суматора 7. Перший прямий вхід тринадцятого суматора 17 з'єднаний з виходом третього блока ділення 32, другий інвертований вхід - з виходом першого блока ділення 30, а вихід - з інформаційним входом третього керованого ключа 23. Перший прямий вхід п'ятого суматора 9 з'єднаний з виходом дев'ятого помножувача 52 та першим інвертованим входом дванадцятого суматора 16, другий прямий вхід - з виходом восьмого помножувача 51 та другим прямим входом двана 11 65213 дцятого суматора 16. Вихід дванадцятого суматора 16 через другий квадратор 37 підключений до першого прямого входу шістнадцятого суматора 20, вихід якого з'єднаний через другий блок обчислення квадратного кореня 39 з першим входом четвертого блока ділення 33. Вихід десятого помножувача 53 підключений безпосередньо до першого входу другого блока ділення 31 і другого входу четвертого блока ділення 33 та через четвертий масштабний блок 43 до першого входу одинадцятого помножувача 54. Другий вхід одинадцятого помножувача 54 з'єднаний з першим прямим входом першого суматора 5, а вихід - з другим прямим входом шістнадцятого суматора 20. Перший прямий вхід чотирнадцятого суматора 18 з'єднаний з виходом четвертого блока ділення 33, другий прямий вхід - з виходом другого блока ділення 31, а вихід - з інформаційним входом четвертого керованого ключа 24. Вихід задавального елемента 1 з'єднаний з першим входом багатофункціонального обчислювального блока 3, вихід якого підключений до входу блока відображення обробленої інформації 4. Як задавальний елемент 1 може бути використаний потенціометричний задатчик або задатчик з покажчиком, що має можливість переміщуватись і позиціонуватись між крайніми поділками на шкалі оцінок (наприклад задатчик відповідно до Патенту України № 71851, 2004). Як багатоканальний блок пам'яті 2 може бути використаний блок пам'яті коефіцієнтів, побудований на регістрах пам'яті (відповідно до Патенту Російської Федерації № 2050587, 1995), або блок пам'яті з лінійкою регульованих джерел опорної напруги. Блок відображення 4 обробленої інформації та компоненти багатофункціонального обчислювального блока 3 (суматори, помножувачі, квадратори, блоки обчислення квадратного кореня, елементи І, порогові елементи, блоки ділення, керовані ключі та елементи ЗАПЕРЕЧЕННЯ) є типовими компонентами комп'ютерних систем. Запропонований пристрій працює наступним чином. У початковому стані інформаційні входи керованих ключів 21-24 відключені від їх відповідних виходів. На виходах порогових елементів 25, 26 і 27, а також на виході багатофункціонального обчислювального блока 3 встановлені сигнали нульового рівня. На виходах елементів ЗАПЕРЕЧЕННЯ 34, 35 та на других входах елементів І 28, 29 встановлені відповідно одиничні сигнали. На першому, другому і третьому виходах багатоканального блока пам'яті 2 встановлені відповідно сигнали а1,а2,а3, що являють собою трійку чисел, за допомогою яких може бути параметризована задана нечітка множина A з трикутною формою ~ функції належності A ( x ) , зокрема у вигляді ~ A ( a1,a2, a3 ) , де параметр а2 визначає максима~ льно можливий ступінь приналежності A (a 2 ) 1 , ~ а параметри a1 і а2 являють собою ліву і праву 12 границі діапазону існування нечіткого параметра х в межах нечіткої множини A ( a1,a2, a3 ) , тобто ~ A (a1) 0 і A (a3 ) 0 , A R+. Нечітка множина ~ ~ ~ A при цьому представляється сукупністю відпові~ дних пар чисел (x, A ( x ) ), де х - значення нечітко~ го параметра x R , який належить множині дійс+ них додатних чисел R ; A ( x ) - відповідне + ~ значення функції належності для параметра х, A ( x ) [0,1]. На четвертому, п'ятому і шостому ~ виходах багатоканального блока пам'яті 2 встановлені відповідно сигнали b1,b2,b3, що являють собою трійку чисел, за допомогою яких може бути параметризована задана нечітка множина B з три~ кутною формою функції належності B ( x ) , зокре~ ма у вигляді B (b1,b2, b3 ) , де параметр b2 визна~ чає максимально можливий ступінь приналежності B (b 2 ) 1 , а параметри b1 і b3 являють собою ліву ~ і праву границю діапазону існування нечіткого параметра х в межах нечіткої множини B (b1) 0 і B (b3 ) 0 , B (b1,b2, b3 ) , тобто ~ ~ ~ B R . Нечітка множина B при цьому представля~ ~ + ється сукупністю відповідних пар чисел (x, B ( x ) ), ~ де х - значення нечіткого параметра x R , який + належить множині дійсних додатних чисел R ; B ( x ) - відповідне значення функції належності + ~ для параметра х, B ( x ) [0,1]. При реалізації об~ числювальним пристроєм операції множення нечітких чисел A та B з трикутними формами функ~ ~ цій належності формується результуюча нечітка множина C A(*) B ( a1,a2, a3 )(*)( b1,b2, b3 ) , форма ~ ~ ~ функції належності якої є нелінійною, тобто відрізняється від трикутної форми. На виході сьомого суматора 11 встановлений сигнал (а2-а1), на виході восьмого суматора 12 - сигнал (а2-а3), на виході дев'ятого суматора 13 - сигнал (b2-b1), а на виході десятого суматора 14 - сигнал (b2-b3). На виході першого помножувача 44 встановлений сигнал a1b1, на виході другого помножувача 45 - сигнал a2b2, на виході третього помножувача 46 - сигнал a3b3, на виході четвертого помножувача 47 - сигнал a1(b2-b1), на виході п'ятого помножувача 48 сигнал b1(а2-а1), на виході шостого помножувача 49 - сигнал (а2-a1)(b2-b1),а на виході першого масштабного блока 40, перших входах сьомого помножувача 50 і першого блока ділення 30 та на другому вході третього блока ділення 32 - сигнал 2(a2a1)(b2-b1). На виході восьмого помножувача 51 13 65213 встановлений сигнал b2(a2-a3), на виході дев'ятого помножувача 52 - сигнал a2(b2-b3), а на виході десятого помножувача 53, першому вході другого блока ділення 31 та другому вході четвертого блока ділення 31 - сигнал 2(a2-a3)(b2-b3). На виході четвертого масштабного блока 43 та першому вході одинадцятого помножувача 54 встановлений сигнал 4(а2-a3)(b2-b3). На виході четвертого суматора 8 встановлений сигнал a1(b2-b1)+b1(a2-a1), на виході одинадцятого суматора 15 – сигнал b1(a2-a1)-a1(b2-b1), а на виході першого квадратора 36 – сигнал [bx(a2-a1)2 -a1(b2-b1)] . На виході п'ятого суматора 9 встановлений сигнал b2(а2-а3)+а2(b2-b3), на виході дванадцятого суматора 16 – сигнал b2(а2-а3)-а2(b2-b3), а на виході другого квадратора 37 – сигнал [b2(а2-а3)-а2(b22 -b3)] . При цьому на виході першого блока ділення 30 встановлюється сигнал Uвих30=Uвих8/Uвих40=[a1(b2-b1)+b1(a2-a1)]/[2(a2-a1)(b2-b1)], а на виході другого Uвих 32 Uвих 38 / Uвих 40 14 блока ділення 31 – сигнал Uвих31=Uвих9/Uвих53=[b2(a2-a3)+a2(b2-b3)]/[2(a2-a3)(b2-b3)]. При подачі з виходу задавального елемента 1 на перший вхід багатофункціонального обчислювального блока 3 сигналу х на виході першого суматора 5 формується сигнал x-a1b1, який надходить на вхід першого порогового елемента 25 з статичною характеристикою: 0, якщо Uвих 5 0 Uвих 25 . , 1 якщо Uвих 5 0 Одночасно на виході другого масштабного блока 41 формується сигнал 2х, на виході сьомого помножувача 50 - сигнал 4(а2-a1)(b2-b1)x, на виході п'ятнадцятого суматора 19 – сигнал {[b1{а2-а1)2 -а1(b2-b1)] +4(а2-а1)(b2-b1)х}. При цьому на виході першого блока обчислення квадратного кореня 38 встановлюється сигнал: [b1(a2 a1) a1(b2 b1)]2 4(a2 a1)(b2 b1)x , на виході третього блока ділення 32 – сигнал: [b1(a2 a1) a1(b2 b1)] 2 4(a2 a1)(b2 b1)x 2(a2 a1)(b2 b1) , виході тринадцятого суматора 17 – сигнал: [a1(b2 b1) b1(a2 a1)] [b1(a2 a1) a1(b2 b1)]2 4(a2 a1)(b2 b1)x 2(a2 a1)(b2 b1) На виході одинадцятого помножувача 54 формується сигнал: 4(а2 - а3)(b2-b3)х, на виході шістнадцятого суматора 20 – сигнал: 2 {[b2{а2 – а3) – а2(b2 – b3)] +4(а2 – а3)(b2 – b3)х}. При цьому на виході другого блока обчислення квадратного кореня 39 встановлюється сигнал: Uвих 33 Uвих 39 / Uвих 53 . [b2(a2 a3 ) a2(b2 b3 )]2 4(a2 a3 )(b2 b3 )x , на виході четвертого блока ділення 33 – сигнал: [b2 (a2 a3 ) a2 (b2 b3 )]2 4(a2 a3 )(b2 b3 )x 2(a2 a3 )(b2 b3 ) а на виході чотирнадцятого суматора 18 – сигнал: , [b2 (a2 a3 ) a2 (b2 b3 )] [b2 (a2 a3 ) a2 (b2 b3 )]2 4(a2 a3 )(b2 b3 )x 2(a2 a3 )(b2 b3 ) . При умові Uвx25=Uвих5=(x-a1b1)0 перший пороговий елемент 25 не спрацьовує і на виході багатофункціонального обчислювального блока 3 залишається сигнал нульового рівня C ( x ) 0 , го порогового елемента 26 з статичною характеристикою: 0, якщо Uвих 6 0 Uвих 26 . , 1 якщо Uвих 6 0 наприклад C ( x1) 0 (фіг. 2). При умові Uвx26=Uвиx6=x-a2b20 другий пороговий елемент 26 не спрацьовує і на виході першого елемента І 28 встановлюється одиничний сигнал Uвих28=1, який призводить до замикання третього керованого ключа 23. При цьому вихідний сигнал Uвих17 тринадцятого суматора 17 через третій керований ключ 23 та шостий суматор 10 надходить на вихід багатофункціонального обчислювального блока 3, тобто ~ ~ Якщо ж Uвx25=Uвиx5=(x-a1b1)>0, то спрацьовує перший пороговий елемент 25, на виході якого формується одиничний сигнал Uвих25=1, який надходить на перший вхід першого елемента І 28 і одночасно замикає перший керований ключ 21. При цьому вхідний сигнал x надходить на перший вхід другого суматора 6, на виході якого формується сигнал x-a2b2, який надходить на вхід другоC ( x ) ~ [a1(b2 b1) b1(a2 a1)] [b1(a2 a1) a1(b2 b1)] 2 4(a2 a1)(b2 b1)x 2(a2 a1)(b2 b1) . 15 65213 Відповідний процес обробки нечіткої інформації при визначенні ступеня приналежності C ( x 2 ) ~ нечіткого параметра х2 показано на фіг. 2. Якщо ж Uвx26=Uвих6=х-a2b2>0, то спрацьовує другий пороговий елемент 26, на виході якого формується одиничний сигнал Uвиx26=1, який надходить на перший вхід другого елемента І 29 і встановлює на виході першого елемента ЗАПЕРЕЧЕННЯ 34 та на другому вході першого елемента І 28 сигнал нульового рівня Uвих34=Uвих28=0, а також одночасно замикає другий керований ключ 22. При цьому вхідний сигнал х надходить на перший вхід третього суматора 7, на виході якого формується сигнал х-а3b3, що надхо C ( x ) 2(a2 a3 )(b2 b3 ) Відповідний процес обробки нечіткої інформації при визначенні ступеня приналежності C ( x 3 ) ~ нечіткого параметра х3 показано на фіг. 2. Якщо ж Uвx27=Uвих1=х-а3b3>0, то спрацьовує третій пороговий елемент 27, на виході якого формується одиничний сигнал Uвиx27=1, який встановлює на виході другого елемента ЗАПЕРЕЧЕННЯ 35 та на другому вході другого елемента І 29 сигнал нульового рівня Uвиx35=Uвих29=0. Отже, на виході багатофункціонального обчислювального блока 3 залишається сигнал нульового рівня C ( x ) 0 , наприклад C ( x 4 ) 0 (фіг. 2). Таким ~ ~ чином, обчислювальний пристрій для множення нечітких чисел забезпечує формування на виході багатофункціонального обчислювального блока 3 і відображення блоком 4 сигналу С ( x ) A (*)B ( x ) , ~ ~ ~ що відповідає поточному значенню нечіткого параметра х, який формується задавальним елементом 1. При необхідності обробки нечіткої інформації з використанням інших нечітких множин, наприклад, D (d1,d2, d3 ) та Q q1, q2, q3 ) трикутною формою ~ дить на вхід третього порогового елемента 27 зі статичною характеристикою: 0, якщо Uвих 7 0 Uвих 27 . , 1 якщо Uвих 7 0 При умові Uвx27=Uвих7=х-a3b30 третій пороговий елемент 27 не спрацьовує і на виході другого елемента І 29 встановлюється одиничний сигнал Uвих29=1, який призводить до замикання четвертого керованого ключа 24. При цьому вихідний сигнал Uвих18 чотирнадцятого суматора 18 через четвертий керований ключ 24 надходить на другий інвертований вхід шостого суматора 10, а отже на виході багатофункціонального обчислювального блока 3 встановлюється сигнал Uвих10=-Uвих18, тобто сигнал: [b2 (a2 a3 ) a2 (b2 b3 )] [b2 (a2 a3 ) a2 (b2 b3 )]2 4(a2 a3 )(b2 b3 )x ~ ~ 16 . відповідних функцій належності D ( x ) та Q ( x ) ~ ~ параметри (d1,d2,d3) та (q1,q2,q3) в першу чергу вводяться до багатоканального блока пам'яті 2, а в подальшому обчислювальний пристрій працює аналогічним чином. Позитивний ефект проявляється в тому, що в порівнянні з пристроєм згідно з патентом України №48972 до складу запропонованого пристрою введено додаткові електронні блоки, які дозволяють пристрою на основі вихідних сигналів багатоканального блока пам'яті, що характеризують параметри первинних нечітких множин з трикутними формами функцій належності, формувати в результаті здійснення операції множення первинних нечітких множин відповідну результуючу нечітку множину з нелінійною формою функції належності, а також для будь-якого задавального сигналу, що формується задавальним елементом пристрою, здійснювати в автоматичному режимі обчислення відповідного ступеня його приналежності до вищезгаданої результуючої нечіткої множини. Нові властивості пристрою розширюють область його застосування, а також забезпечують підвищення швидкодії та точності процесів обчислення відповідних ступенів належності. 17 Комп’ютерна верстка А. Крижанівський 65213 Підписне 18 Тираж 23 прим. Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюComputing device for mltiplication of fuzzy numbers

Автори англійськоюKondratenko Volodymyr Yuriiovych, Kondratenko Nina Yuriivna, Kondratenko Yurii Panteliiovych

Назва патенту російськоюВычислительное устройство для умножения нечетких чисел

Автори російськоюКондратенко Владимир Юрьевич, Кондратенко Нина Юриевна, Кондратенко Юрий Пантелеевич

МПК / Мітки

МПК: G06F 17/00

Мітки: нечітких, пристрій, чисел, обчислювальній, множення

Код посилання

<a href="https://ua.patents.su/9-65213-obchislyuvalnijj-pristrijj-dlya-mnozhennya-nechitkikh-chisel.html" target="_blank" rel="follow" title="База патентів України">Обчислювальний пристрій для множення нечітких чисел</a>

Попередній патент: Обчислювальний пристрій для ділення нечітких чисел

Наступний патент: Пристрій для кріплення довгомірного вантажу на транспортному засобі

Випадковий патент: Дискове ґрунтообробне знаряддя