Інтелектуальна розподілена система пам’яті з ієрархічними кільцевими шинами

Номер патенту: 112237

Опубліковано: 12.12.2016

Формула / Реферат

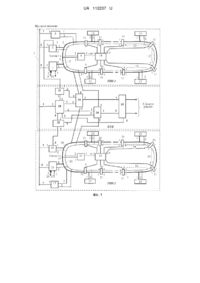

1. Інтелектуальна розподілена система пам'яті з ієрархічними кільцевими шинами, що містить підсистему інтелектуальної пам'яті першого рівня (ПІП-1), до складу якої входять системний контролер пам'яті, множина N блоків інтелектуальної пам'яті, кільцева шина, що складається з кільцевої шини даних і кільцевої шини управління, блок управління кільцевої шиною, локальна шина даних, система вводу/виводу даних, система вводу/виводу управляючих сигналів, ведучий процесор з КЕШ-пам'яттю, n керованих секторних роздільників кільцевої шини на n секторів, загальні для кільцевої шини даних і кільцевої шини управління, при цьому множина з N блоків інтелектуальної пам'яті поділяється також на секторні набори, кількість яких визначається як (n-1), кількість блоків інтелектуальної пам'яті в кожному секторному наборі визначається як N/(n-1), при цьому перший ввід/вивід і-го секторного роздільника з'єднаний з і-м сектором кільцевої шини даних, другий ввід/вивід з'єднаний з (і+1)-м сектором кільцевої шини даних, третій ввід/вивід з'єднаний з і-м сектором кільцевої шини управління, четвертий ввід/вивід з'єднаний з (і+1)-м сектором кільцевої шини управління, де 1£і£n, кожен j-й ввід/вивід вузла управління секторними роздільниками з'єднаний з п'ятим вводом/виводом відповідного j-гo секторного роздільника, де 1£j£n, (n+1) ввід/вивід з'єднаний з третім вводом/виводом блока управління кільцевої шиною, перший ввід/вивід якого з'єднаний з першим сектором кільцевої шини даних, другий його ввід/вивід з'єднаний з першим сектором кільцевої шини управління, перший ввід/вивід кожного m-го блока інтелектуальної пам'яті, де 1£m£N/(n-1), в кожному k-му секторному наборі з'єднаний з відповідним (k+1)-м сектором кільцевої шини даних, другий ввід/вивід з'єднаний з відповідним (k+1)-м сектором кільцевої шини управління, де 1£k£n-1, перший ввід/вивід блока службових функцій з'єднаний з першим сектором кільцевої шини даних, другий ввід/вивід з'єднаний з першим сектором кільцевої шини управління, третій ввід/вивід з'єднаний з локальною шиною даних, четвертий ввід/вивід системного контролера з'єднаний з першим сектором кільцевої шини даних, п'ятий ввід/вивід з'єднаний з першим сектором кільцевої шини управління, при цьому підсистема інтелектуальної пам'яті першого рівня також містить вузол управління секторними роздільниками, блок службових функцій підсистеми пам'яті першого рівня, що містить вузол управління службовими функціями підсистеми пам'яті, вузол розподілу адресного простору всієї інтелектуальної підсистеми пам'яті першого рівня по блоках інтелектуальної пам'яті (БІП-1), вузол розміщення даних по розподілених адресних просторах БІП-1, вузол розподілу програми користувача на частини і розміщення їх по процесорах БІП-1, перший інтерфейс для вводу/виводу даних і кодів адреси, другий інтерфейс для вводу/виводу керуючих сигналів, з'єднані із відповідними шиною даних і шиною управління першого сектора кільцевої шини, при цьому кожен секторний набір блоків інтелектуальної пам'яті (БІП-1) додатково містить локальну шину даних, причому перший ввід/вивід кожного БІП-1 з'єднаний з відповідним сектором кільцевої шини даних, другий ввід/вивід кожного БІП-1 з'єднаний з відповідним сектором кільцевої шини управління, яка відрізняється тим, що уведена підсистема інтелектуальної пам'яті другого рівня (ПІП-2), а також додатково уведено блок управління взаємодією інтелектуальних підсистем пам'яті різних рівнів (БУВ), який містить блок управління рівнями, перший і другий інтерфейси відповідно для передачі даних і управляючих сигналів між першими секторами кільцевих шин різних рівнів, а також два блоки синхронізації відповідно для даних і управляючих сигналів секторів кільцевої шини, при цьому перший і другий виходи блока управління рівнями підключені до першого входу інтерфейсу передачі даних і відповідно - до першого входу інтерфейсу передачі управляючих сигналів, перші виходи яких з'єднані з першими і другими входами даних і управляючих сигналів відповідного інтерфейсу для третього і інших рівнів, третій вхід якого підключений до третього виходу блока управління рівнями, перший вхід якого підключений до четвертого входу локальної шини ("Передача інформації між рівнями"), а його п'ятий вихід підключений до першого входу першого блока синхронізації, другий вхід якого з'єднаний з третім виходом блока службових функцій ПІП-1, а його другий вихід з'єднаний з другим входом інтерфейсу передачі даних між рівнями, треті входи/виходи якого підключені до першого сектора шини даних ПІП-1, кільцева шина управління першого сектора якої з'єднана з третім входом інтерфейсу передачі між рівнями керуючих сигналів, другий вхід якого підключений до першого виходу другого блока синхронізації, другий вхід якого з'єднаний з третім виходом блока службових функцій ПІП-2, другий вхід/вихід інтерфейсу передачі керуючих сигналів між рівнями з'єднаний з кільцевою шиною керуючих сигналів першого сектора ПІП-2, кільцева шина даних першого сектора якої з'єднана з четвертим входом/виходом інтерфейсу, ПІП-2 містить також системний контролер пам'яті, множину М блоків інтелектуальної пам'яті, кільцеву шину, що складається з кільцевої шини даних і кільцевої шини управління і містить m керованих секторних роздільників, загальних для обох шин і розділяючих їх на m секторів, блок управління кільцевою шиною, блок управління роздільниками, локальна шина даних, системний ввід/вивід даних, системний ввід/вивід управляючих сигналів, ведучий процесор з КЕШ-пам'яттю, при цьому множина з М блоків інтелектуальної пам'яті поділяється також на секторні набори, кількість яких визначається як (m-1), кількість блоків інтелектуальної пам'яті в кожному секторному наборі визначається як М/(m-1), при цьому перший ввід/вивід j-гo секторного роздільника з'єднаний с q-м сектором кільцевої шини даних, другий ввід/вивід з'єднаний з (q+1)-м сектором кільцевої шини даних, третій ввід/вивід з'єднаний з q-м сектором кільцевої шини управління, четвертий ввід/вивід з'єднаний з (q+1)-м сектором кільцевої шини управління, де 1£q£m, кожен z-й ввід/вивід вузла управління секторними роздільниками з'єднаний з п'ятим вводом/виводом відповідного m-го секторного роздільника, де 1£z£m, (z+1) ввід/вивід з'єднаний з третім вводом/виводом блока управління кільцевої шиною, перший ввід/вивід якого з'єднаний з першим сектором кільцевої шини даних, другий його ввід/вивід з'єднаний з першим сектором кільцевої шини управління, перший ввід/вивід кожного блока інтелектуальної пам'яті в кожному k-му секторному наборі з'єднаний з відповідним сектором кільцевої шини даних, а його другий ввід/вивід з'єднаний з відповідним сектором кільцевої шини управління, перший ввід/вивід блока службових функцій з'єднаний з першим сектором кільцевої шини даних, другий ввід/вивід з'єднаний з першим сектором кільцевої шини управління, третій ввід/вивід з'єднаний з п'ятим входом локальної шини даних ("Запуск процесів"), четвертий ввід/вивід системного контролера з'єднаний з першим сектором кільцевої шини даних, п'ятий ввід/вивід з'єднаний з першим сектором кільцевої шини управління, а третій вхід системного контролера ПІП-2 підключений до відповідного шостого входу ("Запуск ПІП-2") локальної шини.

2. Інтелектуальна розподілена система пам'яті з ієрархічними кільцевими шинами за п. 1, яка відрізняється тим, що кожен секторний набір першого ПІП-1 і другого ПІП-2 рівнів має блоки секторної пам'яті, мультиплексор і демультиплексор, набір регістрів, що містить регістри РгА, РгВ, РгС і PгD, контролер управління пам'яттю секторного набору і процесорний елемент, а також інтерфейс секторного набору, при цьому перші входи і другі виходи інтерфейсу кожного секторного набору підключені до кільцевої шині даних відповідного сектора, а його треті входи з'єднані з секторною кільцевою шиною управління, перший вхід/вихід управляючих сигналів інтерфейсу з'єднаний з першим входом/виходом контролера управління сектором, з першим входом мультиплексора і з першим входом секторного блока пам'яті, другий вхід якого з'єднаний з другим виходом контролера управління секторною пам'яттю, шостий вхід/вихід керуючих сигналів інтерфейсу з'єднаний з першим входом демультиплексора і з першим входом процесорного елемента, перший вихід якого з'єднаний з третім входом блока пам'яті сектора, другий вихід якого з'єднаний з другим входом процесора, другий і третій виходи інтерфейсу секторного набору з'єднані з відповідними входами регістрів РгА та РгВ, перші і другі виходи яких підключені відповідно до других і третіх входів мультиплексора, перші виходи якого з'єднані з четвертими входами блока пам'яті сектора, перші виходи якого з'єднані з другими входами демультиплексора, перші і другі виходи якого підключені відповідно до перших і других входів регістрів РгС і PгD, перші і другі виходи яких з'єднані відповідно з четвертими і з п'ятими входами інтерфейсу секторного набору, другий і третій входи/виходи процесорного елемента підключені до кільцевої шині даних і відповідно до кільцевої шині управління сектора.

3. Інтелектуальна розподілена система пам'яті з ієрархічними кільцевими шинами за п. 1, яка відрізняється тим, що в блок службових функцій ПІП-1 і ПІП-2, додатково введені вузол синхронізації внутрішніх процесів кільцевої шини, інтерфейс для зв'язку з кільцевої шиною даних і вузол управління читанням/записом даних та програм, при цьому перші, другі, треті і четверті виходи вузла синхронізації внутрішніх процесів кільцевої шини підключені відповідно до перших входів вузла управління читання/запису даних і програм, вузла управління розподілом адресного простору, вузла управління розподілом даних і вузла управління розподілом програм користувача по процесорах, при цьому перші, другі, треті і четверті виходи вузла управління службовими функціями підключені відповідно до других входів вузла управління читання/запису даних і програм, вузла управління розподілом адресного простору, вузла управління розподілом даних і вузла управління розподілом програм користувача по процесорам, перші виходи яких з'єднані відповідно з першим, другим, третім і четвертим входами інтерфейсу для вводу/виводу керуючих сигналів перших секторів кільцевих шин ПІП-1 і ПІП-2, перші виходи яких підключені відповідно до перших секторів кільцевих шин керуючих сигналів, при цьому другі виходи вузла розподілу адресного простору, вузла розподілу даних і вузла розподілу програм користувача по процесорах з'єднані відповідно з першими, другими і третіми входами інтерфейсу введення/виводу даних, коду адреси та програм перших секторів кільцевих шин, перші виходи яких з'єднані відповідно з кільцевими шинами даних ПІП-1 і ПІП-2 перших секторів, при цьому другі входи вузла синхронізації внутрішніх процесів кільцевої шини, інтерфейсу для зв'язку з кільцевою шиною даних і вузла синхронізації внутрішніх процесів кільцевої шини з'єднані з другім виходом локальної шини.

4. Інтелектуальна розподілена система пам'яті з ієрархічними кільцевими шинами за п. 1, яка відрізняється тим, що для ПІП-1 і ПІП-2 кожен секторний роздільник представлений у вигляді матриці елементів схем, що містить перший стовпець елементів "2 І", другий стовпець елементів "3 І", третій стовпець - тригерних схем "Tгj", четвертий стовпець елементів "3 І" , п'ятий стовпець елементів "2 І", а також додатковий рядок тригерних схем і елементів "2 І", при цьому кількість рядків матриці елементів визначено кількістю розрядів кільцевої шини даних і кільцевої шини управління, перші входи всіх тригерів сигналів управління стовпця тригерних схем з'єднані між собою і підключені до кільцевої шини, перші входи всіх тригерів сигналів даних стовпця тригерних схем з'єднані між собою і підключені до кільцевої шини даних, другі входи тригерів стовпця тригерних схем з'єднані між собою і підключені до відповідного входу/виходу (сигнал "Дозвіл читання/запису") вузла управління секторними роздільниками, а треті входи всіх тригерів (сигнал "Скидання") також з'єднані між собою і підключені до вузла управління секторними роздільниками, другі входи елементів "3 І" другого і окремо четвертого стовпців в кожному стовпці з'єднані між собою і підключені до відповідних виходів елементів "2 І", що належать відповідно другому і четвертому стовпцям, перші входи яких з'єднані з виходами відповідних тригерів додаткового тригерного рядка, другі входи яких з'єднані з відповідними виходами (команда "Зчитування") вузла управління секторними роздільниками, вихід кожного тригера в стовпцях тригерних схем кожного рядка з'єднаний з першим входом елемента "3 І" відповідного рядка другого стовпця і з першим входом елемента "3 І" того ж самого рядка четвертого стовпця, треті входи кожного елемента "3 І" другого стовпця і окремо четвертого стовпця з'єднані і підключені до відповідного виходу елемента "2 І" додаткового тригерного рядка, перший вхід якого з'єднаний з виходом відповідного тригера додаткового тригерного рядка, а другий вхід підключений до відповідного виходу ("Дозвіл передачі") вузла управління секторними роздільниками, виходи елемента "3 І" кожного рядка другого стовпця з'єднані з відповідними першими входами елементів "2 І" першого стовпця, другі входи яких з'єднані і підключені до виходу відповідного елемента "2 І" додаткового тригерного рядка, перший вхід якого з'єднаний з виходом тригера додаткового тригерного рядка, другий вхід якого підключений до відповідного виходу вузла управління секторними роздільниками "Передача інформації від q-го роздільника наліво (проти годинникової стрілки) до (q+1)-го роздільника", виходи елемента "3 І" кожного рядка четвертого стовпця з'єднані з відповідними першими входами елемента "2 І" п'ятого стовпця, другі входи яких з'єднані і підключені до відповідного виходу елемента "2 І" додаткового рядка тригерів, перший вхід якого з'єднаний з виходом відповідного тригера додаткового тригерного рядка, другий вхід якого з'єднаний з відповідним виходом ( "Передача інформації від q-го роздільника направо (за годинниковою стрілкою) до (q-1)-го роздільника") вузла управління секторними роздільниками, при цьому кожен вихід елемента "2 І" першого стовпця і кожен вихід елемента "2 І" п'ятого стовпця підключені відповідно до кільцевої шині даних і шини управління (q+1) і (q-1) секторів, другі входи всіх елементів "2 І" додаткового рядка тригерів з'єднані з відповідним виходом ("Сигнал синхронізації") вузла управління секторними роздільниками, а треті входи з першого по п'ятий всіх тригерів додаткового рядка тригерів з'єднані з відповідними виходами (сигнали" Скидання") вузла управління секторними роздільниками.

5. Інтелектуальна розподілена система пам'яті з ієрархічними кільцевими шинами за п. 1, яка відрізняється тим, що блок управління кільцевої шиною першого ПІП-1 та другого ПІП-2 рівнів містить вузол інтерфейсу з кільцевої шиною, вузол аналізу і обробки керуючого пакета, вузол управління сигналами скидання тригерів, вузол управління синхронізацією, вузол управління читанням/записом інформації, вузол управління передачею інформації в (n-1) роздільник, вузол управління в передачею інформації в (n+1) роздільник, вузол управління записом інформації в третій стовпець n-го роздільника, при цьому перші і другі входи інтерфейсу з'єднані відповідно з кільцевої шиною управління і кільцевої шиною даних першого сектора, перший вихід інтерфейсу з'єднаний з першим входом вузла управління синхронізацією, перший, другий, третій і четвертий виходи якого підключені відповідно до перших входів вузла управління читанням/записом інформації, вузла управління передачею інформації в (n-1) роздільник, вузла управління передачею інформації в (n+1) роздільник, вузла управління записом інформації в третій стовпець n-го роздільника, п'ятий вихід вузла управління синхронізацією підключений до першого входу вузла аналізу і обробки управляючого пакета, другий вхід якого з'єднаний з другим виходом інтерфейсу, перший, другий, третій і четвертий виходи вузла аналізу і обробки управляючого пакета підключені відповідно до других виходів вузла управління читанням/записом інформації, вузла управління передачею інформації в (n-1) роздільник, вузла управління передачею інформації в (n+1) роздільник, вузла управління записом інформації в третій стовпець q-го роздільника, перший вихід вузла управління сигналами скидання з'єднаний з третім входом вузла управління зчитуванням/записом, а його другі, треті і четверті виходи з'єднані відповідно з третіми входами вузла управління передачею інформації в (n-1) роздільник, вузла управління передачею інформації в (n+1) роздільник, вузла управління записом інформації в третій стовпець n-го роздільника, виходи яких підключені до відповідних входів n-го роздільника, при цьому шостий вихід вузла управління синхронізацією з'єднаний з першим входом вузла управління сигналами скидання тригерів, другий вхід якого підключений до п'ятого виходу вузла аналізу і обробки керуючого пакета.

Текст