Спосіб контролю та діагностування цифрових схем

Номер патенту: 21399

Опубліковано: 02.12.1997

Автори: Перевозніков Сергій Іванович, Арапова Олена Михайлівна, Байда Микола Прокопович

Формула / Реферат

Способ контроля и диагностирования цифровых схем, заключающийся в том, что на искусственно выделенные фрагменты схем объекта диагностирования подают тестовые воздействия снимают ответные реакции и сравнивают их с эталонными значениями, отличающийся тем, что в объекте диагностирования искусственно выделяют фрагменты схем из однотипных элементов, которые соединяют последовательно и замыкают цепью обратной связи с помощью временных искусственных цепей передачи тестовых сигналов, поочередно, на каждый искусственно созданный фрагмент, подают наборы логических сигналов, причем сначала подают сигналы, обеспечивающие условия электрической защиты элементов объекта диагностирования, затем подают сигналы, активизирующие пути прохождения процесса генерации со входа на выход каждого элемента из выделенного фрагмента, затем подают сигналы, разрешающие процессы периодической смены сигналов в образованном искусственным способом контуре обратной связи, регистрируют смену полярности сигналов в искусственно образованном контуре, путем подсчета числа импульсов и, по результатам сравнения с контрольной суммой судят об исправности элементов искусственно созданного фрагмента.

Текст

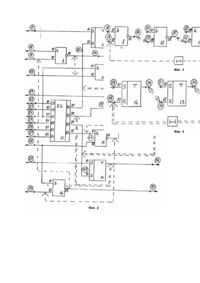

Изобретение относится к контрольноизмерительной технике и может быть использовано для автоматического контроля и диагностирования цифровых устройств. Известен способ поиска дефектов в цифровых устройствах, при котором используются псевдонаучные многоразрядные кодовые наборы, состоящие из логических нулей и единиц в каждом разряде. Множество таких кодовых наборов подают последовательно на информационные и управляющие входы краевого разъема диагностируемого цифрового блока. Исправность цифрового блока фиксируют по совпадению ответных реакций с эталонными значениями (А.с. СССР №1260884, кл. G01R31/28, 1986). Однако практическое применение такого способа с целью обнаружения и поиска места дефектов в цифровом блоке имеет ряд существенных недостатков, связанных, прежде всего, с большим объемом подаваемой на блок тестовой информации, с вопросами устранения подачи запрещенных кодовых наборов, а также с малой глубиной поиска места дефектов. При этом уточнение места дефектов осуществляется, как правило, либо специальным поисковым зондом, управляемым в диалоговом режиме от ЭВМ, либо ручным способом. Известен способ диагностирования цифровых блоков, заключающийся в последовательной проверке каждого отдельного элемента, входящего в состав цифрового блока. Способ реализуется подачей детерминированных тестовых наборов непосредственно на входы каждого элемента внутренней структуры цифрового блока и снятием ответных реакций прямо с их выходов. При этом заключение об исправности каждого элемента производится по результатам сравнения полученных ответных реакций с эталонными значениями. Для подачи тестовых наборов на входы проверяемых элементов и снятия ответных реакций используется специальное игольчатое контактное устройство. В целях предотвращения электрического повреждения связанных элементов диагностируемого блока устанавливают потенциал логической единицы на входах тех элементов, которые непосредственно соединены со входами проверяемого элемента условия электрической защиты элементов (Байда Н.П., Кузьмин И.В., Шпилевой В.Т. Микропроцессорные системы поэлементного диагностирования РЭА. - М.: Радио и связь, 1987. - С.256, гл.1, §1.3, гл.4, §4,1; А.с. СССР №1108451, кл. G06G11/00, 1985). При этом длительность наводимых тестовых сигналов во внутренние узлы связанных элементов не должна превышать одной секунды (используется режим наведения сигнала логического нуля на входы элементов, находящихся в состоянии логической единицы и непосредственно связанных со входами проверяемого элемента). Установленные на входах таких элементов потенциалов логической единицы является начальными условиями диагностирования (НУД) каждого проверяемого элемента. Недостатком такого способа является низкое быстродействие процесса контроля, обусловленное необходимостью проведения последовательного индивидуального тестирования всех элементов цифрового блока в статическом режиме (на малых частотах). Причем для каждого элемента требуется синтезировать специальный тест с учетом НУД. Наиболее близким к заявляемому техническому решению является способ контроля и диагностирования цифровых схем в соответствии с которым выбираются заданные элементы объекта контроля, из которых при помощи искусственных связей образуются фрагменты схем, на которых подают входные тестовые воздействия, затем снимают входные реакции и сравнивают их с эталоном, по результатам сравнения судят об исправности элементов (DESIGN FOR TESTABILITY - A SURVEY, THOMAS W. WILIIAMS, MEMBER, IEEE AND KENNETH P. PARKER, MEMBER, IEEE, PROCEEDINGS OF THE IEEE, VOL.71, NO.1 JANUARY, 1983, PAGE 98 - 111, FIG.28, 29). Недостатком известного способа является сложная процедура контроля. В основу изобретения поставлена задача создания способа контроля и диагностирования цифровых схем, в котором за счет декомпозиции элементов цифровых схем на тестируемые фрагменты, путем введения в структуру цифровой схемы временных искусственных цепей передачи тестовой информации между определенными внутренними контрольными точками обеспечивается организация структур из последовательно связанных однотипных элементов, выводы которых дополнительно замыкаются цепями временных искусственных обратных связей. Подача на искусственно созданные фрагменты наборов логических сигналов способствует возникновению процессов генерации, в каждом таком контуре. Т.е. подобное временное объединение однотипных элементов в искусственный контур обратной связи эквивалентно синтезу искусственного генератора периодических сигналов внутри цифрового объекта. Регистрация процесса генерации позволяет судить об исправности элементов искусственного контура, что упрощает процедуру контроля и диагностирования. Для повышения достоверности контроля в каждом искусственном контуре, средствами диагностирования, осуществляют регулировку частоты генерации сигналов. Для ускорения процесса тестового контроля цифровых схем предлагаемым методом целесообразно синтезировать меньшее число генераторов сигналов с максимально возможным числом элементов в составе каждого из них. По окончании процесса тестирования фрагмента схемы искусственные цепи размыкаются и вновь участвуют в образовании очередного контролируемого фрагмента, путем замыкания определенных внутренних контрольных точек. После чего процесс синтеза искусственных фрагментов повторяется до полной проверки объекта диагностирования. Элементы объекта диагностирования, не вошедшие в состав искусственно создаваемых фрагментов, проверяются индивидуально известными способами, например поэлементно. Таким образом, введение в структуру объекта диагностирования искусственных цепей передачи тестовой информации между выводами отдельных элементов позволяет синтезировать фрагменты цифровой схемы удобные для целей контроля, сократив при этом общее время диагностирования. Поставленная задача решается тем, что в известном способе контроля схем, заключающемся в том, что на искусственно выделенные фрагменты схем объекта диагностирования подают тестовые воздействия, снимают ответные реакции и сравнивают их с эталонными согласно изобретению в объекте диагностирования искусственно выделяют фрагменты схем, из однотипных элементов, которые соединяют последовательно и замыкают цепью обратной связи с помощью временных искусственных цепей передачи тестовых сигналов. Поочередно на каждый искусственно созданный фрагмент подают наборы логических сигналов, причем сначала подают сигналы, обеспечивающие условия электрической защиты элементов объекта диагностирования, затем подают сигналы, активизирующие пути прохождения процесса генерации со входа на выход каждого элемента из выделенного фрагмента, затем подают сигналы, разрешающие процессы периодической смены сигналов в образованном искусственным способом контуре обратной связи, регистрируют смену полярности сигналов в искусственно образованном контуре, путем подсчета числа импульсов и, по результатам сравнения с контрольной суммой судят об исправности элементов искусственно созданного фрагмента объекта диагностирования. На фиг.1 показано устройство для осуществления способа контроля и диагностирования; на фиг.2 объект диагностирования; на фиг.3 и 4 - искусственно образованные фрагменты схем из однотипных элементов объекта диагностирования. Устройство для осуществления способа (фиг.1) содержит управляющую ЭВМ 1, регистр 2, диагностируемую цифровую схему 3, Kразрядный счетчик 4, K-разрядную схему сравнения 5, таймерное устройство 6, коммутатор 7. Элементы 2 - 6 (фиг.1) - см.: Тарабрин В.В., Лунин Л.Ф., Смирнов Ю.Н. и др. Интегральные микросхемы / Под ред. Тарабрина В.В. - М.: Радио и связь, 1984. - 528с. Элементы 1, 7 (фиг.1) - см.: Байда Н.П., Кузьмин И.В., Шпилевой В.Т. Микропроцессорные системы поэлементного диагностирования РЭА. М.: Радио и связь, 1987. - 256с. Системная магистраль управляющей ЭВМ 1 соединена со входами параллельной записи данных регистра 2, выходы регистра 2 соединены с основными входами объекта диагностирования 3, выходы объекта диагностирования 3 подключены к K-разрядному счетчику 4, управляющие входы счетчика 4, K-разрядной схемы сравнения 5, а также таймерного устройства 6 соединены с системной магистралью ЭВМ 1, выход счетчика 4 соединен с K-разрядной схемой сравнения 5, выход таймерного устройства 6 соединен со входом схемы сравнения 5, выход схемы сравнения 5 соединен с системной магистралью ЭВМ 1, вход коммутатора 7 соединен с системной магистралью управляющей ЭВМ 1, выход коммутатора 7 соединен с объектом диагностирования 3. Диагностируемая цифровая схема (фиг.2) содержит первый элеменят 2И-НЕ 8, элемент 4И 9, второй элемент 2И-НЕ 10, регистр RG 11, первый элемент - триггер RS 12, второй элемент триггер RS 13, третий элемент триггер RS 14, третий элемент 2И-НЕ 15, элемент 2И 16. Выход первого элемента 2И-НЕ соединен с первым входом элемента 4И 9, выход второго элемента 2И-НЕ 10 соединен со вторым входом элемента 4И 9, первый вход (вывод седьмой) элемента RG 11 соединен со вторым входом первого элемента RS12, второй выход (вывод восьмой) элемента RG 11 соединен со вторым входом второго элемента RS 13, третий выход (вывод девятый) элемента RG 11 соединен со вторым входом третьего элемента RS 14, четвертый выход (вывод десятый) элемента RG 11 соединен с первым входом третьего элемента 2И-НЕ 15, выход третьего элемента 2И-НЕ 15 соединен с третьим и четвертым входами элемента 4И 9, первый вход первого элемента RS 12, первый и второй входы первого элемента 2ИНЕ 8, второй вход второго элемента 2И-НЕ, первый вход второго элемента RS 13, первый, второй, третий и первый вход второго элемента 2И-НЕ 10, четвертый, пятый, шестой входы элемента RG 11, второй вход третьего элемента 2И-НЕ 15 и первый вход элемента 2И 16, первый вход третьего элемента RS 14 соединены соответственно с первым, вторым, ..., четырнадцатым входами регистра 2. Способ контроля и диагностирования реализуется следующим образом. Сначала цифровая схема, как объект исследования, декомпозируется на тестируемые фрагменты в следующем порядке: 1. Из всех элементов, составляющих объект диагностирования, выделяют n-комбинированных элементов и m-элементов триггерного типа, для которых рассчитываются векторы специальных тестовых сигналов. Подача таких векторов на объект установит вектор начальных условий диагностирования (НУД) для выбранных элементов. 2. Фиксируют номера внутренних контрольных точек цифрового объекта, которые в дальнейшем будут участвовать в последовательном соединении n-элементов комбинационного типа и m-элементов триггерного типа. При этом зафиксированный выход первого комбинационного элемента будет соединен с входом второго комбинационного элемента, выход второго комбинационного элемента будет соединен со входом третьего комбинационного элемента и т.д., а выход n - го комбинационного элемента будет соединен со вторым входом первого комбинационного элемента. Зафиксированный выход первого триггера будет соединен со входом второго триггера, выход второго триггера будет соединен со входом третьего триггера и т.д., а выход m - го триггера будет соединен со вторым входом первого триггера. 3. Рассчитывают векторы сигналов (вектор активизации) для каждого из n-элементов комбинационного типа и m-триггеров, подача которых на входы этих элементов во внутренние узлы цифровой схемы не будут блокировать передачу тестовой информации со входа каждого элемента на его выход (эти входы элементов, для которых подаются векторы активизации, не участвуют в последовательном соединении рассматриваемых элементов в тестируемые фрагменты). 4. Рассчитываются значения сигналов, подача которых на первый элемент комбинационного типа и на первый элемент триггерного типа будут блокировать процессы генерации в каждом синтезируемом фрагменте объекта диагностирования. 5. Выбирается алгоритм поиска дефектов среди n-элементов комбинационного типа и mтриггеров. Осуществив декомпозицию цифровой схемы на тестируемые фрагменты, реализуют поиск дефектов в каждом отдельном из выделенных фрагментов в следующем порядке: 1. Для каждого из n-комбинационных элементов и m-триггеров подают векторы их НУД. 2. На первый элемент комбинационного типа из n выбранных и на первый триггер из m триггеров подают сигналы блокирующие процессы генерации в каждом фрагменте. 3. Средствами диагностирования замыкают (n + m) искусственными цепями внутренние контрольные точки объекта исследования, зафиксированные ранее при декомпозиции цифровой схемы на фрагменты. 4. Снимают сигналы, блокирующие процессы генерации в каждом искусственно созданном фрагменте комбинационного и триггерного типа. 5. Измеряют периодическую смену сигналов в созданных искусственным образом контурах обратных связей путем подсчета числа импульсов на выходе n - го элемента комбинационного типа и на входе m - го триггера. 6. Сравнивают числа зарегистрированных импульсов с контрольной суммой для каждого типа элементов. 7. Если есть дефект, то осуществляют его поиск согласно выбранному алгоритму диагностирования. 8. Выдают диагностическое сообщение. Рассмотрим реализацию предлагаемого способа на примере диагностирования цифровой схемы 3 представленной на фиг.2. Для одновременного тестирования первого элемента 2И-НЕ 8, второго элемента 2И-НЕ 10, третьего элемента 2И-НЕ 15, а также для элемента 2И 16 рассчитываются векторы сигналов, являющиеся начальными условиям их диагностирования. Аналогичные значения сигналов рассчитываются для группы триггеров, состоящей из первого элемента RS 12, второго элемента RS 13 и третьего элемента RS 14. Для этого необходимо на основные входы цифровой схемы (с семнадцатого по тридцатый вход) подать потенциал логической единицы. Для объединения рассматриваемой группы комбинационных элементов и группы триггеров в тестируемые фрагменты зафиксируем номера внутренних контрольных точек (КТ), которые в дальнейшем будут замкнуты искусственными цепями коммутирующего устройства. Это второй вход первого элемента 2И-НЕ 8 - КТ 19, выход первого элемента 2И-НЕ 8 - КТ 36, второй вход второго элемента 2И-НЕ 10 - КТ 20, выход второго элемента 2И-НЕ 10 - КТ 37, первый вход третьего элемента 2И-НЕ 15 - КТ 41, выход третьего элемента 2И-НЕ 15 - КТ 42, второй вход элемента 2И 16 - КТ 30, выход элемента 2И 16 - КТ 35; второй вход первого элемента RS 12 - КТ 38, выход второго элемента RS 13 - КТ 33, второй вход второго элемента RS 13 - КТ 39, выход третьего элемента RS 14 - КТ 34, выход первого элемента RS12 - КТ 31, второй вход третьего элемента RS 14 - КТ 40. В регистр 2 (фиг.1) из управляющей ЭВМ 1 записывается ранее рассчитанный вектор логических сигналов, который по команде (из ЭВМ 1) выдается на основные входы цифровой схемы 3 и устанавливает необходимые сигналы, разрешающие процесс генерации, на входах каждого из выбранных комбинационных элементов и триггеров. В K-разрядную схему сравнения 5 записывается из ЭВМ 1 код контрольной суммы. Затем на выход элемента 2И 16 (КТ 35) подаются от управляющей ЭВМ 1 через коммутирующее устройство 7 (фиг.1) потенциалы логического нуля, которые блокируют процесс генерации сигналов в искусственно созданном фрагменте. Замыкают с помощью шин коммутирующего устройства 7 внутренние КТ цифровой схемы 3. Первая искусственная цепь замыкает КТ 36 и КТ 20, вторая искусственная цепь замыкает КТ 37 и КТ 41, третья цепь замыкает КТ 42 и КТ 30, четвертая - КТ 35 и КТ 19. Для контроля синтезированного фрагмента из комбинационных элементов по команде из управляющей ЭВМ 1 счетчик 4 устанавливается в исходное нулевое состояние. Выход элемента 2И 16 подключается ко входу счетчика 4. Затем снимаются потенциалы логического нуля, блокирующие процесс генерации в созданном комбинационном фрагменте (фиг.3). В процессе смены полярности сигналов, импульсы с выхода элемента 2И 16 поступают на вход счета на увеличение K-разрядного счетчика 4 - й изменяют его исходное состояние. Процесс генерации проходит с выхода первого элемента 2И-НЕ 8 (КТ 36) по первой искусственной цепи на второй вход второго элемента 2И-НЕ 10 (КТ 20) с выхода второго элемента 2И-НЕ 10 (КТ 37) по второй искусственной цепи поступает на первый вход третьего элемента 2И-НЕ 15 (КТ 41), с выхода третьего элемента 2И-НЕ 15 (КТ 42) по третьей искусственной цепи поступает на второй вход элемента 2И 16 (КТ 30), с выхода элемента 2И 16 (КТ 35) по четвертой искусственной цепи поступает на второй вход первого элемента 2ИНЕ 8 (КТ 19). В четвертую искусственную цепь обратной связи включен средствами диагностирования элемент задержки, представляющий собой, например, программируемый одновибратор, который согласовывает скорость процесса генерации сигналов в синтезируемом контуре с возможностями его достоверного контроля схемой K-разрядного счетчика 4. После установления на всех выходах K-разрядного счетчика 4 сигналов логической единицы, состояние выхода элемента 5 изменится с логической единицы на противоположное. Сигнал логического нуля с выхода K-разрядной схемы сравнения 5 поступает в управляющую ЭВМ 1 по выводам, соединенных с цепями искусственных связей в процессе генерации и свидетельствует об окончании процедуры контроля группы элементов комбинационного фрагмента. Аналогично, подключив выход элемента RS 12 (КТ 31) ко входу счетчика 4, который установлен в исходное нулевое состояние, контролируются элементы триггерного фрагмента (фиг.4). Для этого, предварительно по команде из управляющей ЭВМ 1, создают пятую искусственную цепь замкнув КТ 34 и КТ 39, шестую искусственную цепь, замкнув КТ 33 и КТ 38, седьмую цепь - КТ 31 и КТ 40. В седьмую искусственную цепь обратной связи включен программируемый элемент задержки. Сняв блокирующий сигнал, который был подан в КТ 31 (уровень логического нуля), регистрируют генерацию сигналов в контуре. При этом импульсы проходят с выхода третьего элемента RS 14 (КТ 34) по пятой искусственной цепи и поступают на второй вход второго элемента RS 13 (КТ 39), с выхода второго элемента RS 13 (КТ 33) по шестой искусственной цепи поступают на второй вход первого элемента RS12 (КТ 38), с выхода первого элемента RS 12 (КТ 31) по седьмой искусственной цепи импульсы поступают на второй вход третьего элемента RS 14 (КТ 40). Время контроля ограничено периодом опроса управляющей ЭВМ 1, но в зависимости от сложности синтезируемого фрагмента схемы оно может быть рассчитано и заранее записано в таймерное устройство 6. При этом, синхронно с началом процесса генерации (снятие сигнала блокировки) в контуре обратной связи, от управляющей ЭВМ 1 на таймерное устройство 6 выдается, сигнал на запуск таймера времени. После сравнения кода, записанного в таймерное устройство 6, с текущим кодом таймера процесс контроля фрагмента схемы прекращается, с выхода K-разрядного счетчика 4 установившийся вектор сигналов поступает на входы K-разрядной схемы сравнения 5. В следующем такте машинного времени идет обработка результатов тестирования управляющей ЭВМ 1. Периодическая смена сигналов в контуре представляет собой динамический процесс. Частота смены полярности сигналов тем выше, чем меньше число элементов входит в искусственно созданный генератор (при этом она зависит от быстродействия самих элементов). Поэтому с целью адаптации средств поэлементного тестирования к различным объектам контроля, в структуру каждого созданного генератора вводится (средствами диагностирования) элемент задержки. Вводимый элемент задержки может быть представлен, например RC-цепью или программируемым одновибратором. Такой элемент позволяет согласовывать динамические возможности управляющей ЭВМ с цифровым объектом в процессе поиска дефектного элемента каждого тестируемого контура. При наличии дефектов в цифровом объекте, когда например, на входе одного из элементов проверяемого контура присутствует постоянно уровень логической единицы или логического нуля, генерации сигналов не будет. В этом случае поиск неисправного элемента осуществляется, например, поочередным отключением элементов из контура за счет изменения адресов подключения искусственных обратных связей и соблюдения принципа нечетного числа инверсий в каждом вновь образованном фрагменте. С целью исключения внесения в объект контроля вторичных дефектов в процессе тестирования, в состав каждой искусственно созданной цепи вводится токоограничивающий резистор.

ДивитисяДодаткова інформація

Автори англійськоюBaida Mykola Prokopovych, Perevoznikov Serhii Ivanovych, Arapova Olena Mykhailivna

Автори російськоюБайда Николай Прокопович, Перевозников Сергей Иванович, Арапова Елена Михайловна

МПК / Мітки

МПК: G01R 31/28

Мітки: спосіб, схем, контролю, цифрових, діагностування

Код посилання

<a href="https://ua.patents.su/5-21399-sposib-kontrolyu-ta-diagnostuvannya-cifrovikh-skhem.html" target="_blank" rel="follow" title="База патентів України">Спосіб контролю та діагностування цифрових схем</a>

Попередній патент: М’ясний фарш для виготовлення варених ковбасних виробів

Наступний патент: Гідро-вітроколесо з орієнтаційно-змінною парусністю

Випадковий патент: Механізм для примусової вертикальної подачі відходів у реактор