Спосіб контролю та діагностування цифрових схем

Номер патенту: 14810

Опубліковано: 18.02.1997

Автори: Перевозніков Сергій Іванович, Байда Микола Прокопович, Арапова Олена Михайлівна

Формула / Реферат

Способ контроля и диагностирования цифровых схем, заключающийся в том, что на входы искусственно выделенных фрагментов схем объекта диагностирования подают тестовые воздействия, регистрируют выходные ответные реакции и сравнивают их с эталонными значениями, отличающийся тем, что на входы искусственно выделенных фрагментов схем из однотипных элементов перед тестовыми воздействиями подают сигналы, устанавливающие условия электрической защиты элементов проверяемого устройства, затем измеряют значения сигналов на входах тестируемых элементов, после чего с помощью программируемого устройства коммутации замыкают элементы выделенной группы параллельно между собой, и на входы образованной параллельной структуры подают тестовые воздействия, соответствующие конкретному типу элементов.

Текст

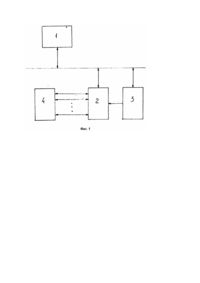

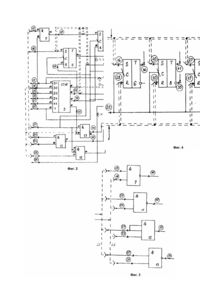

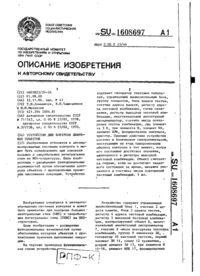

Изобретение относится к контрольноизмерительной технике и может быть использовано для автоматического контроля и диагностирования цифровых устройств. Наиболее близким техническим решением к заявляемому способу является способ контроля цифровых схем, заключающийся в том, что на входы искусственно созданных фрагментов контролируемой схемы подают входные тестовые воздействия, регистрируют выходные ответные реакции, сравнивают их с эталонными значениями, по результатам сравнения судят об исправности элементов схемы. Однако суть проводимого контроля фрагментов цифровых схем (согласно прототипу) сводится фактически к поочередному тестированию последовательно соединенных между собой разнотипных элементов, составляющих выделенный искусственным образом фрагмент объекта диагностирования. При этом, как для поиска места неисправного элемента (при наличии дефекта), так и для синтеза теста любого фрагмента необходимо учитывать функциональные особенности последовательно включенных между собой разнотипных элементов, образующих его структуру, что несомненно усложняет процесс подготовки программ контроля цифрового устройства. В основу изобретения поставлена задача создания способа контроля и диагностирования цифровых схем, в котором за счет декомпозиции элементов цифровых схем на тестируемые фрагменты путем временного объединения элементов цифровой схемы с помощью искусственных токоограничивающих цепей передачи тестовой информации между определенными внутренними контрольными точками объекта обеспечивается организация параллельных структур, удобных для целей контроля и диагностирования. Программа тестирования каждого образованного фрагмента схемы представляет собой тест для элементов, составляющих параллельную структуру. Такой тест подается на фрагмент только один раз. Анализ ответных реакций на выходах элементов такого фрагмента учитывает их функциональные особенности. По окончании процесса тестирования фрагмента схемы искусственные цепи размыкаются и вновь участвуют в образовании очередного контролируемого фрагмента путем замыкания определенных внутренних контрольных точек. После чего процесс синтеза искусственных фрагментов повторяется до полной проверки объекта диагностирования. И за счет этого экономится общее время тестирования объекта в целом (уменьшение времени), а также (при наличии дефектов) путем поочередного отключения каждого из параллельно соединенных элементов указывается место неисправного элемента, что существенно упрощает процедуру контроля и диагностирования цифровых схем. Эффективность предлагаемого способа наиболее значительна, когда объединяется в каждый искусственный фрагмент схемы максимально возможное число элементов. Элементы, "не попавшие" в тестируемые фрагменты, проверяются индивидуально известными способами, например, поэлементно. Поставленная задача решается тем, что в известном способе контроля цифровых схем, заключающимся втом, что в контролируемой схеме искусственно выделяются фрагменты схем, на которые подают входные тестовые воздействия, регистрируют ответные реакции и сравнивают их с эталонными согласно изобретению в объекте диагностирования искусственно выделяются фрагменты схем из однотипных элементов, на которые сначала подают сигналы, устанавливающие условия электрической защиты элементов проверяемого устройства, затем измеряют значения сигналов на входах тестируемых элементов с целью обеспечения контроля условий защиты; затем замыкают с помощью программируемого устройства коммутации искусственные цепи передачи тестовой информации между выводами выделенной в фрагмент группы однотипных элементов, образующих параллельную структуру, причем элементы, объединяемые в искусственно созданный фрагмент, могут быть непосредственно не связаны между собой в самом цифровом устройстве, затем одновременно на каждый элемент проверяемого фрагмента подается тест, соответствующий конкретному типу элементов; измеряют ответные реакции на выходах фрагмента и, по результатам сравнения с эталонными значениями, судят об исправности элементов в цифровой схеме. На фиг.1 показано устройство для осуществления способа контроля и диагностирования, на фиг.2 представлена цифровая схема с проверяемыми элементами (объект диагностирования), на фиг.3 и 4 показаны образованные искусственные фрагменты схем из однотипных элементов объекта диагностирования. Устройство для осуществления способа (фиг.1) содержит упраляющую ЭВМ 1, релейное коммутирующее устройство, включающее игольчатое контактное приспособление 2, Kразрядный регистр 3, объект диагностирования цифровая схема 4 (более подробно смотри на фиг.2). Управляющая ЭВМ 1 соединена двунаправленными шинами передачи информации с релейным коммутирующим устройством 2 и с Kразрядным регистром 3 (фиг.1), коммутирующее устройство 2 соединено через игольчатое контактное приспособление с внутренними контрольными точками (КТ) диагностируемой цифровой схемы 4, выходы разрядного регистра соединены с основными входами объекта диагностирования 4 (КТ15-27). Диагностируемая цифровая схема 4 (фиг. 2) содержит элемент счетчик СТ10 5, первый элемент - триггер первый элемент 2И-НЕ 7, второй элемент - триггер третий элемент - триггер четвертый элемент - триггер второй элемент 2И-НЕ 11, элемент 3И 12, третий элемент 2И-НЕ 13, элемент 4И-14. Входы 17, 18, 19, 20, 21, 22 элемента СТ10 5 (фиг.2) соединены с третьим, четвертым, пятым, шестым, седьмым и восьмым выходами Kразрядного регистра 3 соответственно, первый выход элемента СТ10 5 соединен со вторым входом первого элемента второй выход элемента CT10 5 соединен с первым входом четвертого элемента третий выход элемента СТ10 5 соединен со вторым входом второго элемента четвертый выход элемента СТ10 5 соединен со вторым входом третьего элемента 2И-НЕ 13, первый вход первого элемента соединен со вторым выходом Kразрядного регистра 3 (фиг.1), выход первого элемента 2И-НЕ 7 соединен с первым входом второго элемента второй вход третьего элемента соединен с третьим выходом Kразрядного регистра 3, второй вход четвертого элемента соединен с двенадцатым выходом K-разрядного регистра 3 (фиг.1), первый вход второго элемента 2И-HE 11 соединен с девятым выходом регистра 3, а второй вход второго элемента 2И-НЕ 11 соединен с десятым выходом K-разрядного регистра 3, выход второго элемента 2И-HE 11 соединен с третьим входом элемента 4И 14, первый и второй входы элемента 3И 12, а также первый вход третьего элемента 2ИНЕ 13 соединены с тринадцатым выходом регистра 3, третий вход элемента 3И 12 соединен с одиннадцатым выходом регистра 3, выход элемента 3И 12 соединен с четвертым входом элемента 4И 14, выход третьего элемента 2И-НЕ 13 соединен с первым и вторым входом элемента 4И 14. Способ контроля и диагностирования реализуется следующим образом. Сначала цифровая схема 4, как объект исследования, разбивается на тестируемые фрагменты в следующем порядке: 1. Из всех элементов, составляющих структуру цифровой схемы, выделить группы однотипных элементов (например, группу триггеров, группу комбинационных элементов, группу счетчиков и т.д.), для которых рассчитываются векторы специальных тестовых сигналов. Подача таких сигналов на объект устанавливает начальные условия диагностирования каждого из выбранных элементов цифровой схемы. 2. Зафиксировать номера внутренних КТ объекта диагностирования, которые в дальнейшем будут участвовать в параллельном соединении однотипных элементов для образования искусственных фрагментов схем. Выполнить декомпозицию цифровой схемы на тестируемые фрагменты и приступить к ее диагностированию в следующем порядке: 1. В регистр 3 из управляющей ЭВМ 1 записывается вектор сигналов, являющихся начальными условиями диагностирования элементов, которые будут объединены в искусственный фрагмент схемы. 2. По сигналу из управляющей ЭВМ 1 вектор НУД выдается на основные входы объекта. 3. Под упралвением ЭВМ 1 коммутатор 2 создает в диагностируемом устройстве 4 искусственные цепи передачи тестовой информации между выводами элементов, замыкая между собой группы внутренних КТ, зафиксированных на втором шаге процесса тестирования объекта. 4. По команде из управляющей ЭВМ 1 на тестируемый фрагмент схемы подается тест для типа элементов, составляющих его структуру, а с выходов каждого элемента фрагмента снимаются ответные реакции, которые через коммутирующее устройство 2 поступают в ЭВМ 1 для дальнейшего анализа. 5. Ответные реакции сравниваются с эталонными значениями. Выдается диагностическое сообщение о результатах тестирования объекта. Рассмотрим реализацию предлагаемого способа на примере диагностирования цифровой схемы, представленной на фиг.2. Для одновременного тестирования, например, первого элемента 2И-НЕ 7, второго элемента 2И-НЕ 11, третьего элемента 2И-НЕ 13, а также элемента ЗИ 12 необходимо установить на выходе K-разрядного регистра 3 сигналы логической единицы. Затем на выходах элемента СТ10 5 установить состояние логической единицы (при этом необходимо воспользоваться входом подавна него от управляющей ЭВМ 1 сигнал логического нуля). Для параллельного соединения рассматриваемой группы элементов необходимо образовать первую искусственную цепь путем замыкания с помощью коммутирующего устройства 2 первого входа первого элемента 2И-НЕ 7 - Кт15, первого входа второго элемента 2И-НЕ 11 - КТ23, первого входа третьего элемента 2И-НЕ 13 - КТ27, а также первого и второго входов элемента 3И 12 - КТ27. Затем образовать вторую искусственную цепь путем замыкания между собой с помощью коммутирующего устройства 2 второго входа первого элемента 2И-НЕ 7 - КТ18, второго входа второго элемента 2И-НЕ 11 КТ24, третьего входа элемента 3И 12 - КТ25, второго входа третьего элемента 2И-НЕ 13 - КТ31. Результатом такой коммутации является образование временного искусственного фрагмента схемы, показанного на фиг.3. После формирования фрагмента реализуется тест для элементов типа 2И-НЕ и 2И, который подается от управляющей ЭВМ 1. Ответные реакции снимаются на выходах каждого из элементов образованного фрагмента схемы: КТ32, КТ33, КТ34, КТ40. Анализируя структуру цифровой схемы (фиг.2), можно выделить группу триггеров. Для этого, учитывая, что вектор, обеспечивающий условия электрической защиты элементов объекта диагностирования установлен (он совпадает для ранее проверяемых элементов комбинационного типа). необходимо образовать третью искусственную цепь путем замыкания между собой выводов следующих моментов: первого входа первого элемента - КТ16, первого входа второго элемента - КТ40, первого входа третьего элемента - КТ27 и первого входа четвертого элемента - КТ29, затем образовать четвертую искусственную цепь путем замыкания второго входа первого элемента - КТ28, второго входа второго элемента КТ30, второго входа третьего элемента КТ17 и второго входа четвертого элемента КТ26, образованный таким образом фрагмент показан на фиг.4. Тестирование выделенного фрагмента схемы осуществляется как и для элементов комбинационного фрагмента. При этом на входы группы параллельно соединенных триггеров подается соответствующий их типу тест.

ДивитисяДодаткова інформація

Автори англійськоюBaida Mykola Prokopovych, Perevoznikov Serhii Ivanovych, Arapova Olena Mykhailivna

Автори російськоюБайда Николай Прокопович, Перевозников Сергей Иванович, Арапова Елена Михайловна

МПК / Мітки

МПК: G01R 31/28

Мітки: контролю, спосіб, цифрових, схем, діагностування

Код посилання

<a href="https://ua.patents.su/4-14810-sposib-kontrolyu-ta-diagnostuvannya-cifrovikh-skhem.html" target="_blank" rel="follow" title="База патентів України">Спосіб контролю та діагностування цифрових схем</a>

Попередній патент: Спосіб ідентифікації компонентів у друкованих вузлах невідомої структури

Наступний патент: Спосіб підвищення резистентності організму при лікуванні вірусних інфекцій

Випадковий патент: Кавова суміш