Пристрій аналого-цифрового перетворення

Номер патенту: 43254

Опубліковано: 10.08.2009

Автори: Бойко Олександр Володимирович, Захарченко Сергій Михайлович, Азаров Олексій Дмитрович

Формула / Реферат

Пристрій аналого-цифрового перетворення, який містить вхідну аналогову шину та вихідну цифрову шину, схему порівняння, регістр послідовного наближення, цифро-аналоговий перетворювач із ваговою надлишковістю, блок постійної пам'яті, лічильник адреси, причому другий аналоговий вхід схеми порівняння під'єднано до виходу цифро-аналогового перетворювача із ваговою надлишковістю, вихід схеми порівняння з'єднано з інформаційною шиною результату порівняння, яку з'єднано з інформаційними входами регістра послідовного наближення, лічильник адреси з'єднано з першим входом блока постійної пам'яті, який відрізняється тим, що в нього введено шину нульового потенціалу, комутатор, генератор калібрувальних сигналів, генератор імпульсів, блок оперативної пам'яті, цифровий обчислювальний пристрій, блок елементів АБО, шину керуючих сигналів блока керування, причому вхідну аналогову шину з'єднано з першим інформаційним входом комутатора, вихід генератора калібрувальних сигналів з'єднано з другим інформаційним входом комутатора, третій інформаційний вхід комутатора з'єднано з шиною нульового потенціалу, вихід комутатора з'єднано з першим аналоговим входом схеми порівняння, вхід генератора калібрувальних сигналів з'єднано з відповідним виходом шини керуючих сигналів блока керування, вхід генератора імпульсів з'єднано з відповідним виходом шини керуючих сигналів блока керування, а вихід генератора імпульсів з'єднано з входом регістра послідовного наближення і входом лічильника адреси, виходи регістра послідовного наближення з'єднано з відповідними першими входами блока елементів АБО і першими входами цифрового обчислювального пристрою, другий вхід блока постійної пам'яті з'єднано з відповідним виходом шини керуючих сигналів блока керування, вихід блока постійної пам'яті через шину, керовану відповідним виходом шини керуючих сигналів блока керування, з'єднано з другим входом блока елементів АБО, виходи блока елементів АБО з'єднано з відповідними входами цифро-аналогового перетворювача із ваговою надлишковістю, другий вхід цифрового обчислювального пристрою з'єднано з шиною керуючих сигналів блока керування, треті входи цифрового обчислювального пристрою з'єднано з другим блоком постійної пам'яті, четверті входи цифрового обчислювального пристрою об'єднано з блоком оперативної пам'яті, виходи цифрового обчислювального пристрою з'єднано з вихідною цифровою шиною, генератор калібрувальних сигналів містить джерело струму, підсилювач постійного струму, два конденсатори і шість ключових елементів, перший вивід джерела струму з'єднано з шиною нульового потенціалу, другий вивід джерела струму об'єднано з першою клемою ключового елемента, другу клему даного ключового елемента з'єднано з першою клемою першого ключового елемента, першим виводом конденсатора, від'ємним входом підсилювача постійного струму і ключовим елементом, який другим виводом під'єднано до конденсатора і другого ключового елемента, додатний вхід підсилювача постійного струму з'єднано з шиною нульового потенціалу, вихід підсилювача постійного струму, що є виходом генератора калібрувальних сигналів, з'єднано з другою клемою ключового елемента, другим виводом конденсатора, другий конденсатор першим виходом з'єднано з ключовими елементами, перший із яких підключено до вхідної шини, а другий - до шини нульового потенціалу, другий вихід конденсатора з'єднано з ключовими елементами, перший підключено до входу першого конденсатора, а другий - до шини нульового потенціалу.

Текст

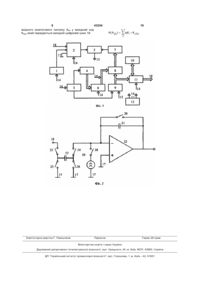

Пристрій аналого-цифрового перетворення, який містить вхідну аналогову шину та вихідну цифрову шину, схему порівняння, регістр послідовного наближення, цифро-аналоговий перетворювач із ваговою надлишковістю, блок постійної пам'яті, лічильник адреси, причому другий аналоговий вхід схеми порівняння під'єднано до виходу цифро-аналогового перетворювача із ваговою надлишковістю, вихід схеми порівняння з'єднано з інформаційною шиною результату порівняння, яку з'єднано з інформаційними входами регістра послідовного наближення, лічильник адреси з'єднано з першим входом блока постійної пам'яті, який відрізняється тим, що в нього введено шину нульового потенціалу, комутатор, генератор калібрувальних сигналів, генератор імпульсів, блок оперативної пам'яті, цифровий обчислювальний пристрій, блок елементів АБО, шину керуючих сигналів блока керування, причому вхідну аналогову шину з'єднано з першим інформаційним входом комутатора, вихід генератора калібрувальних сигналів з'єднано з другим інформаційним входом комутатора, третій інформаційний вхід комутатора з'єднано з шиною нульового потенціалу, вихід комутатора з'єднано з першим аналоговим входом схеми порівняння, вхід генератора калібрувальних сигналів з'єднано з відповідним виходом шини керуючих сигналів блока керування, вхід генератора імпульсів з'єднано з відповідним виходом шини керуючих сигналів блока керування, а вихід генератора імпульсів з'єднано з входом регістра послідовного наближення і входом лічильника адреси, виходи регістра послідовного наближення з'єднано з відповідними пер U 2 (19) 1 3 43254 4 Відомий аналого-цифровий перетворювач вого комутатора, інформаційний вхід якого підклю[А.с. СРСР №1513619, М. кл. Н 03 М 1/26, бюл. № чено до виходів додаткового і основного 37, 1989], який містить вхідну аналогову шину, перетворювача код-струм, n входів останнього блок опорної напруги, перший, другий, третій, четпідключено до відповідних виходів регістра, тактовертий, п'ятий аналогові комутатори, операційний ві входи якого підключено до вісімнадцятого вихопідсилювач, вихідну аналогову шину, резистор, ду блоку керування, перший і другий інформаційні блок вибірки-зберігання, блок порівняння струмів, входи підключено до виходів відповідних розрядів додатковий перетворювач код-струм, основний регістру послідовного наближення, вихід закінченперетворювач код-струм, перший, другий регістр ня перетворення якого підключено до п'ятого вхозсуву, регістр, блок елементів АБО, регістр посліду блоку керування, виходи розрядів з третього до довного наближення, блок керування, обчислюваn-ого підключено до відповідних перших входів льний блок, шину "Запис", вхідну цифрову шину, блоку елементів АБО, виходи якого підключено до вихідну цифрову шину, шину "Режим перетворенвідповідних інформаційних входів регістра з треня", шину "Контроль", шину "Пуск", шину "Кінець тього до n-ого, другі входи підключено до відповідперетворення", причому перший інформаційний них виходів другого регістру зсуву, виходи запису і вхід першого аналогового комутатора є аналогозсуву якого підключено до відповідно до дванадвою вхідною шиною, його керуючий вхід підключецятого і двадцятого виходів блоку керування, шосний до першого виходу блоку керування, перший, тий вхід якого підключено до другого виходу обчидругий і третій виходи якого являються відповідно слювального блоку, двадцять перший і двадцять шинами "Режим перетворення", "Контроль", другий виходи підключено відповідно до сьомого і "Пуск", четвертий вхід підключено до виходу блоку восьмого входів обчислювального блоку, двадцять порівняння струмів, другий і третій входи підклютретій вихід є вихідна шина "Закінчення перетвочено відповідно до тактового і інформаційного рення" і підключений до дев'ятого входу обчислювходів регістру послідовного наближення, виходи з вального, десяті виходи якого є вхідною цифровою четвертого до восьмого підключено до входів обшиною, одинадцятий вхід є шиною "Запис". числювального блоку відповідно від першого до Недоліком цього пристрою є низька параметп'ятого, перші виходи якого являються вихідною рична надійність перетворення. цифровою шиною, шості входи підключено до відНайбільш близьким до пристрою, що заявляповідних дев'ятих виходів блоку керування, десяється, є аналого-цифровий перетворювач [А.с. тий і одинадцятий виходи якого підключено відпоСРСР №1221750, М. кл. Н 03 М 1/26, бюл. № 12, відно до входів запису і зсуву першого регістру 1986], який містить схему порівняння, цифроаназсуву, виходи якого підключено до входів додаткологовий перетворювач із ваговою надлишковістю, вого перетворювача код-струм, перший вихід блорегістр послідовного наближення, вхідну аналогоку опорної напруги підключено до другого інфорву шину, шину "Запуск", блок постійної пам'яті, маційного входу першого аналогового ключа, вихід блок підсумовування, регістр, лічильник адреси, якого підключено до першого інформаційного вховихідну цифрову шину, шину тактових імпульсів, ду другого аналогового комутатора, керуючий вхід причому вхідну аналогову шину під'єднано до якого підключено до дванадцятого виходу блоку першого входу схеми порівняння, другий вхід якої керування, другий і третій інформаційні входи об'під'єднано до виходу цифроаналогового перетвоєднано і підключено до загальної шини, четвертий рювача із ваговою надлишковістю, а вихід схеми інформаційний вхід підключено до другого виходу порівняння - до інформаційного входу регістру блоку опорної напруги, перший і другий виходи послідовного наближення, перший керуючий вхід підключено відповідно до першого інформаційного якого під'єднано до шини "Запуск", другий керуювходу третього аналогового комутатора і до інфочий вхід регістру послідовного наближення з'єднармаційного входу блоку вибірки-зберігання, керуюно з шиною тактових імпульсів, вихід регістру почий вхід якого підключено до тринадцятого виходу слідовного наближення під'єднано до входу блоку керування, вихід підключено до другого інцифроаналогового перетворювача із ваговою формаційному входу третього аналогового комунадлишковістю, перший керуючий вхід лічильника татора, керуючий вхід якого підключено до чотирадреси об'єднано з першим керуючим входом ренадцятого виходу блоку керування, вихід гістру і другим керуючим входом регістру послідопідключено до першого інформаційного входу четвного наближення, другий керуючий вхід лічильнивертого аналогового комутатора, другий інформака адреси об'єднано з другим керуючим входом ційний вхід якого об'єднано з входом операційного регістру і першим керуючим входом регістру попідсилювача і підключено до першого виходу п'яслідовного наближення, вихід лічильника адреси того аналогового комутатора, третій інформаційпід'єднано до адресних входів блоку постійної паний вхід підключено до виходу операційного підм'яті, керуючий вхід блоку постійної пам'яті під'єдсилювача і вихідної аналогової шини, четвертий нано до виходу блоку порівняння, вихід блоку поінформаційний вхід об'єднано з інформаційним стійної пам'яті з'єднано з першим входом блоку входом блоку порівняння струмів і підключено до підсумовування, вихід якого під'єднано до входу другого виходу п'ятого аналогового комутатора, регістру, вихід регістру під'єднано до другого входу перший і другий виходи підключено до відповідних блоку підсумовування і до вихідної цифрової шивиходів резистора, керуючий вхід підключено до ни. п'ятнадцятого виходу блоку керування, шістнадцяНедоліком цього пристрою є низька параметтий вихід якого підключено до керуючого входу рична надійність перетворення, що обмежує габлоку порівняння струмів сімнадцятий вихід підлузь використання корисної моделі. ключено до управляючого входу п'ятого аналого 5 43254 6 В основу корисної моделі поставлено задачу постійного струму і ключовим елементом, який, створення такого пристрою аналого-цифрового другим виводом під'єднано до конденсатора і інперетворення, в якому за рахунок введення нових шого ключового елемента, додатний вхід підсилюблоків і зв'язків між ними досягається підвищення вача постійного струму з'єднано з шиною нульовопараметричної надійності перетворення, що розго потенціалу, вихід підсилювача постійного ширює галузь використання пристрою. струму, що є виходом генератора калібрувальних Поставлена задача досягається тим, що у сигналів, з'єднано з другою клемою ключового пристрій аналого-цифрового перетворення, який елемента, другим виводом конденсатора, другий містить вхідну аналогову шину та вихідну цифрову конденсатор першим виходом з'єднано з ключошину, схему порівняння, регістр послідовного навими елементами, перший із яких підключено до ближення, цифроаналоговий перетворювач із вавхідної шини, а другий - до шини нульового потенговою надлишковістю, блок постійної пам'яті, лічиціалу, другий вихід конденсатора з'єднано з клюльник адреси причому другий аналоговий вхід човими елементами, перший підключено до входу схеми порівняння під'єднано до виходу цифроанапершого конденсатора, а другий - до шини нульологового перетворювача із ваговою надлишковісвого потенціалу. тю, вихід схеми порівняння з'єднано з інформаційНа Фіг.1 представлено структурну схему ананою шиною результату порівняння, яку з'єднано з лого-цифрового перетворювача, що реалізує заінформаційними входами регістру послідовного пропонований спосіб, на Фіг.2 представлено струкнаближення, лічильника адреси з'єднано з входом турну схему генератора калібрувальних сигналів. блоку постійної пам'яті, введено шину нульового Пристрій містить вхідну аналогову шину 18, потенціалу, комутатор, генератор калібрувальних яку з'єднано з першим інформаційним входом косигналів, генератор імпульсів, блок оперативної мутатора 2, вихід генератора калібрувальний сигпам'яті, цифровий обчислювальний пристрій, блок налів 1 з'єднано з другим інформаційним входом елементів АБО, шину керуючих сигналів блоку комутатора 2, третій інформаційний вхід комутатокерування, причому вхідну аналогову шину з'єднара 2 з'єднано з шиною нульового потенціалу 17, но з першим інформаційним входом комутатора, вихід комутатора 2 з'єднано з першим аналоговим вихід генератора калібрувальний сигналів з'єднано входом схеми порівняння 5, вхід генератора калібз другим інформаційним входом комутатора, трерувальних сигналів 1 з'єднано з відповідним вихотій інформаційний вхід комутатора з'єднано з шидом шини керуючих сигналів 14 блоку керування ною нульового потенціалу, вихід комутатора з'єд12, другий аналоговий вхід схеми порівняння 5 нано з першим аналоговим входом схеми під'єднано до виходу цифроаналогового перетвопорівняння, вхід генератора калібрувальних сигрювача із ваговою надлишковістю 7, вихід схеми налів з'єднано з відповідним виходом шини керуюпорівняння 5 з'єднано з інформаційною шиною чих сигналів блоку керування, вхід генератора імрезультату порівняння 15, яку з'єднано з інформапульсів з'єднано з відповідним виходом шини ційними входами регістру послідовного наближенкеруючих сигналів блоку керування, а вихід гененя 9, вхід генератора імпульсів 3 з'єднано з відпоратора імпульсів з'єднано з входом регістру послівідним виходом шини керуючих сигналів 14 блоку довного наближення і входом лічильника адреси, керування 12, а вихід генератора імпульсів 3 з'єдвиходи регістру послідовного наближення з'єднано нано з входом регістру послідовного наближення 9 з відповідними першими входами блоку елементів і входом лічильника адреси 4, вихід лічильника АБО і першими входами цифрового обчислювальадреси 4 з'єднано з першим входом першого блоку ного пристрою, другий вхід блоку пам'яті з'єднано постійної пам'яті 6, другий вхід першого блоку поз відповідним виходом шини керуючих сигналів стійної пам'яті 6 з'єднано з відповідним виходом блоку керування, вихід блоку постійної пам'яті чешини керуючих сигналів 14 блоку керування 12, рез шину, керовану відповідним виходом шини вихід першого блоку постійної пам'яті 6 через шикеруючих сигналів блоку керування, з'єднано з ну керовану відповідним виходом шини керуючих другим входом блоку елементів АБО, виходи блосигналів 14 блоку керування 12 з'єднано з другим ку елементів АБО з'єднано з відповідними входами входом блоку елементів АБО 8, виходи регістру цифроаналогового перетворювача із ваговою послідовного наближення 9 з'єднано з відповіднинадлишковістю, другий вхід цифрового обчислюми першими входами блоку елементів АБО 8 і вального пристрою з'єднано з шиною керуючих першими входами цифрового обчислювального сигналів блоку керування, треті входи цифрового пристрою 11, виходи блоку елементів АБО 8 з'єдобчислювального пристрою з'єднано з другим нано з відповідними входами цифроаналогового блоком постійної пам'яті, четверті входи цифровоперетворювача із ваговою надлишковістю 7, друго обчислювального пристрою об'єднано з блоком гий вхід цифрового обчислювального пристрою 11 оперативної пам'яті, виходи цифрового обчислюз'єднано з шиною керуючих сигналів 14 блоку кевального пристрою з'єднано з вихідною цифровою рування 12, треті входи цифрового обчислювальшиною, причому генератор калібрувальних сигнаного пристрою 11 з'єднано з другим блоком полів містить джерело струму, підсилювач постійного стійної пам'яті 13, четверті входи цифрового струму, конденсатори і ключові елементи, перший обчислювального пристрою об'єднано з блоком вивід джерела струму з'єднано з шиною нульового оперативної пам'яті 10, виходи цифрового обчиспотенціалу, другий вивід джерела струму об'єдналювального пристрою 11 з'єднано з вихідною цино з першою клемою ключового елемента, другу фровою шиною 16. клему даного ключового елемента з'єднано з перГенератор калібрувальних сигналів 1 містить шою клемою ключового елемента, першим виводжерело струму 19, перший вивід якого з'єднано з дом конденсатора, від'ємним входом підсилювача шиною нульового потенціалу 17, другий вивід 7 43254 8 джерела струму 19 об'єднано з першою клемою визначення ваги розряду що калібрується по коключового елемента 28. Друга клема ключового манді блоку керування 12 ключ 28 розмикається і елемента 28 з'єднана з першою клемою ключового замикаються ключові елементи 23 і 26, конденсаелемента 20, першою клемою ключового елементор 27 заряджається. На наступному етапі ключові та 24, першим виводом конденсатора 21, від'ємелементи 23 і 26 розмикаються, а 24 і 25 замиканим входом підсилювача постійного струму 22. ються, заряд з конденсатора 27 перетікає у конДодатний вхід підсилювача постійного струму 22 денсатор 21, формуючи нове значення допоміжноз'єднано з шиною нульового потенціалу 17, вихід го сигналу. Причому ємність конденсатора 27 підсилювача постійного струму 22, що є виходом набагато менша за ємність конденсатора 21. У генератора калібрувальних сигналів 1, з'єднано з міру формування вказаного коду і появі значущих другою клемою ключового елемента 20, другим розрядів із блоку постійної пам'яті 6 беруться коди виводом конденсатора 21. Другу клему ключового цифрових еквівалентів ваг значущих розрядів і елемента 24 з'єднано з першим виводом конденпослідовно подаються у цифровий обчислювальсатора 27 і першою клемою ключового елемента ний пристрій 11, де розраховується: n-m-1 26. Другу клему ключового елемента 26 з'єднано з K'n =m( `A `&0 ) = å a¢Ki( `A `&0 ). шиною нульового потенціалу 17. Другий вивід конi && && a i&-`0 a i&-`0 0 денсатора 27 з'єднано з першою клемою ключовоДалі примусово вимикається (n-m)-ий розряд і го елемента 25 і першою клемою ключового елемента 23, другу клему ключового елемента 25 проводиться компенсація A 0n -m , процесі чого у ¶ з'єднано з шиною нульового потенціалу 17. Другу цифровому обчислювальному пристрої 11 отримуклему ключового елемента 23 з'єднано з вхідною ¢¢ ється Kn-m : шиною 18. Пристрій працює у режимі самокалібрування і n -m-1 ² K¢¢ -m( `A `&0 ) = å ai K (`A `&0 ) . основного перетворення. Перед початком самокаn && && a i&- `0 a i&- `0 0 лібрування по команді блоку керування 12 комутаПісля цього знаходиться вага (n-m)-го розряду тор 2 підключає вихід генератора калібрувальних сигналів 1 до першого входу схеми порівняння 5, а у вигляді: для допоміжного сигналу A 0 && an - m регістр послідовного наближення 9 встановлюється у нульовий стан керуючим сигналом 14 блоку K 0n-m( `Aa&`&0- 0 ) = K 0¢¢n -m( `Aa&`&0- 0 ) - K 0¢n-m( `Aa&`&0- 0 ) & i& ` & i& ` & i& ` керування 12. Процес самокалібрування здійснюОтриманий код фіксується у блоці оперативної ється послідовно від молодших розрядів до старпам'яті 10 у (n-m)-y комірку пам'яті. Далі допоміжших, причому першим калібрується (n-m)-ий розний сигнал змінюється з A 0n -m на A1 n-m і процеряд. У цьому випадку за допомогою лічильника ¶ ¶ адреси 4, який отримує імпульси від генератора дура повністю повторюється. Вага розряду отриімпульсів 3, і першого блоку постійної пам'яті 6 мана за допомогою допоміжного сигналу A1 n-m за ¶ через блок елементів АБО 8 на цифровий вхід цифроаналогового перетворювача із ваговою допомогою цифрового обчислювального пристрою надлишковістю 7 подається кодова комбінація, яка 11 додається до коду, який міститься у блоці опезабезпечує вмикання (п-т)-ого розряду і деяких ративної пам'яті 10 у (n-m)-y комірку пам'яті. В реінших молодших розрядів таким чином, щоб викозультаті вага розряду буде знайдена шляхом осенувалось співвідношення на виході цифроанареднення за формулою: логового перетворювача із ваговою надлишковіS -1 стю 7: å K n-m(`Aa&&i&i&-`0 ) 0 K n - m = i= 0 . && A a n-m ³ Qn -m = DQn -m, S DQn -m = dQ × Qn-m . Після цього розпочинається процес калібрування (п-т+1)-го розряду і вона продовжується аж По команді блоку керування 12 на виході генедо калібрування старшого (n-1)-го розряду. Після ратора калібрувальних сигналів 1 починає формуцього аналого-цифровий перетворювач переховатись аналоговий сигнал Аклб, який лінійно зросдить у режим калібрування зсуву нуля. Комутатор тає аж доти, поки сигнали на вході схеми 2 підключає перший вхід схеми порівняння 5 до порівняння 5 не зрівняються. При цьому схема шини нульового потенціалу 17. По команді блоку порівняння 5 спрацьовує. Генератор калібрувалькерування 12 здійснюється процес порозрядного них сигналів 1 являє собою інтегратор на базі опеврівноваження вхідного сигналу. У міру формураційного підсилювача 22, а також містить джеревання значущих розрядів у цифровому обчислюло струму 19. Для цього по команді блоку вальному пристрої 11 обчислюється код зміщення керування 12 замикає ключовий елемент 20 і нуля і фіксується у блоці оперативної пам'яті 10. струм зміщення заряджає конденсатор 21. Коли На цьому процес калібрування закінчується і приключовий елемент 20 розмикається, заряд на констрій переходить у режим основного перетворенденсаторі 21 фіксується і на виході генератора ня. встановлюється постійний рівень напруги. Після У режимі основного перетворення комутатор 2 розмикання ключового елемента 20 інтегратора підключає перший вхід схеми порівняння 5 до вхіблок керування 12 блокує подачу коду з виходу дної аналогової шини 18, а також у цифровий обблоку постійної пам'яті 6 і розпочинає процес почислювальний пристрій 11 подається код зміщенрозрядного врівноваження, в результаті якого у ня нуля. Далі розпочинається перетворення регістрі послідовного наближення 9 формується код N’n-m , який надходить із входу 15. Для точного 9 43254 вхідного аналогового сигналу Авх у вихідний код Kвих який передається вихідній цифровій шині 16: Комп’ютерна верстка Г. Паяльніков 10 K( A a o ) = ˆ~ n -1 ~ å aiK i + K cn 0. Підписне 0 Тираж 28 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюAnalog-to-digital conversion device

Автори англійськоюAzarov Oleksii Dmytrovych, Zakharchenko Serhii Mykhailovych, Boiko Oleksandr Volodymyrovych

Назва патенту російськоюУстройство аналого-цифрового преобразования

Автори російськоюАзаров Алексей Дмитриевич, Захарченко Сергей Михайлович, Бойко Александр Владимирович

МПК / Мітки

МПК: H03M 1/22

Мітки: перетворення, пристрій, аналого-цифрового

Код посилання

<a href="https://ua.patents.su/5-43254-pristrijj-analogo-cifrovogo-peretvorennya.html" target="_blank" rel="follow" title="База патентів України">Пристрій аналого-цифрового перетворення</a>

Попередній патент: Біогазова установка

Наступний патент: Спосіб поверхневого зміцнення ріжучих пластин з твердих сплавів

Випадковий патент: Операційний аноскоп