Схема пам’яті

Номер патенту: 29581

Опубліковано: 25.01.2008

Автори: Мараховський Леонід Федорович, Міхно Наталія Леонідовна

Формула / Реферат

Схема пам'яті (СП) з керуючими входами, за допомогою яких забезпечується можливість переключення їх в будь-який стійкий стан, що складається із n логічних елементів І-НІ та/або АБО-НІ, яка відрізняється тим, що будується на j(j ³ 2) схемах пам'яті (СПj), кожна з яких складається із nj (nj ³ 3) логічних K-входових елементів І-НІ та/або АБО-НІ з навантажувальною здатністю Р1, розбитих на ![]() груп, де

груп, де  кількість запам'ятовуючих станів пристрою пам'яті), по qj,k елементів І-НІ та/або АБО-НІ, де

кількість запам'ятовуючих станів пристрою пам'яті), по qj,k елементів І-НІ та/або АБО-НІ, де

причому виходи елементів І-НІ та/або АБО-НІ k-тої групи (qk > 1) СПj через додатково введені Г-входові елементи І та/або АБО з навантажувальною здатністю Р2 або безпосередні виходи елементів І-НІ та/або АБО-НІ k-тої групи (qk = 1) з'єднані з одним із входів елементів І-НІ та/або АБО-НІ інших груп даного СПj, СПj розташовані по j рівнях, причому верхній рівень CПj містить nj елементів СПj, розбитих не менш ніж на дві групи mj (j ³ 2) по qj,k елементів ![]() ; один вхід кожного елемента І-НІ та/або АБО-НІ k-тої групи (qj,k > 1) БФСПj j-го рівня з'єднаний з одним інформаційним входом j-тої групи схеми пам'яті ШZj, a виходи елементів І-HІ та/або АБО-НІ СПj з'єднані відповідно з інформаційними виходами j-тої групи схеми пам'яті ШАj, входи елементів І-НІ та/або АБО-НІ k-тої групи (qj,k > 1) СПj j-го рівня з'єднані з груповими виходами елементів І та/або АБО k-тих груп (qs,k > 1)

; один вхід кожного елемента І-НІ та/або АБО-НІ k-тої групи (qj,k > 1) БФСПj j-го рівня з'єднаний з одним інформаційним входом j-тої групи схеми пам'яті ШZj, a виходи елементів І-HІ та/або АБО-НІ СПj з'єднані відповідно з інформаційними виходами j-тої групи схеми пам'яті ШАj, входи елементів І-НІ та/або АБО-НІ k-тої групи (qj,k > 1) СПj j-го рівня з'єднані з груповими виходами елементів І та/або АБО k-тих груп (qs,k > 1) ![]() та з виходами елементів І та/або АБО k-тої групи (qs,k = 1) СПs через додатково введені С-входові елементи АБО та/або I з навантажувальною здатністю Р3 блока Ij-1 міжступеневих зв'язків, які реалізують дешифрування групових вихідних сигналів СПs та виходи яких з'єднані у відповідності з одиницями (нулями) двійкового коду k-тих груп (qj,k > 1) із входами елементів І-НI та/або АБО-НI цих k-тих груп СПj, причому вихід кожного елемента АБО та/або І блока Ij-1 не з'єднаний хоча б з одним елементом І-НI та/або АБО-НІ кожної k-тої групи СПj; кількість ip елементів АБО та/або І в схемі блока

та з виходами елементів І та/або АБО k-тої групи (qs,k = 1) СПs через додатково введені С-входові елементи АБО та/або I з навантажувальною здатністю Р3 блока Ij-1 міжступеневих зв'язків, які реалізують дешифрування групових вихідних сигналів СПs та виходи яких з'єднані у відповідності з одиницями (нулями) двійкового коду k-тих груп (qj,k > 1) із входами елементів І-НI та/або АБО-НI цих k-тих груп СПj, причому вихід кожного елемента АБО та/або І блока Ij-1 не з'єднаний хоча б з одним елементом І-НI та/або АБО-НІ кожної k-тої групи СПj; кількість ip елементів АБО та/або І в схемі блока ![]() визначається із відношення за формулою:

визначається із відношення за формулою: ![]() ,

,

де qp,k >1, та один вхід кожного елемента АБО та/або I всіх блоків Ір з'єднаний з керуючим входом z0 всього пристрою; загальна кількість М запам'ятовуючих станів пристрою обчислюється за формулою: ![]() , загальна кількість зовнішніх зв'язків визначається співвідношенням: Sзн.з<2n, загальна кількість внутрішніх зв'язків між елементами визначається співвідношенням: Sвн.з < n´(n-1), при цьому обмеження параметрів елементів, що використовуються, по кількості допустимих навантажень повинні задовольняти наступним умовам (при максимальному значені mj та qj,k:

, загальна кількість зовнішніх зв'язків визначається співвідношенням: Sзн.з<2n, загальна кількість внутрішніх зв'язків між елементами визначається співвідношенням: Sвн.з < n´(n-1), при цьому обмеження параметрів елементів, що використовуються, по кількості допустимих навантажень повинні задовольняти наступним умовам (при максимальному значені mj та qj,k:

Текст

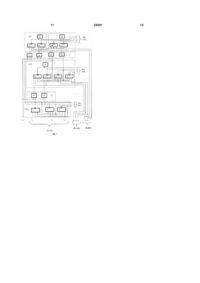

Схема пам'яті (СП) з керуючими входами, за допомогою яких забезпечується можливість переключення їх в будь-який стійкий стан, що складається із n логічних елементів І-НІ та/або АБО-НІ, яка відрізняється тим, що будується на j(j ³ 2) схемах пам'яті (СПj), кожна з яких складається із nj (nj ³ 3) логічних K-входових елементів І-НІ та/або АБО-НІ з навантажувальною 3 29581 4 K ³ m j - 1 + 2qj, k -1; T ³ q j, k ; C ³ j; P³ 1 m j- 1 å (2 i =2 P2 ³ qp , k -1 m j- 1 j -1 i =1 - 1) + m j ; i =1 å q j,k + å (2 qp,k -1 - 1); P3 ³ 2 qp, k -1 - 1. Корисна модель відноситься до області автоматики, обчислювальної техніки та призначений для реалізації функції запам'ятовування декілька станів на основі двійкових базових елементів "І-НІ" та/або "АБОНІ". Відомі одноступеневі схеми пам'яті із логічних елементів "І-НІ" та/або "АБО-НІ", де ви хід i-го елемента "І-НІ" та/або "АБО-НІ", з'єднаний зі входами двох і більш логічних елементів схеми, закономірність зв'язків між якими визначається за формулою: (N - 1)! Z = Cs -1 = N S! (N - 1- S)! , де S≥2, N≥3 [И.Н. Букреев и др. Микроэлектронные схемы цифровых устройств Изд. 2-е перераб. и доп. - М.: "Сов. радио", 1975. - стр.209-211, рис.5.47]. Недоліком цих схем пам'яті є те, що багато варіантів з'єднання ведуть до створення непрацездатних схем, а працездатні схеми змінюють свої стани тільки при появі установчих вхідних сигналів на всій множині вхідних вузлів та кількість станів, що можна запам'ятовувати, не перевищує кількість використовуваних логічних елементів, а, крім того, недоліком ще є те, що вони не в змозі змінювати структуру запам'ятання станів цих схем пам'яті. Відомі одноступеневі однофазні схеми пам'яті із Дилогічних елементів "І-НІ" та/або "АБО-НІ" з кількістю внутрішніх входів K=N-1, де вихід кожного I-го елемента "І-НІ" та/або "АБО-НІ", з'єднаний зі входом інших (N-1) логічних елементів схеми. [И.Н. Букреев и др. Микроэлектронные схемы цифровых устройств Изд. 2-е перераб. и доп. - М.: "Сов. радио", 1975. - стр.208-210, рис.5.46]. Недоліком цих схем пам'яті є те, що вони змінюють свої стани тільки при появі установчих вхідних сигналів на всій множині вхідних вузлів та кількість станів, що можна запам'ятовувати, не перевищує кількість використовуваних логічних елементів. Кількість К входів елементів цих схем та кількість Р допустимих навантажень елементів повинно дорівнювати кількості N використовуваних елементів для побудови цих схем пам'яті (СП), а, крім того, недоліком ще є те, що вони не в змозі змінювати структуру запам'ятання станів цих схем пам'яті. Одноступеневі схеми пам'яті є базовими схемами пам'яті, запам'ятовуючих всю множину своїх станів при одному вхідному сигналі. Окремим випадком одноступеневих однофазних схем пам'яті є одноступеневий тригер RS-типу [И.Н. Букреев и др. Микроэлектронные схемы цифровых устройств Изд. 2-е перераб. и доп. - М.: "Сов. радио", 1975. - стр.55-61, рис.2.3]. Одноступеневий тригер RS-типу є базовою схемою пам'яті для побудови інших типів тригерів. Недоліком тригера RS-типу є те, що він змінює свої стани тільки при появі установчих вхідних сигналів на всій множині вхідних вузлів, а, крім того, недоліком ще є те, що він не в змозі змінювати структуру запам'ятання своїх станів. Відома схема пам'яті, що складається із n елементів "І-НІ" та/або "АБО-НІ", один з входів якого з'єднаний зі вхідною шиною установки схеми пам'яті в один із станів, елементи "І-НІ" та/або "АБО-НІ", розбиті на m (m1) СПs (s = 1 j - 1) таз виходами елементів "І" та/або "АБО" А-тої групи (qs,k=1) СП s 6 через додатково введені С-входові елементи "АБО" та/або "І" з навантажувальною здібністю Р3 блока Ij-1 між ступеневих зв'язків, які реалізують дешифр ування групових ви хідних сигналів СП j та виходи яких з'єднані у відповідності з одиницями (нулями) двійкового коду k-тих гр уп (qj,k>1) зі входами елементів "І-Н" та/або "АБО-НI" ци х k-тих груп СП j, причому вихід кожного елемента "АБO" та/або "І" блока Ij-1 не з'єднаний хоча би з одним елементом "І-НІ" та/або "АБО-НІ" кожної k-тої групи СП j кількість Ij-1 елементів "АБО" та/або "І-НІ" I (p= 1, j - 1) в схемі блока p відношення за формулою: mk визначається із m k q å qp,k £ rp £ Õ æ 2 p,k - 1ö - 1 ç ÷ ø i=1 i=1è де qp,k>1, та один вхід кожного елемента "АБО" та/або "І" всі х блоків Ір з'єднаний з управляючим входом Z0 всього пристрою; загальна кількість М запам'ятовуючи х станів схеми пам'яті обчислюється за формулою: J M = Õ mi i=1 при цьому обмеження параметрів елементів, що використовуються, по кількості допустимих навантажень повинні задовольняти наступним умовам (при максимальному значені m j та qj,k): K ³ m j - 1+ 2 T ³ qj,k; C ³ j; mj-1 P1 ³ å (2 i= 2 qj ,k -1 qj ,k -1 ; - 1) + m j; m j-1 j-1 i=1 i =1 q j, k -1 P2 ³ å qj,k + å (2 qj ,k -1 - 1); P3 ³ 2 -1 ; На Фіг.1 приведена функціональна схема пам'яті. Вона складається із трьох СП j (СП 1, СП 2 СП 3, де j=3) та двох схем блоків Iр (I1, I2, де p=2). Схеми пам'яті СП 1-СП 3, що побудовані на одинадцяті елементах "АБО-НI" 1-11 та на трьох елементах "АБО" 12-14. В СП 1 вихід елемента 1 з'єднаний зі входами елементів 2, 3, вихід елемента 2 з'єднаний зі входами елементів 1, 3, вихід елемента 3 з'єднаний зі входами елементів 1, 2, входи елементів 1. 2, 3 з'єднані відповідно з інформаційними входами z1, z2 z3 шини Bx.ШZ1 . В СП 3 виходи елементів 4, 5 через елемент 12 з'єднані зі входами елементів 6, 7, вихід елемента 6 з'єднаний зі входами елементів 4, 5, 7, вихід елемента 7 з'єднаний зі входами елементів 4, 5, 6, входи елементів 4, 5 з'єднані між собою та з інформаційним входом 24 шини Bx.ШZ 2 входи елементів, 6, 7 з'єднані відповідно з інформаційними входами 25, 66 шини Вх.ШZ2. В СП 3 виходи елементів 8 та 9 через елемент 13 з'єднані зі входами елементів 10, 11, виходи елементів 10 та 11 через елемент 14 з'єднані зі входами елементів 8, 9, вхід інформаційний z7 шини Bx.ШZ3 з'єднаний зі входами елементів 8, 9, вхід інформаційний z8 шини Вх.ШZ 3 з'єднаний зі входами елементів 10, 11, входи елементів 1-11 з'єднані відповідно з інформаційними виходами а 1 7 29581 8 а11 шини Вих.ША1-Вих.ША3. С хеми блоків 11, 12 побудовані із елементів "І" 15-20; один із входів елементів 15-20 з'єднаний з управляючим входом z0 , ви хід елемента 1 з'єднаний зі входами елементів 15, 17, вихід елемента 2 з'єднаний зі входами елементів 16, 18, вихід елемента 12 з'єднаний зі входом елемента 19, вихід елемента 6 з'єднаний зі входом елемента 20, виходи елементів 15, 16 з'єднані відповідно зі входами елементів 4, 5, виходи елементів 17-20 з'єднані відповідно зі входами елементів 8-11. Відміною структурною особливістю схеми пам'яті, що заявляється, є багатоступенева пам'ять, де кожний структурний j-й рівень складається з стійкової схеми пам'яті СП j (j=1, 2, 3), причому в СПj з’єднані тільки входи тих елементів, які належать k-ої групі (qj,k>1), з xj (табл.4). Установчі набори k вхідних сигналів при функціональному режимі роботи пристрою (z0=1) представлені в табл.2. Багатофункціональний режим розглядає роботу СП j (j≥2) верхніх рівнів в різних підмножинах станів, що запам'ятовуються при відповідних станах СП s ніжних рівнів. В цьому режимі СП j функціонують в різних підмножинах своїх станів у відповідності зі станами СП s, здібні змінювати відображення інформації вхідної у вихідну (табл.3). Переходи в СП j, із одного стана в інший одної підмножини здійснюється під впливом , виходами тригерів ніжних рівнів СПs (s = 1 j - 1) через схеми блоків Ір (I1, І2) між ступеневих зв'язків, причому схеми блоків Ір комутуються управляючим входом z0, який може бути виконаний у вигляді роздільної шини ШZ0 по кожному структурному рівню. Відміною функціональною особливістю пристрою, що заявляється, є робота СПj верхніх рівнів в декількох різних підмножинах своїх станів, що визначають сукупністю станів тригерів xj СП j пристрою при подані установчих наборів k вхідних сигналів тільки на вхідних вузлах СП s ніжних рівнів. В цьому режимі переходи в CП s ніжних рівнях із одного стану в інший стан СПs (s 1 j - 1) = , ніжних рівнів, що дозволяє змінювати відображення вхідної та вихідної інформації в СП j та стани схеми пам'яті меншою кількістю вхідних сигналів, які поступають тільки на частину вхідни х вузлів схеми пам'я ті. У даному випадку, функціональна схема пам'яті запам'ятовує 18 станів і має 9 вхідних і 11 вихідних вузлів, що у сумі складають 20 зовнішніх, вузлів, що менше чим у прототипу на 16 вузлів. Закон функціонування багатоступеневого пристрою пам'яті здійснюється у дво х режимах: регістровому (при z0=0) та функціональному (при z0=1). Регістровий режим (табл.1) розглядає роботу СП j як окремих розрадів паралельного регістра. Робота СП j в цьому режимі задається xj наборів k вхідних сигналів у час такту ti (див. діаграму сигналів). Укрупнений режим розглядає зміну станів усіх xj здійснюється під впливом наборів k вхідних сигналів у час такту ti а переходи в СП j верхніх рівнів із одного стану в інший здійснюються під впливом внутрішніх наборів вхідних сигналів, що поступають з виходів СП s ніжних рівнів через блоки Ір міжступеневих зв'язків, у час такту а( неперервного автоматного часу Ті (див. діаграму сигналів). Укрупнені переходи в СП j верхніх рівнів здійснюються в пристрої у такт Di, коли на їх вхідні вузли zi поступають набори ej вхідних сигналів. Таким чином, запропонована корисна модель уявляє собою схему пам'яті, функціонування в регістровому режимі як самостійні схеми пам'яті в паралельному регістрі та у функціональному режимі як єдина багатоступенева схема пам'яті, яка має здібність змінювати відображення інформації в СПj верхніх рівнів без впливу установчих вхідних сигналів за рахунок внутрішніх міжступеневих зв'язків та змінювати стан всієї схеми пам'я ті меншою кількістю вхідних сигналів, що в прототипі здійснювати принципово неможливо. xj (z ) установочними наборами k i вхідних сигналів, що поступають у такт ti та установлюють стани Установчі набори вхідних сигналів - при регістровому режим j Ak (ai ) , які зберігають ці стани під впливом наборів ej вхідних сигналів, що поступають у такт Di (см. діаграму сигналів) та мають значення на всіх 1 вхідних вузлах zj рівні 0, тобто, zj=0. Стани A0 , A2 , A3 (табл. 1) не зберігаються, а тому в 0 0 детермінованому режимі не розглядаються. Схеми пам'яті СП j в регістровому детермінованому режимі однозначно працюють при появі СП Набори вхідних сигналів Значення вхідних вузлів СП j j xk zi СП 1 x1 k z1 z2 z3 x1 0 111 x1 1 011 x1 2 101 x1 3 110 x2 k z4 z5 z6 x2 0 111 j xk послідовної пари вхідних сигналів та ej, тобто, e1 (z1=z2=z3=0), e 2 (z4=z5=z6=0), e 3 (z7=z8=0). Функціональний режим розглядає роботу схеми пам’яті у двох режимах: багатофункціональному (табл.3) та укрупненому СП 2 Зн 9 29581 10 011 2 x1 , 1 x3 1 0 0 1 В6 В6 B6 1 6 В6 В6 В6 В12 В12 B B A2 101 2 x1 , 0 x3 0 1 0 2 AВ В5 B5 В5 2 5 B5 В5 В11 В11 В11 В 2 x2 3 110 x2 2 0 x3 0 0 1 1 AВ В4 В4 В4 3 4 В4 В4 B10 B10 B10 B x3 k z8 z9 , 8 x2 ax3a9 а10 a11 2, 2 0000 x2 x3 3, 1 1100 x2 x3 3, 2 0011 2 x1 x2 2 СП 3 , x3 0 11 x3 1 01 x3 2 10 2 3 AВ В3 В3 В3 k 3 В3 В3 В9 В9 В9 A3 0 В2 В2 В2 В2 3 A1 В2 В2 B8 B8 B8 В1 В1 В1 В1 В1 В1 B1 A3 2 В7 В7 Таблиця 2 Переходи при укрупненому режимі роботи схе Установчі набори вхідних сигналів при функціональному режимі роботи схеми пам'яті (z0=1) Об'єднані стан Набори вхідних Об'єднані Набори вхідних сигналів Значення вихідних вузлів СП j Набори станів СП j сигналів стани схеми пам'яті В5 В6 В7 B8 В9 В1 В2 В3 В4 j x1 x2 x3 a1 а2 а3 a4 a5 а6 а 7 a8 a9 a10 a11 Ak ВВi B14 В15 В16 В17 B18 В13 В14 В15 k, k, k 13 x1 1 x1 3 , x2 3 , x3 1 001 0001 11 00 3 A1 A2 A1 x1 3, 3, 2 1 2 3 x1 A3 A3 A2 3 , , 1 2 1 2 x3 x1 1 A3 A2 A1 , , , x1 2 1 A1 A2 A3 , x2 3, 2, 2 1 2 2 x3 1 A1 A1 A1 , x3 3, , 2 2 x1 2 A1 A1 A3 , x1 3, , 2 2 3 x1 A1 A2 A1 , x2 2, 3, 2 2 x1 A1 A2 A3 , x3 2, 3, 2 2 1 2 x3 3 A1 A2 A1 , x1 2, 2, 2 x1 3 A1 A2 A3 , x2 2, 2, 2 x1 3 , x2 3 , x3 2 001 0001 00 11 x1 3 , x2 2 , x3 1 001 0010 11 00 x1 3 , x2 2 , x3 2 001 0010 00 10 x1 3 , 2 x1 , x3 1 001 1100 11 00 x1 3 , 2 x1 , x3 2 001 1100 00 01 x1 2 , x2 3 , x3 1 010 0001 10 00 x1 2 , x2 3 , x3 2 010 0001 00 11 x1 2 , x2 2 , x3 1 010 0010 10 00 x1 2 , x2 2 , x3 2 010 0010 00 10 x1 2 , 2 x1 , x3 1 010 1000 10 00 1 2 2 x3 3 A1 A1 A1 , x3 2, , В1 В2 В1 В2 В1 В2 В1 В2 В1 В11 x1 2 , 2 x1 , x3 2 010 1000 00 01 2 A1 A1 A3 2, , 2 В12 x1 x2 x3 1, 3 , 1 100 0001 01 00 3 A1 A2 A1 1, 3 , В13 x1 x2 x3 1, 3 , 2 100 0001 00 11 A1 A2 A3 1, 3 , 2 В14 x1 x2 x3 1, 2 , 1 100 0010 01 00 3 A1 A2 A1 1, 2 , B15 x1 x2 x3 1, 2 , 2 100 0010 00 10 A1 A2 A3 1, 2 , 2 В16 2 x1 x1 x3 1, , 1 100 0100 01 00 2 3 A1 A1 A1 1, , В17 2 x1 x1 x3 1, , 2 100 0100 00 01 2 A1 A1 A3 1, , 2 B18 В71 B8 В9 B10 B11 B12 В7 B8 В9 В В12 В2 В3 В4 В5 В6 В1 В2 В3 В ВВ3 В18 В17 B18 В17 B18 В17 B18 B17 17 ВВ4 В16 В15 В16 В15 В16 В15 В16 В15 15 ВВ5 В14 В13 В14 В13 В14 В13 В14 В13 13 BВ6 B12 B11 B12 B11 B12 B11 B12 B11 11 В97 B10 В9 B10 В9 B10 В9 B10 В9 В В78 B8 В7 B8 В7 B8 В7 B8 В7 B В59 B6 В5 B6 В5 B6 В5 B6 В5 В В3 В4 В3 В4 В3 В4 В3 В4 В3 В10 Таблиця 3 Переходи при багатофункціональному режимі роботи схеми пам'яті (z0=1) x3 1 Об'єднані стани схеми пам'яті В1 В2 В3 В4 В5 В6 В7 B8 В9 B10 В11 В12 В13 В14 В15 В16 В17 B18 В2 В2 В4 В4 В6 В6 В8 B8 B10 B10 B12 B12 В14 В14 В16 В16 B18 В18 x3 2 В1 В1 В3 В3 В5 В5 B7 Набори вхідних сигналів В7 В7 В7 В11 В11 В13 В13 В15 В15 B17 B17 11 29581 12

ДивитисяДодаткова інформація

Назва патенту англійськоюMemory circuit

Автори англійськоюMarakhovskyi Leonid Fedorovych, Mikhno Natalia Leonidivna

Назва патенту російськоюСхема памяти

Автори російськоюМараховский Леонид Федорович, Михно Наталья Леонидовна

МПК / Мітки

МПК: G05B 11/42

Код посилання

<a href="https://ua.patents.su/6-29581-skhema-pamyati.html" target="_blank" rel="follow" title="База патентів України">Схема пам’яті</a>

Попередній патент: П’єзоелектричний перетворювач енергії потоку

Наступний патент: Схема пам’яті