Пристрій для додавання послідовності добутків пар чисел із плаваючою точкою

Номер патенту: 58920

Опубліковано: 15.08.2003

Автори: Блінова Тетяна Олександрівна, Порєв Віктор Миколайович, Долголенко Олександр Миколайович, Луцький Георгій Михайлович

Формула / Реферат

Пристрій для додавання послідовності добутків пар чисел із плаваючою точкою, що містить тактовий вхід пристрою, блок керування, який містить тригер керування, регістри мантиси та порядку, перший вузол пам'яті, причому тактові входи регістра мантиси й регістра порядку з'єднані з тактовим входом пристрою, блок підсумовування, який містить регістр мантиси, тригер переносу, комутатор, суматор мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра мантиси та тригера переносу, та блок формування результату, який містить вхід обнуління, регістр, комутатор результату, суматор результату, першу групу із m(n-1) - входових елементів АБО, де n - розрядність мантиси, m = [Pмакс/n-1]+1,а Pмакс - максимальний порядок доданків, другий вузол пам'яті, тригер знака, регістр порядку, тригер перестановок, регістр результату, другу групу з (n-1)[0,5m] - входових елементів АБО, третю групу з (n-1)(m-[0,5m]) - входових елементів АБО, третій вузол пам'яті, суматор порядків, вихід знака, вихід порядку, n - розрядний вихід мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра, тригера знака, регістра порядку, тригера перестановок та регістра результату, а вхід обнуління зв'язаний з керуючим входом встановлення в нуль регістра, вихід якого зв'язаний із другою групою входів суматора мантиси блока підсумовування, вихід котрого приєднаний до входу регістра, вихід старшого розряду якого з'єднаний з інформаційним входом тригера знака, з входом переносу суматора результату та з керуючим входом комутатора результату, перший та другий інформаційні входи якого з'єднані відповідно з прямим та інверсним виходами m(n-1) молодших розрядів регістра, а вихід комутатора результату приєднаний до першої групи входів суматора результату, на другу групу входів якого подається сигнал "Логічний нуль", вихід суматора результату приєднаний до входів регістра результату, а також до відповідних входів першої групи (n-1) - входових елементів АБО, виходи яких з'єднані з m- розрядним адресним входом другого вузла пам'яті, перший, другий і m - розрядний третій виходи якого з'єднані відповідно з інформаційним входом регістра порядку, інформаційним входом тригера перестановок і з керуючими входами встановлення в нуль кожної із m(n-1) - розрядних груп регістра результату, виходи усіх непарних (n-1) - розрядних груп виходів якого з'єднані зі входами другої групи із (n-1)[0,5m] - входових елементів АБО таким чином, що виходи усіх k-x розрядів цих груп приєднані до входів k-ого елемента АБО, і аналогічно, виходи усіх парних (n-1) - розрядних груп виходів регістра результату з'єднані зі входами третьої групи із (n-1)(m-[0,5m]) - входових елементів АБО таким чином, що виходи усіх k-x розрядів цих груп приєднані до входів k-ого елемента АБО, виходи другої групи елементів АБО та виходи третьої групи елементів АБО з'єднані відповідно з другим та третім адресними входами третього вузла пам'яті, перший адресний вхід якого приєднаний до виходу тригера перестановок, а перший вихід третього вузла пам'яті з'єднаний з другою групою входів суматора порядку, перша група входів котрого з'єднана з виходом регістра порядку, вихід суматора порядку з'єднаний з виходом порядку, вихід тригера знака з'єднаний з виходом знака, а другий вихід третього вузла пам'яті приєднаний до виходу мантиси, причому виходи регістрів мантиси та порядку блока керування з'єднані з адресними входами першого вузла пам'яті, а тактовий вхід пристрою з'єднаний з тактовим входом тригера керування, вихід якого з'єднаний з інформаційним входом тригера переносу блока підсумовування, керуючий вхід комутатора блока підсумовування з'єднаний з виходом тригера переносу, з входом переносу та з двома старшими розрядами першої групи входів суматора мантиси, вихід комутатора зв'язаний з молодшими розрядами першої групи входів суматора мантиси, перший та другий інформаційні входи комутатора з'єднані відповідно з прямим та інверсним виходами (n-1)m- розрядного регістра мантиси, який відрізняється тим, що в пристрій введено блок множення, який містить вхід мантиси першого та вхід мантиси другого співмножників, вхід порядку першого та вхід порядку другого співмножників, вхід знака першого та вхід знака другого співмножників, регістр мантиси першого співмножника, регістр мантиси другого співмножника, регістр порядку першого співмножника, регістр порядку другого співмножника, тригер знака першого співмножника, тригер знака другого співмножника, вузол пам'яті добутків, суматор, елемент І, причому тактові входи регістрів мантиси, регістрів порядку, тригерів знака першого та другого співмножників з'єднані з тактовим входом пристрою, інформаційні входи регістрів мантиси першого та другого співмножників з'єднані відповідно з входами мантиси першого та другого співмножників блока множення, інформаційні входи регістрів порядку першого та другого співмножників з'єднані відповідно з входами порядку першого та другого співмножників блока множення, інформаційні входи тригерів знака першого та другого співмножників з'єднані відповідно з входами знака першого та другого співмножників блока множення, виходи регістрів мантиси першого та другого співмножників приєднані відповідно до першого та другого адресних входів вузла пам'яті добутків, виходи регістрів порядку першого та другого співмножників приєднані відповідно до першого та другого інформаційних входів суматора, виходи тригерів знака першого та другого співмножників приєднані відповідно до входів елементу І, а виходи вузла пам'яті добутків, суматора та елемента І з'єднані відповідно з інформаційними входами регістра мантиси, регістра порядку й тригера керування блока керування, усі непарні 3(n–1)-розрядні групи інформаційних входів регістра мантиси блока підсумовування з'єднані з першим 3(n–1)-розрядний виходом першого вузла пам'яті блока керування, другий 3(n–1)-розрядний вихід котрого зв'язаний з усіма парними 3(n–1)-розрядними групами інформаційних входів регістра мантиси блока підсумовування, керуючі входи встановлення в нуль кожної із [m/3] груп якого приєднані до третього [m/3]-розрядного виходу першого вузла пам'яті блока керування.

Текст

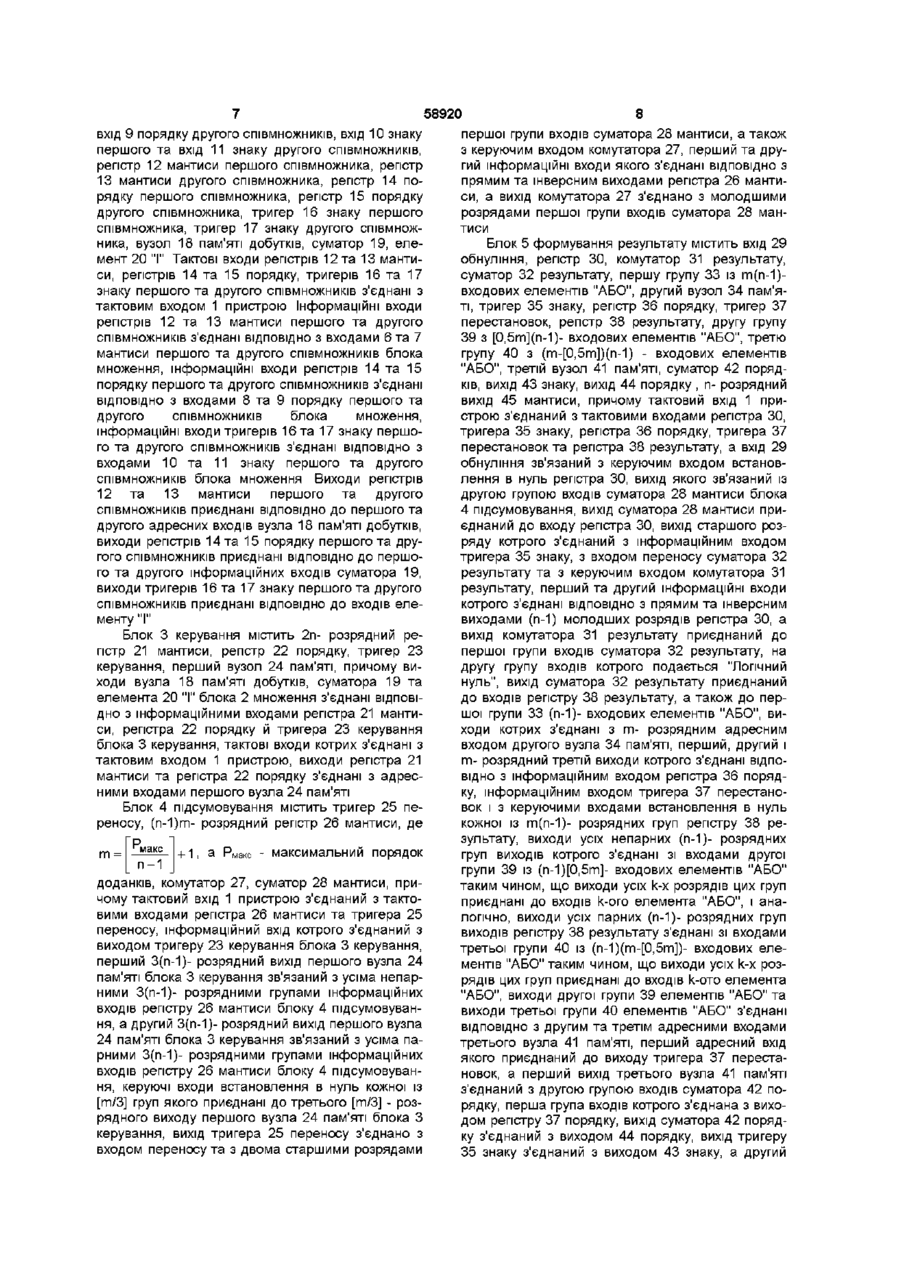

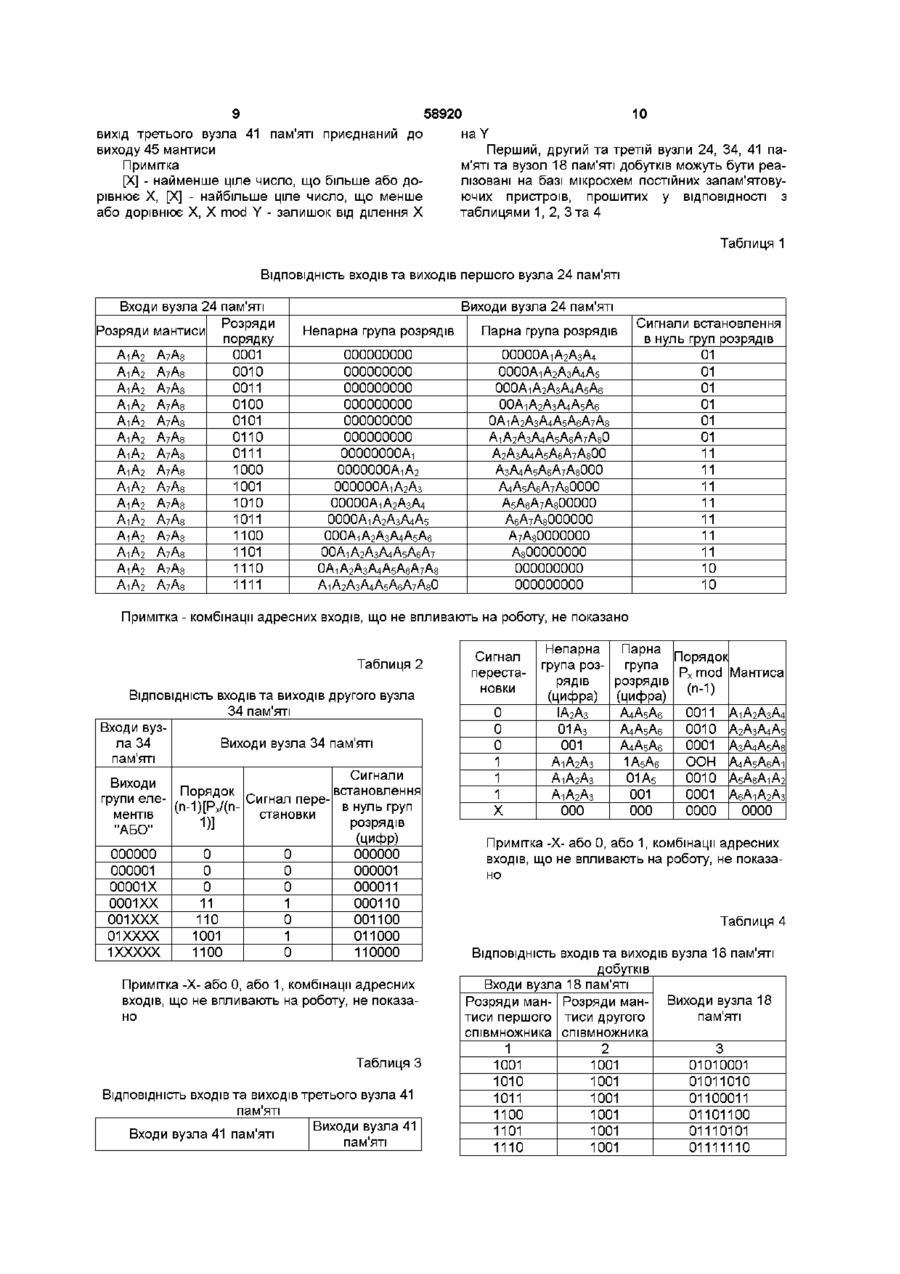

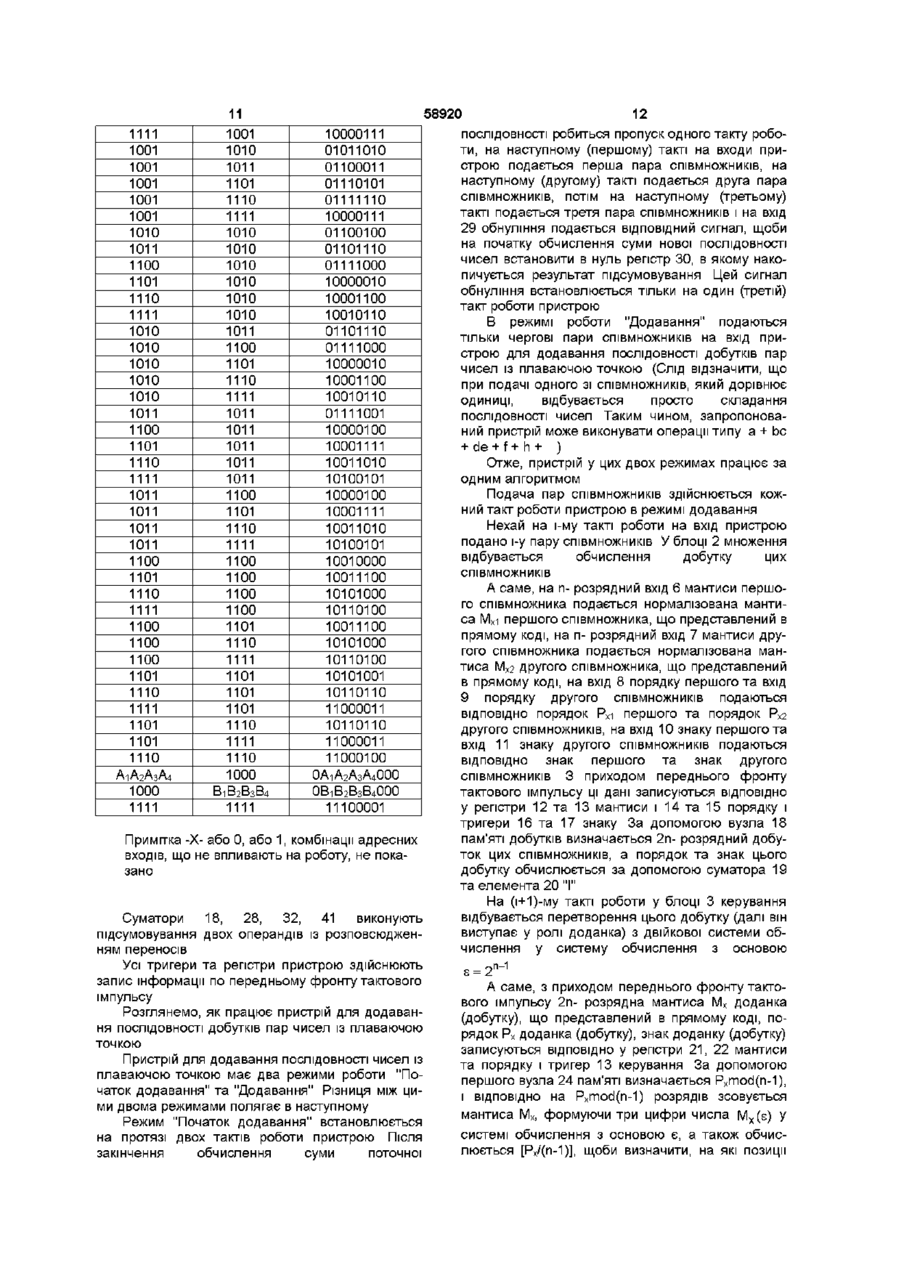

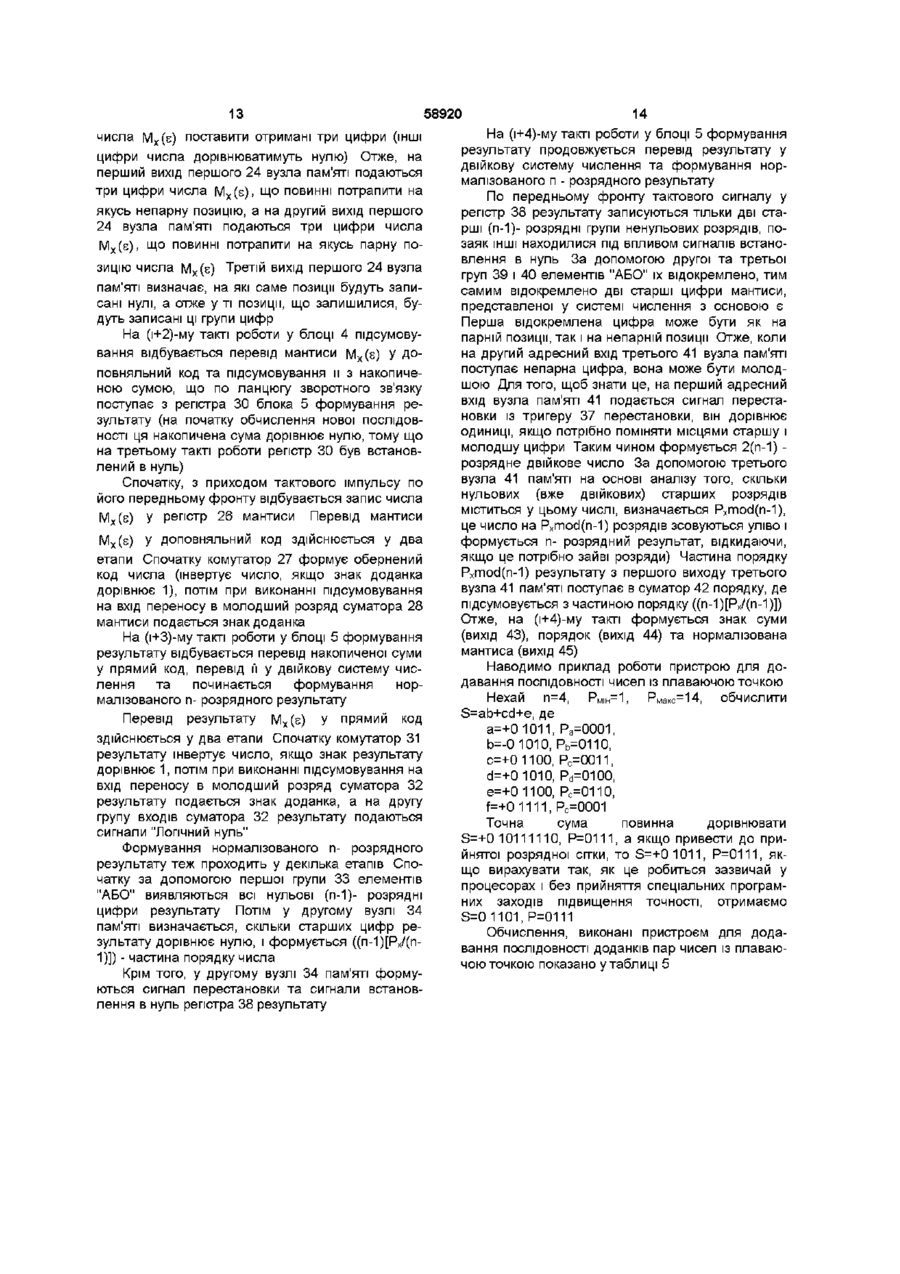

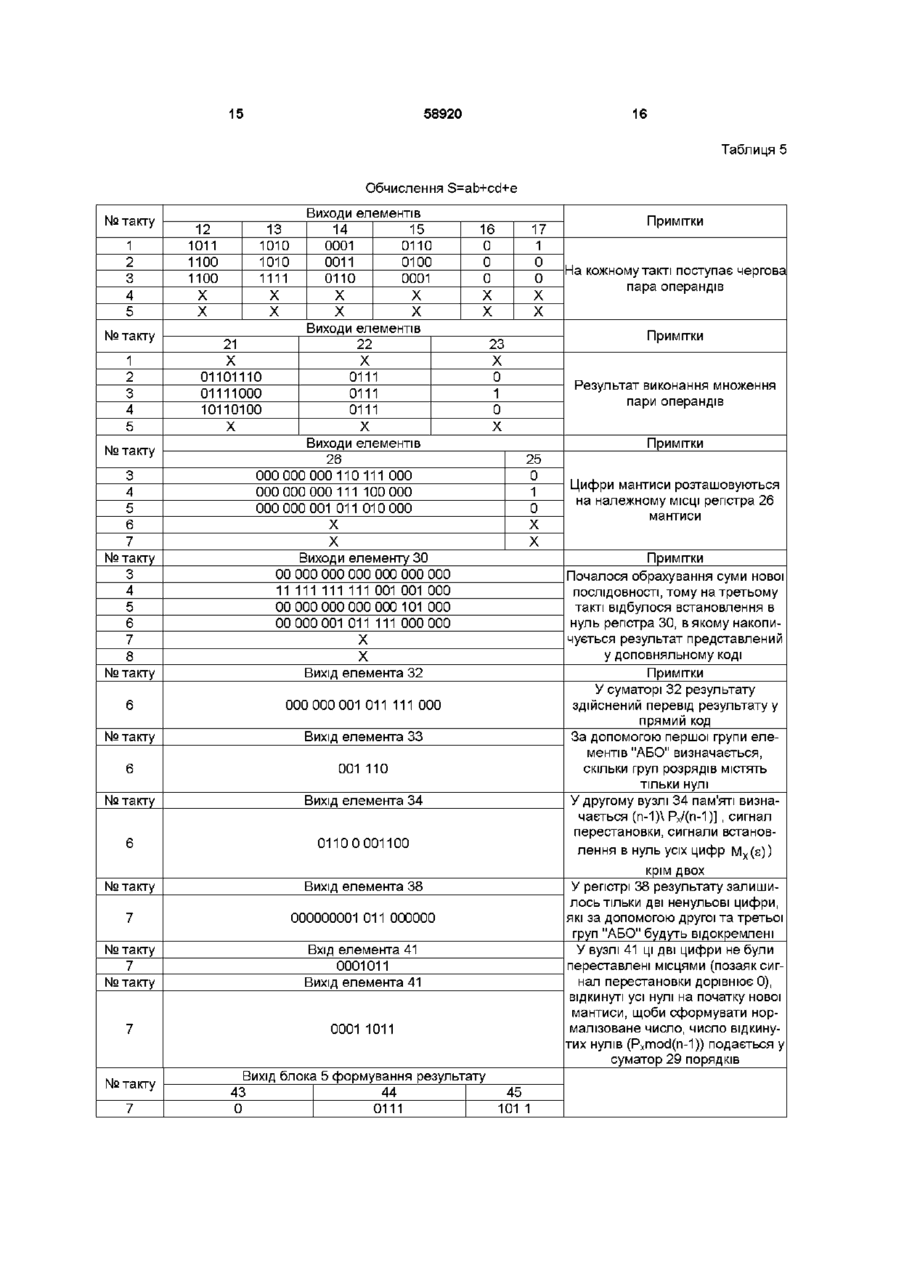

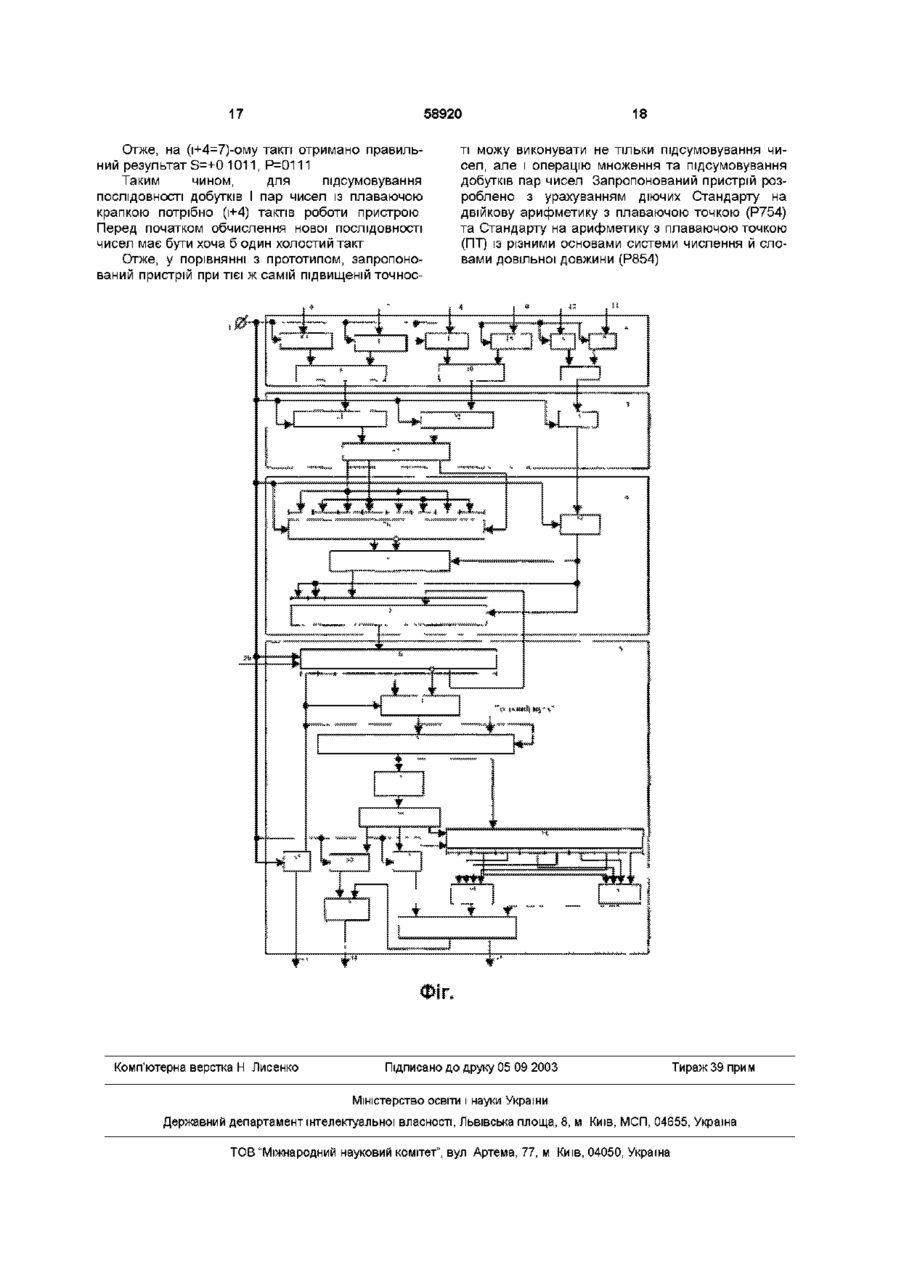

Пристрій для додавання ПОСЛІДОВНОСТІ до бутків пар чисел із плаваючою точкою, що містить тактовий вхід пристрою, блок керування, який містить тригер керування, регістри мантиси та порядку, перший вузол пам'яті, причому тактові входи регістра мантиси й регістра порядку з'єднані з тактовим входом пристрою, блок підсумовування, який містить регістр мантиси, тригер переносу, комутатор, суматор мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра мантиси та тригера переносу, та блок формування результату, який містить вхід обнуління, регістр, комутатор результату, суматор результату, першу групу із m(n-1) - входових елементів АБО, де п - розрядність мантиси, m = [Рмакс/п-1]+1,а Рнакс - МЭКСИМЭЛЬНИЙ ПОрЯДОК ДО данків, другий вузол пам'яті, тригер знака, регістр порядку, тригер перестановок, регістр результату, другу групу з (n-1)[0,5m] - входових елементів АБО, третю групу з (n-1)(m-[0,5m]) - входових елементів АБО, третій вузол пам'яті, суматор порядків, вихід знака, вихід порядку, п - розрядний вихід мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра, тригера знака, регістра порядку, тригера перестановок та регістра результату, а вхід обнуління зв'язаний з керуючим входом встановлення в нуль регістра, вихід якого зв'язаний із другою групою входів суматора мантиси блока підсумовування, вихід котрого приєднаний до входу регістра, вихід старшого розряду якого з'єднаний з інформаційним входом тригера знака, з входом переносу суматора результату та з керуючим входом комутатора результату, перший та другий інформаційні входи якого з'єднані ВІДПОВІДНО З прямим та інверсним виходами m(n-1) молодших розрядів регістра, а вихід комутатора результату приєднаний до першої групи входів суматора результату, на другу групу входів якого подається сигнал "Логічний нуль", вихід суматора результату приєднаний до входів регістра результату, а також до ВІДПОВІДНИХ ВХОДІВ першої групи (п-1) - входових елементів АБО, виходи яких з'єднані з т - розрядним адресним входом другого вузла пам'яті, перший, другий і m - розрядний третій виходи якого з'єднані ВІДПОВІДНО з інформаційним входом регістра порядку, інформаційним входом тригера перестановок і з керуючими входами встановлення в нуль кожної із m(n-1) - розрядних груп регістра результату, виходи усіх непарних (п-1) - розрядних груп виходів якого з'єднані зі входами другої групи із (п1)[0,5т] - входових елементів АБО таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента АБО, і аналогічно, виходи усіх парних (п-1) - розрядних груп виходів регістра результату з'єднані зі входами третьої групи із (п1)(m-[0,5m]) - входових елементів АБО таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента АБО, виходи другої групи елементів АБО та виходи третьої групи елементів АБО з'єднані ВІДПОВІДНО З другим та третім адресними входами третього вузла пам'яті, перший адресний вхід якого приєднаний до виходу тригера перестановок, а перший вихід третього вузла пам'яті з'єднаний з другою групою входів суматора порядку, перша група входів котрого з'єднана з виходом регістра порядку, вихід суматора порядку з'єднаний з виходом порядку, вихід тригера знака з'єднаний з виходом знака, а другий вихід третього вузла пам'яті приєднаний до виходу мантиси, причому виходи регістрів мантиси та порядку блока керування з'єднані з адресними входами першого вузла пам'яті, а тактовий вхід пристрою з'єднаний з тактовим входом тригера керування, вихід якого з'єднаний з інформаційним входом тригера переносу блока підсумовування, керуючий вхід комутатора блока підсумовування з'єднаний з виходом тригера переносу, з входом переносу та з двома старшими розрядами першої групи входів суматора мантиси, вихід комутатора зв'язаний з молодшими розрядами першої групи входів суматора мантиси, перший та другий інформаційні входи комутатора з'єднані ВІДПОВІДНО з прямим та інверсним виходами (n-1)m- розрядного регістра мантиси, який відрізняється тим, що в пристрій введено блок множення, який 00 ю 58920 містить вхід мантиси першого та вхід мантиси другого СПІВМНОЖНИКІВ, вхід порядку першого та вхід порядку другого СПІВМНОЖНИКІВ, вхід знака першого та вхід знака другого СПІВМНОЖНИКІВ, регістр мантиси першого співмножника, регістр мантиси другого співмножника, регістр порядку першого співмножника, регістр порядку другого співмножника, тригер знака першого співмножника, тригер знака другого співмножника, вузол пам'яті добутків, суматор, елемент І, причому тактові входи регістрів мантиси, регістрів порядку, тригерів знака першого та другого СПІВМНОЖНИКІВ з'єднані з тактовим входом пристрою, інформаційні входи регістрів мантиси першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО з входами мантиси першого та другого СПІВМНОЖНИКІВ блока множення, інформаційні входи регістрів порядку першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО З входами по рядку першого та другого СПІВМНОЖНИКІВ блока множення, інформаційні входи тригерів знака першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО з входами знака першого та другого Винахід відноситься до обчислювальної техніки і може бути використаний при побудові обчислювальних систем, у якості високопродуктивного блока, що забезпечує підвищену точність додавання ПОСЛІДОВНОСТІ добутків пар чисел із плаваючою точкою Відомий пристрій для додавання ПОСЛІДОВНОСТІ чисел із плаваючою комою (див авторське свідоцтво СРСР № 1182512 А, кл G06F7/50, 1985), що складається з однотипних блоків, причому кожний і-й блок містить регістр часткового результату, вузол формування часткового результату, тригер зберігання молодшого розряду кінцевого результату, елемент І, регістр порядку, вузол формування порядку, елемент АБО та два логічних вузли Недоліки цього пристрою - при роботі в режимі "Додавання" зовнішня обчислювальна система подає операнди на вхід пристрою не на кожному такті роботи, а тільки у ВІДПОВІДЬ на виставлення сигналу "Готовність", пристрій не виконує операцію множення Найбільш близький за технічною суттю до пристрою, що пропонується, є вибраний як прототип пристрій для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою (див позитивне рішення від 12 07 02 про видачу деклараційного патенту України по заявці №2002010246, кл G06F7/50), який завдяки заміни т блоків підсумовування одним блоком підсумовування й уведенням додатково блока формування результату зі зв'язками дозволяє в режимі "Додавання" подавати новий доданок на кожному такті роботи пристрою, що забезпечує підвищення швидкодії пристрою Пристрій містить тактовий вхід, блок керування, блок підсумовування, блок формування результату, причому блок керування містить прозрядний вхід мантиси, вхід порядку та вхід знака, регістр мантиси, регістр порядку, тригер керу СПІВМНОЖНИКІВ блока множення, виходи регістрів мантиси першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО до першого та другого адресних входів вузла пам'яті добутків, виходи регістрів порядку першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО ДО першого та другого інформаційних входів суматора, виходи тригерів знака першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО до входів елементу І, а виходи вузла пам'яті добутків, суматора та елемента І з'єднані ВІДПОВІДНО з інформаційними входами регістра мантиси, регістра порядку й тригера керування блока керування, усі непарні 3(п-1)-розрядні групи інформаційних входів регістра мантиси блока підсумовування з'єднані з першим 3(п-1)розрядний виходом першого вузла пам'яті блока керування, другий 3(п-1)-розрядний вихід котрого зв'язаний з усіма парними 3(п-1)-розрядними групами інформаційних входів регістра мантиси блока підсумовування, керуючі входи встановлення в нуль кожної із [т/3] груп якого приєднані до третього [т/3]-розрядного виходу першого вузла пам'яті блока керування вання, перший вузол пам'яті, блок підсумовування містить тригер переносу, (п-і)т-розрядний регістр "р мантиси, де m = Маіч° + 1 , а Нмяко - максимальп-1 ний порядок доданків, комутатор, суматор мантиси, блок формування результату містить вхід обнуління, регістр, комутатор результату, суматор результату, першу групу із т(п-1)-входових елементів "АБО", другий вузол пам'яті, тригер знаку, регістр порядку, тригер перестановок, регістр результату, другу групу з [0,5т](п-1)-входових елементів "АБО", третю групу з (m-[0,5m])(n-1)входових елементів "АБО", третій вузол пам'яті, суматор порядків, вихід знаку, вихід порядку , прозрядний вихід мантиси Основним недоліком даного пристрою є наступне пристрій не виконує операцію множення пар операндів В основу винаходу поставлено задачу вдосконалити пристрій для додавання ПОСЛІДОВНОСТІ добутків пар чисел з плаваючою точкою шляхом уведенням додатково блока множення зі зв'язками і частковою зміною зв'язків блока керування та блока підсумовування, з тим, щоб пристрій виконував не тільки операцію послідовного підсумовування чисел, але й послідовного підсумовування добутків пар чисел, що дозволяє розширити функціональні можливості пристрою Поставлена задача досягається тим, що в пристрої для додавання ПОСЛІДОВНОСТІ добутків пар чисел із плаваючою точкою, що містить тактовий вхід пристрою, блок керування, який містить тригер керування, регістри мантиси та порядку, перший вузол пам'яті, причому тактові входи регістра мантиси й регістра порядку з'єднані з тактовим входом пристрою, блок підсумовування, який містить регістр мантиси, тригер переносу, комутатор, 58920 суматор мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра мантиси та тригера переносу, та блок формування результату, який містить вхід обнуління, регістр, комутатор результату, суматор результату, першу групу із m(n-1)- входових елементів "АБО", де п - розрядність мантиси, m = п-1 + 1 , a Ph - максима льний порядок доданків, другий вузол памяті, тригер знаку, регістр порядку, тригер перестановок, регістр результату, другу групу з [0,5m](n-1)- входових елементів "АБО", третю групу з (m-[0,5m])(n1)-входових елементів "АБО", третій вузол пам'яті, суматор порядків, вихід знаку, вихід порядку , прозрядний вихід мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра, тригера знаку, регістра порядку, тригера перестановок та регістра результату, а вхід обнуління зв'язаний з керуючим входом встановлення в нуль регістра, вихід якого зв'язаний із другою групою входів суматора мантиси блока підсумовування, вихід котрого приєднаний до входу регістра, вихід старшого розряду котрого з'єднаний з інформаційним входом тригера знаку, з входом переносу суматора результату та з керуючим входом комутатора результату, перший та другий інформаційні входи котрого з'єднані ВІДПОВІДНО З прямим та інверсним виходами m(n-1) молодших розрядів регістра, а вихід комутатора результату приєднаний до першої групи входів суматора результату, на другу групу входів котрого подається сигнал "Логічний нуль", вихід суматора результату приєднаний до входів регістра результату, а також до ВІДПОВІДНИХ ВХОДІВ першої групи (п-і)-входових елементів "АБО", виходи котрих з'єднані з m-розрядним адресним входом другого вузла пам'яті, перший, другий і m-розрядний третій виходи котрого з'єднані ВІДПОВІДНО з інформаційним входом регістра порядку, інформаційним входом тригера перестановок і з керуючими входами встановлення в нуль кожної із т(п-1)-розрядних груп регістра результату, виходи усіх непарних (п-1)- розрядних груп виходів котрого з'єднані зі входами другої групи із (п1)[0,5т]- входових елементів "АБО" таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента "АБО", і аналогічно, виходи усіх парних (п-і)-розрядних груп виходів регістра результату з'єднані зі входами третьої групи із (п1)(m-[0,5m])- входових елементів "АБО" таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента "АБО", виходи другої групи елементів "АБО" та виходи третьої групи елементів "АБО" з'єднані ВІДПОВІДНО З другим та третім адресними входами третього вузла пам'яті, перший адресний вхід якого приєднаний до виходу тригера перестановок, а перший вихід третього вузла пам'яті з'єднаний з другою групою входів суматора порядку, перша група входів котрого з'єднана з виходом регістру порядку, вихід суматора порядку з'єднаний з виходом порядку, вихід тригеру знаку з'єднаний з виходом знаку, а другий вихід третього вузла пам'яті приєднаний до виходу мантиси, причому виходи регістрів мантиси та порядку блоку керування з'єднані з адресними входами першого вузла пам'яті, а тактовий вхід при строю з єднаний з тактовим входом тригера керування, вихід котрого з'єднаний з інформаційним входом тригера переносу блока підсумовування, керуючий вхід комутатора блока підсумовування з'єднаний з виходом тригера переносу, з входом переносу та з двома старшими розрядами першої групи входів суматора мантиси, вихід комутатора зв'язаний з молодшими розрядами першої групи входів суматора мантиси, перший та другий інформаційні входи комутатора з'єднані ВІДПОВІДНО з прямим та інверсним виходами (п1)-т- розрядного регістра мантиси, новим є те, що в пристрій введено блок множення, який містить вхід мантиси першого та вхід мантиси другого СПІВМНОЖНИКІВ, вхід порядку першого та вхід порядку другого СПІВМНОЖНИКІВ, вхід знаку першого та вхід знаку другого СПІВМНОЖНИКІВ, регістр мантиси першого співмножника, регістр мантиси другого співмножника, регістр порядку першого співмножника, регістр порядку другого співмножника, тригер знаку першого співмножника, тригер знаку другого співмножника, вузол пам'яті добутків, суматор, елемент "І", причому тактові входи регістрів мантиси, регістрів порядку, тригерів знаку першого та другого СПІВМНОЖНИКІВ з'єднані з тактовим входом пристрою, інформаційні входи регістрів мантиси першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО з входами мантиси першого та другого СПІВМНОЖНИКІВ блока множення, інформаційні входи регістрів порядку першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО з входами порядку першого та другого СПІВМНОЖНИКІВ блока множення, інформаційні входи тригерів знаку першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО З входами знаку першого та другого СПІВМНОЖНИКІВ блока множення, виходи регістрів мантиси першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО ДО першого та другого адресних входів вузла пам'яті добутків, виходи регістрів порядку першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО до першого та другого інформаційних входів суматора, виходи тригерів знаку першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО до входів елементу "І", а виходи вузла пам'яті добутків, суматора та елемента "І" з'єднані ВІДПОВІДНО з інформаційними входами регістра мантиси, регістра порядку й тригера керування блока керування, усі непарні 3(п-1)- розрядні групи інформаційних входів регістра мантиси блока підсумовування з'єднані з першим 3(п-1)розрядний виходом першого вузла пам'яті блока керування, другий 3(п-1)- розрядний вихід котрого зв'язаний з усіма парними 3(п-1)- розрядними групами інформаційних входів регістра мантиси блоку підсумовування, керуючі входи встановлення в нуль кожної із [т/3] груп якого приєднані до третього [т/3]- розрядного виходу першого вузла паМ'ЯТІ блока керування На кресленні представлено функціональну схему пристрою для додавання ПОСЛІДОВНОСТІ добутків пар чисел із плаваючою точкою Пристрій містить тактовий вхід 1, блок 2 множення, блок 3 керування, блок 4 підсумовування, блок 5 формування результату Блок 2 множення містить п- розрядний вхід 6 мантиси першого та п- розрядний вхід 7 мантиси другого СПІВМНОЖНИКІВ, вхід 8 порядку першого та 58920 вхід 9 порядку другого СПІВМНОЖНИКІВ, вхід 10 знаку першого та вхід 11 знаку другого СПІВМНОЖНИКІВ, регістр 12 мантиси першого співмножника, регістр 13 мантиси другого співмножника, регістр 14 порядку першого співмножника, регістр 15 порядку другого співмножника, тригер 16 знаку першого співмножника, тригер 17 знаку другого співмножника, вузол 18 пам'яті добутків, суматор 19, елемент 20 "І" Тактові входи регістрів 12 та 13 мантиси, регістрів 14 та 15 порядку, тригерів 16 та 17 знаку першого та другого СПІВМНОЖНИКІВ з'єднані з тактовим входом 1 пристрою Інформаційні входи регістрів 12 та 13 мантиси першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО З входами 6 та 7 мантиси першого та другого СПІВМНОЖНИКІВ блока множення, інформаційні входи регістрів 14 та 15 порядку першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО з входами 8 та 9 порядку першого та другого СПІВМНОЖНИКІВ блока множення, інформаційні входи тригерів 16 та 17 знаку першого та другого СПІВМНОЖНИКІВ з'єднані ВІДПОВІДНО З входами 10 та 11 знаку першого та другого СПІВМНОЖНИКІВ блока множення Виходи регістрів 12 та 13 мантиси першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО ДО першого та другого адресних входів вузла 18 пам'яті добутків, виходи регістрів 14 та 15 порядку першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО ДО першого та другого інформаційних входів суматора 19, виходи тригерів 16 та 17 знаку першого та другого СПІВМНОЖНИКІВ приєднані ВІДПОВІДНО ДО ВХОДІВ еле менту "І" Блок 3 керування містить 2п- розрядний регістр 21 мантиси, регістр 22 порядку, тригер 23 керування, перший вузол 24 пам'яті, причому виходи вузла 18 пам'яті добутків, суматора 19 та елемента 20 "І" блока 2 множення з'єднані ВІДПОВІДНО з інформаційними входами регістра 21 мантиси, регістра 22 порядку й тригера 23 керування блока 3 керування, тактові входи котрих з'єднані з тактовим входом 1 пристрою, виходи регістра 21 мантиси та регістра 22 порядку з'єднані з адресними входами першого вузла 24 пам'яті Блок 4 підсумовування містить тригер 25 переносу, (n-1)m- розрядний регістр 26 мантиси, де + 1, a Ph - максимальний порядок п-1 доданків, комутатор 27, суматор 28 мантиси, причому тактовий вхід 1 пристрою з'єднаний з тактовими входами регістра 26 мантиси та тригера 25 переносу, інформаційний вхід котрого з'єднаний з виходом тригеру 23 керування блока 3 керування, перший 3(п-1)- розрядний вихід першого вузла 24 пам'яті блока 3 керування зв'язаний з усіма непарними 3(п-1)- розрядними групами інформаційних входів регістру 26 мантиси блоку 4 підсумовування, а другий 3(п-1)- розрядний вихід першого вузла 24 пам'яті блока 3 керування зв'язаний з усіма парними 3(п-1)- розрядними групами інформаційних входів регістру 26 мантиси блоку 4 підсумовування, керуючі входи встановлення в нуль кожної із [т/3] груп якого приєднані до третього [т/3] - розрядного виходу першого вузла 24 пам'яті блока З керування, вихід тригера 25 переносу з'єднано з входом переносу та з двома старшими розрядами m= 8 першої групи входів суматора 28 мантиси, а також 3 керуючим входом комутатора 27, перший та другий інформаційні входи якого з'єднані ВІДПОВІДНО З прямим та інверсним виходами регістра 26 мантиси, а вихід комутатора 27 з'єднано з молодшими розрядами першої групи входів суматора 28 мантиси Блок 5 формування результату містить вхід 29 обнуління, регістр ЗО, комутатор 31 результату, суматор 32 результату, першу групу 33 із m(n-1)входових елементів "АБО", другий вузол 34 пам'яті, тригер 35 знаку, регістр 36 порядку, тригер 37 перестановок, регістр 38 результату, другу групу 39 з [0,5m](n-1)- входових елементів "АБО", третю групу 40 з (m-[0,5m])(n-1) - входових елементів "АБО", третій вузол 41 пам'яті, суматор 42 порядків, вихід 43 знаку, вихід 44 порядку , п- розрядний вихід 45 мантиси, причому тактовий вхід 1 пристрою з'єднаний з тактовими входами регістра ЗО, тригера 35 знаку, регістра 36 порядку, тригера 37 перестановок та регістра 38 результату, а вхід 29 обнуління зв'язаний з керуючим входом встановлення в нуль регістра ЗО, вихід якого зв'язаний із другою групою входів суматора 28 мантиси блока 4 підсумовування, вихід суматора 28 мантиси приєднаний до входу регістра ЗО, вихід старшого розряду котрого з'єднаний з інформаційним входом тригера 35 знаку, з входом переносу суматора 32 результату та з керуючим входом комутатора 31 результату, перший та другий інформаційні входи котрого з'єднані ВІДПОВІДНО З прямим та інверсним виходами (п-1) молодших розрядів регістра ЗО, а вихід комутатора 31 результату приєднаний до першої групи входів суматора 32 результату, на другу групу входів котрого подається "Логічний нуль", вихід суматора 32 результату приєднаний до входів регістру 38 результату, а також до першої групи 33 (п-1)- входових елементів "АБО", виходи котрих з'єднані з т - розрядним адресним входом другого вузла 34 пам'яті, перший, другий і т - розрядний третій виходи котрого з'єднані ВІДПОВІДНО з інформаційним входом регістра 36 порядку, інформаційним входом тригера 37 перестановок і з керуючими входами встановлення в нуль кожної із m(n-1)- розрядних груп регістру 38 результату, виходи усіх непарних (п-1)- розрядних груп виходів котрого з'єднані зі входами другої групи 39 із (n-1)[0,5m]- входових елементів "АБО" таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента "АБО", і аналогічно, виходи усіх парних (п-1)- розрядних груп виходів регістру 38 результату з'єднані зі входами третьої групи 40 із (n-1)(m-[0,5m])- входових елементів "АБО" таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ото елемента "АБО", виходи другої групи 39 елементів "АБО" та виходи третьої групи 40 елементів "АБО" з'єднані ВІДПОВІДНО з другим та третім адресними входами третього вузла 41 пам'яті, перший адресний вхід якого приєднаний до виходу тригера 37 перестановок, а перший вихід третього вузла 41 пам'яті з'єднаний з другою групою входів суматора 42 порядку, перша група входів котрого з'єднана з виходом регістру 37 порядку, вихід суматора 42 порядку з'єднаний з виходом 44 порядку, вихід тригеру 35 знаку з'єднаний з виходом 43 знаку, а другий вихід третього вузла 41 пам'яті приєднаний до виходу 45 мантиси Примітка [X] - найменше ціле число, що більше або дорівнює X, [X] - найбільше ціле число, що менше або дорівнює X, X mod Y - залишок від ділення X 10 58920 наУ Перший, другий та третій вузли 24, 34, 41 пам'яті та вузол 18 пам'яті добутків можуть бути реалізовані на базі мікросхем постійних запам'ятовуючих пристроїв, прошитих у ВІДПОВІДНОСТІ з таблицями 1, 2, 3 та 4 Таблиця 1 ВІДПОВІДНІСТЬ ВХОДІВ та виходів першого вузла 24 пам'яті Входи вузла 24 пам'яті Розряди Розряди мантиси порядку 0001 АіА 2 А 7 А 8 0010 АіА 2 А 7 А 8 0011 АіА 2 А 7 А 8 0100 АіА 2 А 7 А 8 АіА 2 А 7 А 8 0101 АіА 2 А 7 А 8 0110 АіА 2 А 7 А 8 0111 АіА 2 А 7 А 8 1000 АіА 2 А 7 А 8 1001 АіА 2 А 7 А 8 1010 АіА 2 А 7 А 8 1011 АіА 2 А 7 А 8 1100 АіА 2 А 7 А 8 1101 АіА 2 А 7 А 8 1110 АіА 2 А 7 А 8 1111 Виходи вузла 24 пам'яті Непарна група розрядів Парна група розрядів 000000000 000000000 000000000 000000000 000000000 000000000 00000000Аі 0000000АіА 2 000000АіА 2 А 3 00000АіА 2 А 3 А 4 0000АіА 2 А 3 А 4 А 5 000АіА 2 АзА 4 А 5 Аб 00АіА 2 АзА 4 А 5 АбА 7 0АіА 2 А 3 А 4 А 5 А 6 А 7 А 8 АіА 2 А 3 А 4 А 5 А 6 А 7 А 8 0 00000АіА 2 А 3 А 4 0000АіА 2 А 3 А 4 А 5 000АіА 2 А 3 А 4 А 5 А 6 00АіА 2 А 3 А 4 А 5 А 6 0АіА 2 А 3 А 4 А 5 А 6 А 7 А 8 АіА 2 А 3 А 4 А 5 А 6 А 7 А 8 0 А2А3А4А5А6А7А800 А 3 А 4 А 5 А 6 А 7 А 8 000 А 4 А 5 А 6 А 7 А 8 0000 А 5 А 6 А 7 А 8 00000 А 6 А 7 А 8 000000 А 7 А 8 0000000 А 8 00000000 000000000 000000000 Сигнали встановлення в нуль груп розрядів 01 01 01 01 01 01 11 11 11 11 11 11 11 10 10 Примітка - комбінації адресних входів, що не впливають на роботу, не показано Таблиця 2 ВІДПОВІДНІСТЬ ВХОДІВ та виходів другого вузла 34 пам'яті Входи вузла 34 Виходи вузла 34 пам'яті пам'яті Сигнали Виходи встановлення Порядок групи елеСигнал пере- в нуль груп ментів (п-1)[Рх/(п- становки розрядів 1)] "АБО" (цифр) 000000 0 0 000000 000001 0 0 000001 00001X 0 0 000011 0001XX 11 1 000110 001XXX 110 0 001100 01ХХХХ 1001 1 011000 1ХХХХХ 1100 0 110000 Примітка -X- або 0, або 1, комбінації адресних входів, що не впливають на роботу, не показано Таблиця З ВІДПОВІДНІСТЬ ВХОДІВ та виходів третього вузла 41 пам'яті Виходи вузла 41 Входи вузла 41 пам'яті пам'яті Непарна Парна Сигнал Порядок група роз- група перестарядів розрядів Р х mod Мантиса новки (цифра) (цифра) (п-1) 0 0011 АіА 2 А 3 А 4 ІА 2 А 3 А4А5А6 0 0010 А 2 А 3 А 4 А 5 01 Аз А4А5А6 0 001 0001 АзА 4 А 5 А 6 А4А5А6 1 АіА 2 А 3 1А 5 А 6 ООН А 4 А 5 А 6 Аі 1 01А 5 0010 А 5 А 6 АіА 2 АіА 2 А 3 1 001 0001 А 6 АіА 2 А 3 АіА 2 А 3 000 000 0000 0000 X Примітка -X- або 0, або 1, комбінації адресних входів, що не впливають на роботу, не показано Таблиця 4 ВІДПОВІДНІСТЬ ВХОДІВ та виходів вузла 18 пам'яті добутків Входи вузла 18 пам'яті Розряди ман- Розряди ман- Виходи вузла 18 пам'яті тиси першого тиси другого співмножника співмножника 1 2 3 1001 1001 01010001 1010 1001 01011010 1011 1001 01100011 1100 1001 01101100 1101 1001 01110101 1110 1001 01111110 11 1111 1001 1001 1001 1001 1001 1010 1011 1100 1101 1110 1111 1010 1010 1010 1010 1010 1011 1100 1101 1110 1111 1011 1011 1011 1011 1100 1101 1110 1111 1100 1100 1100 1101 1110 1111 1101 1101 1110 A1A2A3A4 1000 1111 1001 1010 1011 1101 1110 1111 1010 1010 1010 1010 1010 1010 1011 1100 1101 1110 1111 1011 1011 1011 1011 1011 1100 1101 1110 1111 1100 1100 1100 1100 1101 1110 1111 1101 1101 1101 1110 1111 1110 1000 B1B2B3B4 1111 10000111 01011010 01100011 01110101 01111110 10000111 01100100 01101110 01111000 10000010 10001100 10010110 01101110 01111000 10000010 10001100 10010110 01111001 10000100 10001111 10011010 10100101 10000100 10001111 10011010 10100101 10010000 10011100 10101000 10110100 10011100 10101000 10110100 10101001 10110110 11000011 10110110 11000011 11000100 0АіА2А3А4000 OB1B2B3B4OOO 11100001 Примітка -X- або 0, або 1, комбінації адресних входів, що не впливають на роботу, не показано Суматори 18, 28, 32, 41 виконують підсумовування двох операндів із розповсюдженням переносів Усі тригери та регістри пристрою здійснюють запис інформації по передньому фронту тактового імпульсу Розглянемо, як працює пристрій для додавання ПОСЛІДОВНОСТІ добутків пар чисел із плаваючою точкою Пристрій для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою має два режими роботи "Початок додавання" та "Додавання" Різниця між цими двома режимами полягає в наступному Режим "Початок додавання" встановлюється на протязі двох тактів роботи пристрою Після закінчення обчислення суми поточної 12 58920 ПОСЛІДОВНОСТІ робиться пропуск одного такту роботи, на наступному (першому) такті на входи пристрою подається перша пара СПІВМНОЖНИКІВ, на наступному (другому) такті подається друга пара СПІВМНОЖНИКІВ, потім на наступному (третьому) такті подається третя пара СПІВМНОЖНИКІВ І на вхід 29 обнуління подається ВІДПОВІДНИЙ сигнал, щоби на початку обчислення суми нової ПОСЛІДОВНОСТІ чисел встановити в нуль регістр ЗО, в якому накопичується результат підсумовування Цей сигнал обнуління встановлюється тільки на один (третій) такт роботи пристрою В режимі роботи "Додавання" подаються тільки чергові пари СПІВМНОЖНИКІВ на вхід пристрою для додавання ПОСЛІДОВНОСТІ добутків пар чисел із плаваючою точкою (Слід відзначити, що при подачі одного зі СПІВМНОЖНИКІВ, ЯКИЙ дорівнює одиниці, відбувається просто складання ПОСЛІДОВНОСТІ чисел Таким чином, запропонований пристрій може виконувати операції типу а + be + de + f + h + ) Отже, пристрій у цих двох режимах працює за одним алгоритмом Подача пар СПІВМНОЖНИКІВ ЗДІЙСНЮЄТЬСЯ КОЖ НИЙ такт роботи пристрою в режимі додавання Нехай на і-му такті роботи на вхід пристрою подано і-у пару СПІВМНОЖНИКІВ У блоці 2 множення відбувається обчислення добутку цих СПІВМНОЖНИКІВ А саме, на п- розрядний вхід 6 мантиси першого співмножника подається нормалізована мантиса Мхі першого співмножника, що представлений в прямому коді, на п- розрядний вхід 7 мантиси другого співмножника подається нормалізована мантиса МХ2 другого співмножника, що представлений в прямому коді, на вхід 8 порядку першого та вхід 9 порядку другого СПІВМНОЖНИКІВ подаються ВІДПОВІДНО порядок Рхі першого та порядок РХ2 другого СПІВМНОЖНИКІВ, на вхід 10 знаку першого та вхід 11 знаку другого СПІВМНОЖНИКІВ подаються ВІДПОВІДНО знак першого та знак другого СПІВМНОЖНИКІВ 3 приходом переднього фронту тактового імпульсу ці дані записуються ВІДПОВІДНО у регістри 12 та 13 мантиси і 14 та 15 порядку і тригери 16 та 17 знаку За допомогою вузла 18 пам'яті добутків визначається 2п- розрядний добуток цих СПІВМНОЖНИКІВ, а порядок та знак цього добутку обчислюється за допомогою суматора 19 та елемента 20 "І" На (і+1)-му такті роботи у блоці 3 керування відбувається перетворення цього добутку (далі він виступає у ролі доданка) з двійкової системи обчислення у систему обчислення з основою 8 = 2П"1 А саме, з приходом переднього фронту тактового імпульсу 2п- розрядна мантиса Мх доданка (добутку), що представлений в прямому коді, порядок Рх доданка (добутку), знак доданку (добутку) записуються ВІДПОВІДНО у регістри 21, 22 мантиси та порядку і тригер 13 керування За допомогою першого вузла 24 пам'яті визначається Pxmod(n-1), і ВІДПОВІДНО на Pxmod(n-1) розрядів зсовується мантиса Мх, формуючи три цифри числа M x (s) У системі обчислення з основою є, а також обчислюється [Рх/(п-1)], щоби визначити, на які позиції 13 числа M x (s) поставити отримані три цифри (ІНШІ цифри числа дорівнюватимуть нулю) Отже, на перший вихід першого 24 вузла пам'яті подаються три цифри числа M x (s), що повинні потрапити на якусь непарну позицію, а на другий вихід першого 24 вузла пам'яті подаються три цифри числа M x (s), що повинні потрапити на якусь парну позицію числа M x (s) Третій вихід першого 24 вузла пам'яті визначає, на які саме позиції будуть записані нулі, а отже у ті позиції, що залишилися, будуть записані ці групи цифр На (і+2)-му такті роботи у блоці 4 підсумовування відбувається перевід мантиси M x (s) У доповняльний код та підсумовування и з накопиченою сумою, що по ланцюгу зворотного зв'язку поступає з регістра ЗО блока 5 формування результату (на початку обчислення нової ПОСЛІДОВНОСТІ ця накопичена сума дорівнює нулю, тому що на третьому такті роботи регістр ЗО був встановлений в нуль) Спочатку, з приходом тактового імпульсу по його передньому фронту відбувається запис числа М х (s) У регістр 26 мантиси Перевід мантиси M x (s) У доповняльний код здійснюється у два етапи Спочатку комутатор 27 формує обернений код числа (інвертує число, якщо знак доданка дорівнює 1), потім при виконанні підсумовування на вхід переносу в молодший розряд суматора 28 мантиси подається знак доданка На (і+3)-му такті роботи у блоці 5 формування результату відбувається перевід накопиченої суми у прямий код, перевід її у двійкову систему числення та починається формування нормалізованого п- розрядного результату Перевід результату M x (s) У прямий код здійснюється у два етапи Спочатку комутатор 31 результату інвертує число, якщо знак результату дорівнює 1, потім при виконанні підсумовування на вхід переносу в молодший розряд суматора 32 результату подається знак доданка, а на другу групу входів суматора 32 результату подаються сигнали "Логічний нуль" Формування нормалізованого п- розрядного результату теж проходить у декілька етапів Спочатку за допомогою першої групи 33 елементів "АБО" виявляються всі нульові (п-1)- розрядні цифри результату Потім у другому вузлі 34 пам'яті визначається, скільки старших цифр результату дорівнює нулю, і формується ((п-1)[Рх/(п1)]) - частина порядку числа Крім того, у другому вузлі 34 пам'яті формуються сигнал перестановки та сигнали встановлення в нуль регістра 38 результату 14 На (і+4)-му такті роботи у блоці 5 формування результату продовжується перевід результату у двійкову систему числення та формування нормалізованого п - розрядного результату По передньому фронту тактового сигналу у регістр 38 результату записуються тільки дві старші (п-1)- розрядні групи ненульових розрядів, позаяк ІНШІ находилися під впливом сигналів встановлення в нуль За допомогою другої та третьої груп 39 і 40 елементів "АБО" їх відокремлено, тим самим відокремлено дві старші цифри мантиси, представленої у системі числення з основою є Перша відокремлена цифра може бути як на парній позиції, так і на непарній позиції Отже, коли на другий адресний вхід третього 41 вузла пам'яті поступає непарна цифра, вона може бути молодшою Для того, щоб знати це, на перший адресний вхід вузла пам'яті 41 подається сигнал перестановки із тригеру 37 перестановки, він дорівнює одиниці, якщо потрібно поміняти місцями старшу і молодшу цифри Таким чином формується 2(п-1) розрядне двійкове число За допомогою третього вузла 41 пам'яті на основі аналізу того, скільки нульових (вже двійкових) старших розрядів міститься у цьому числі, визначається Pxmod(n-1), це число на Pxmod(n-1) розрядів зсовуються уліво і формується п- розрядний результат, відкидаючи, якщо це потрібно зайві розряди) Частина порядку Pxmod(n-1) результату з першого виходу третього вузла 41 пам'яті поступає в суматор 42 порядку, де підсумовується з частиною порядку ((п-1)[Рх/(п-1)]) Отже, на (і+4)-му такті формується знак суми (вихід 43), порядок (вихід 44) та нормалізована мантиса (вихід 45) 58920 Наводимо приклад роботи пристрою для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою Нехай п=4, Рнін-1, Рнакс-14, обчислити S=ab+cd+e, де а=+0 1011, Ра=0001, Ь=-0 1010, Рь=0110, с=+01100, Рс=0011, d=+0 1010, Pd=0100, е=+0 1100, Рс=0110, f=+0 1111, Рс=0001 Точна сума повинна дорівнювати S=+0 10111110, Р=0111, а якщо привести до прийнятої розрядної сітки, то S=+0 1011, Р=0111, якщо вирахувати так, як це робиться зазвичай у процесорах і без прийняття спеціальних програмних заходів підвищення точності, отримаємо S=0 1101, Р=0111 Обчислення, виконані пристроєм для додавання ПОСЛІДОВНОСТІ доданків пар чисел із плаваючою точкою показано у таблиці 5 58920 15 16 Таблиця 5 Обчислення S=ab+cd+e № такту 1 2 3 4 5 № такту 1 2 3 4 5 Виходи елементів 12 13 14 15 1011 1100 1100 1010 1010 1111 0001 0011 0110 0110 0100 0001 X X X X X X X X 16 0 0 0 X X 17 1 0 0 X X Виходи елементів 21 X 22 X 01101110 01111000 10110100 0111 0111 0111 X Результат виконання множення пари операндів Виходи елементів № такту Примітки 26 25 0 1 0 X X 000 000 000 110 111 000 000 000 000 111 100 000 000 000 001 011 010 000 3 4 5 6 7 X X № такту 00 11 00 00 3 4 5 6 7 8 Виходи 000 000 111 111 000 000 000 001 елементу ЗО 000 000 000 000 111 001 001 000 000 000 101 000 011 111 000 000 Вихід елемента 32 6 000 000 001 011 111 000 № такту Вихід елемента 33 6 001 110 № такту Вихід елемента 34 6 01100001100 № такту Вихід елемента 38 7 000000001 011 000000 № такту № такту Вхід елемента 41 0001011 Вихід елемента 41 7 0001 1011 7 № такту 7 Примітки У суматорі 32 результату здійснений перевід результату у прямий код За допомогою першої групи елементів "АБО" визначається, скільки груп розрядів містять тільки нулі У другому вузлі 34 пам'яті визначається (п-1)\ Рх/(п-1)] , сигнал перестановки, сигнали встановлення в нуль усіх цифр M x (s)) крім двох У регістрі 38 результату залишилось тільки дві ненульові цифри, які за допомогою другої та третьої груп "АБО" будуть відокремлені У вузлі 41 ці дві цифри не були переставлені місцями (позаяк сигнал перестановки дорівнює 0), відкинуті усі нулі на початку нової мантиси, щоби сформувати нормалізоване число, число відкинутих нулів (Pxmod(n-1)) подається у суматор 29 порядків Вихід блока 5 формування результату 43 0 Цифри мантиси розташовуються на належному МІСЦІ регістра 26 мантиси Примітки Почалося обрахування суми нової ПОСЛІДОВНОСТІ, тому на третьому такті відбулося встановлення в нуль регістра ЗО, в якому накопичується результат представлений у доповняльному коді X X № такту Ча кожному такті поступає чергова пара операндів Примітки 23 X 0 1 0 X X Примітки 44 45 0111 101 1 58920 17 Отже, на (і+4=7)-ому такті отримано правильний результат S=+0 1011, Р=0111 Таким чином, для підсумовування ПОСЛІДОВНОСТІ добутків І пар чисел із плаваючою крапкою потрібно (і+4) тактів роботи пристрою Перед початком обчислення нової ПОСЛІДОВНОСТІ чисел має бути хоча б один холостий такт Отже, у порівнянні з прототипом, запропонований пристрій при тієї ж самій підвищеній точнос Комп'ютерна верстка Н Лисенко 18 ті можу виконувати не тільки підсумовування чисел, але і операцію множення та підсумовування добутків пар чисел Запропонований пристрій розроблено з урахуванням діючих Стандарту на двійкову арифметику з плаваючою точкою (Р754) та Стандарту на арифметику з плаваючою точкою (ПТ) із різними основами системи числення й словами довільної довжини (Р854) Підписано до друку 05 09 2003 Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ТОВ "Міжнародний науковий комітет", вул Артема, 77, м Київ, 04050, Україна

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for summing a series of products of floating-point numbers

Назва патенту російськоюУстройство для суммирования последовательности произведений чисел с плавающей запятой

МПК / Мітки

МПК: G06F 7/507

Мітки: чисел, додавання, плаваючою, пристрій, послідовності, точкою, добутків, пар

Код посилання

<a href="https://ua.patents.su/9-58920-pristrijj-dlya-dodavannya-poslidovnosti-dobutkiv-par-chisel-iz-plavayuchoyu-tochkoyu.html" target="_blank" rel="follow" title="База патентів України">Пристрій для додавання послідовності добутків пар чисел із плаваючою точкою</a>

Попередній патент: Спосіб прогнозування виникнення раку шийки матки

Наступний патент: Гранульований теплоізоляційний матеріал і композиція для його одержання

Випадковий патент: Синергічні фунгіцидні композиції