Автоматизована система тестового контролю і діагностування цифрових мікропроцесорних блоків

Номер патенту: 28350

Опубліковано: 16.10.2000

Автори: Глущак Сергій Валеріанович, Огневий Олександр Вікторович, Локазюк Віктор Миколайович, Чешун Віктор Миколайович, Хмельницький Юрій Владиславович

Формула / Реферат

Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков, содержащая в устройстве формирования тестовой информации блок управления, блок ввода программ, блок памяти и регистратор, входы-выходы которых соединены с каналом передачи данных, с которым также соединены первые группы входов-выходов процессора управления вводом-выводом тестовой информации и блока памяти тестовых воздействий и ответных реакций, вторая группа входов-выходов процессора управления вводом-выводом тестовой информации, первая группа входов блока памяти тестовых воздействийи ответных реакций, группа входов-выходов сигнатурного анализатора и выходы объекта контроля соединены с системной магистралью, вторая группа входов и вторая группа входов-выходов блока памяти тестовых воздействий и ответных реакций соединены соответственно с выходами второго блока преобразования и первой группой входов-выходов первого блока преобразования, вторая группа входов-выходов которого соединена с первой группой входов-выходов блока контактирования, вторая группа входов-выходов которого соединена с группой входов-выходов объекта контроля, первая группа входов-выходов многоконтактного устройства соединена с группой входов-выходов БИС в составе объекта контроля, вторая группа входов-выходов соединена с первой группой вводов-выходов коммутатора, выходы которого соединены с входами сигнатурного анализатора, вторая группа входов-выходов соединена с группой входов, выходов второго блока преобразования, отличающаяся тем, что в систему введен блок формирования импульсов, состоящий из узла ввода-вывода, узла шинных формирователей, узла формирования адреса, узла оперативных запоминающих устройств, узла сдвиговых регистров и узла коммутаторов, первые группы входов узла ввода-вывода, узла шинных формирователей, узла формирования адреса, узла оперативных запоминающих устройств, узла сдвиговых регистров и узда коммутаторов, соединение системной магистралью, вторая группа входов узла ввода-вывода соединена с группой выходов блока памяти тестовых воздействий и ответных реакций, первая группа выходов узла ввода-вывода соединена со второй группой входов узла шинных формирователей, вторая группа выходов узла ввода-вывода соединена со второй группой входов узла формирования адреса, группа выходов которого соединена со второй группой входов узла оперативных запоминающих устройств, группа выходов узла шинных формирователей соединена с группой входов-выходов узла оперативных запоминающих устройств и второй группой входов узла сдвиговых регистров, группа выходов которого соединена со вторыми входами узла коммутаторов, группа выходов которого соединена с группой входов второго блока преобразования.

Текст

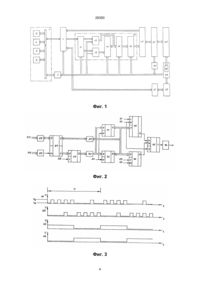

Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков, содержащая в устройстве формирования тестовой информации блок управления, блок ввода программ, блок памяти и регистратор, входы-выходы которых соединены с каналом передачи данных, с которым также соединены первые группы входов-выходов процессора управления вводом-выводом тестовой информации и блока памяти тестовых воздействий и ответных реакций, вторая группа входов-выходов процессора управления вводом-выводом тестовой информации, первая группа входов блока памяти тестовых воздействий и ответных реакций, группа входов-выходов сигнатурного анализатора и выходы объекта контроля соединены с системной магистралью, вторая группа входов и вторая группа входов-выходов блока памяти тестовых воздействий и ответных реакций соединены соответственно с выходами второго блока преобразования и первой группой входов-выходов первого блока преобразования, вторая группа входоввыходов которого соединена с первой группой входов-выходов блока контактирования, вторая группа входов-выходов которого соединена с группой входов-выходов объекта контроля, первая A (54) АВТОМАТИЗОВАНА СИСТЕМА ТЕСТОВОГО КОНТРОЛЮ І ДІАГНОСТУВАННЯ ЦИФРОВИХ МІКРОПРОЦЕСОРНИХ БЛОКІВ 28350 ния, второй блок преобразования, сигнатурный анализатор, коммутатор, многоконтактное устройство с соответствующими связями. Недостатком указанной системы является разделение функций формирования длительностей и задержек сигналов тестовых воздействий между двумя отдельными блоками, использующими в качестве формирующих элементов RСцепочки (взаимное влияние погрешностей формирования сигналов RС-цепочками каждого блока приводит к возникновению суммарной погрешности сформированного сигнала со значениями до десятков процентов), работающими последовательно и не позволяющими производить формирование результирующего сигнала одновременно с запрограммированными значениями задержки и длительности. В основу предлагаемого изобретения поставлена задача повышения достоверности контроля и диагностирования цифровых микропроцессорных блоков системой за счет снижения погрешности формирования сигналов тестовых воздействий с программируемой задержкой и длительностью, которые формируются вводимым в состав системы блоком формирования импульсов вместо блока формирования длительностей сигналов тестовых воздействий и блока формирования задержек сигналов тестовых воздействий в прототипе, использующим цифровой способ формирования длительности и задержки сигналов тестовых воздействий, основанный на использовании в качестве формирующих элементов сдвиговых регистров вместо формирования на RС-цепочках в прототипе. Поставленная задача решается тем, что в автоматизированную систему тестового контроля и диагностирования цифровых микропроцессорных блоков, содержащую в устройстве формирования тестовой информации блок управления, блок ввода программ, блок памяти и регистратор, входывыходы которых соединены с каналом передачи данных, с которым также соединены первые группы входов-выходов процессора управления вводом-выводом тестовой информации и блока памяти тестовых воздействий и ответных реакций, вторая группа входов-выходов процессора управления вводом-выводом тестовой информации, первая группа входов блока памяти тестовых воздействий и ответных реакций, группа входов-выходов сигнатурного анализатора и выходы объекта контроля соединены с системной магистралью, вторая группа входов и вторая группа входоввыходов блока памяти тестовых воздействий и ответных реакций соединены соответственно с выходами второго блока преобразования и первой группой входов-выходов первого блока преобразования, вторая группа входов-выходов которого соединена с первой группой входов-выходов блока контактирования, вторая группа входоввыходов которого соединена с группой входоввыходов объекта контроля, первая группа входоввыходов многоконтактного устройства соединена с группой входов-выходов БИС в составе объекта контроля, вторая группа входов-выходов соединена с первой группой входов-выходов коммутатора, выходы которого соединены с входами сигнатурного анализатора, вторая группа входов-выходов соединена с группой входов-выходов второго блока преобразования, согласно предложенному изобретению, введен блок формирования импульсов, состоящий из узла ввода-вывода, узла шинных формирователей, узла формирования адреса, узла оперативных запоминающих устройств, узла сдвиговых регистров и узла коммутаторов, первые группы входов узла ввода-вывода, узла шинных формирователей, узла формирования адреса, узла оперативных запоминающих устройств, узла сдвиговых регистров и узла коммутаторов соединены с системной магистралью, вторая группа входов узла ввода-вывода соединена с группой выходов блока памяти тестовых воздействий и ответных реакций, первая группа выходов узла ввода-вывода соединена со второй группой входов узла шинных формирователей, вторая группа выходов узла ввода-вывода соединена со второй группой входов узла формирования адреса, группа выходов которого соединена со второй группой входов узла оперативных запоминающих устройств, группа выходов узла шинных формирователей соединена с группой входов-выходов узла оперативных запоминающих устройств и второй группой входов узла сдвиговых регистров, группа выходов которого соединена с входами узла коммутаторов, группа выходов которого соединена с группой входов второго блока преобразования. Структурная схема предлагаемой системы приведена на фиг. 1. На фиг. 2 показана функциональная схема блока формирования импульсов. На фиг. 3 приведены временные диаграммы работы блока. Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков содержит в устройстве 1 формирования тестовой информации блок 2 управления, канал 3 передачи данных, блок 4 ввода программ, блок 5 памяти и регистратор 6, процессор 7 управления вводом-выводом тестовой информации, системную магистраль 8, блок 9 памяти тестовых воздействий и ответных реакций, блок формирования импульсов 10, состоящий из узла ввода-вывода 11, узла шинных формирователей 12, узла формирования адреса 13, узла оперативных запоминающих устройств 14, узла сдвиговых регистров 15 и узла коммутаторов 16, блок 17 преобразования, блок 18 контактирования, блок 19 преобразования, сигнатурный анализатор 20, коммутатор 21, многоконтактное устройство 22, объект контроля 23, содержащий БИС 24, с соответствующими связями. Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков работает следующим образом. Объект 23 контроля подключается к блоку 18 контактирования, который обеспечивает электрическую связь между контактами краевого разъема объекта 23 контроля и блоком 17 преобразования. Программа контроля с помощью блока 2 управления и блока 4 ввода программ поступает в блок 5 памяти. Затем тестовые воздействия из блока 5 памяти записываются в блок 9 памяти тестовых воздействий и ответных реакций, информация о настройке блока 9 записывается из блока 5 памяти в процессор 7 управления вводом-выводом тестовой информации. Блок 9 памяти тестовых 2 28350 воздействий и ответных реакций настраивается на подачу тестовых воздействий через блок 17 преобразования и блок 18 контактирования, отключающих БИС 24 от соответствующих входоввыходов соседних узлов объекта 23 контроля. Блок 2 управления отключается от процессора 7, снимая сигнал "Захват", отрабатывая программу перезаписи тестовой информации из оперативной памяти процессора 7. Тестовая информация поступает на соответствующие входы объекта 23 контроля и БИС 24. Сигналы ответных реакций через многоконтактное устройство 22, коммутатор 21 могут поступать либо на сигнатурный анализатор 20 для формирования сигнатур и в дальнейшем их сравнения с помощью процессора 7 с эталонными, при этом результат сравнения дает информацию об исправности БИС 24, либо в блок памяти 9 тестовых воздействий и ответных реакций для уточнения неисправности БИС 24 путем сравнения ответных реакций с эталонными. Блок 10 формирования импульсов задает необходимую временную диаграмму работы БИС 24. Данные формируемых задержек и длительностей тестовых воздействий из блока 9 памяти тестовых воздействий и ответных реакций записываются через узел ввода-вывода 11 и узел шинных формирователей 12 под управлением поступающей из процессора 7 управляющей информации и узла формирования адреса 13 в узел оперативных запоминающих устройств 14. Из узла оперативных запоминающих устройств 14 записанные данные поступают через узел сдвиговых регистров 15 в узел 16 коммутаторов, откуда сформированные импульсы передаются в блок 19 преобразования. Работа блока формирования импульсов поясняется приведенной на фиг. 2 функциональной схемой и приведенными на фиг. 3 временными диаграммами. Согласно фиг. 2 один канал блока формирования импульсов содержит шинный формирователь 25, дешифратор 26, программируемый параллельный интерфейс 27, счетчик 28, шинные формирователи 29 и 30, оперативные запоминающие устройства 31 и 32, сдвиговые регистры 33 и 34, коммутатор 35, буферный элемент 36, вход шины данных 37, вход шины адреса 38, вход тактирования 39, вход управления оперативными запоминающими устройствами 40, вход тактирования 41 и вход управления 42 для регистра 33, вход тактирования 43 и вход управления 44 для регистра 34. Блок работает следующим образом. Первоначально производится запись данных в оперативные запоминающие устройства 31 и 32. Информация о параметрах формируемых импульсов от входов 37 через шинный формирователь 25 поступает в программируемый параллельный интерфейс 27, выборка которого осуществляется посредством дешифратора 26, формирующего сигнал выборки СS на основании установленного на входах 38 адреса. Из порта А программируемого параллельного интерфейса 27 по лученные данные через шинный формирователь 29 записываются в оперативные запоми- нающие устройства 31 и 32, которые устанавливаются в режим записи сигналом, поданным на вход управления оперативными запоминающими устройствами 40 по адресу, поступающему через шинный формирователь 30 со счетчика 28, который инициализируется портом С программируемого параллельного интерфейса 27 и формирует адреса под управлением сигнала, поданного на вход тактирования 39. После записи исходных данных оперативные запоминающие устройства 31 и 32 переключаются в режим чтения сигналом, поступающим на вход управления 40 оперативными запоминающими устройствами, и блок переходит в режим формирования импульса. Временные диаграммы, поясняющие работу блока в режиме формирования импульса при 4разрядных сдвиговых регистрах, представлены на фиг. 3. За время такта Т импульса для управления работой регистров сдвига 33 и 34 подается восемь тактовых импульсов длительностью Т/8. Первые четыре импульса поступают на вход 41 тактирования сдвигового регистра 33 (фиг. 3, 41), который по сигналу, поданному на вход 42, устанавливается в режим сдвига (фиг. 3, 42). Сигнал, установленный на входе 42, переводит коммутатор 35 в режим приема сигнала с выхода сдвигового регистра 33. В это время регистр 34 сигналом, поданным на вход 44 (фиг. 3, 44), устанавливается в режим параллельной загрузки и по тактовому импульсу, подаваемому на вход 43 (фиг. 3, 43), загружает данные из оперативного запоминающего устройства 32. Следующие четыре импульса поступают на вход 43 тактирования сдвигового регистра 34, а сдвиговый регистр 33 сигналом, подаваемым на вход 42, устанавливается в режим параллельной загрузки из оперативного запоминающего устройства 31, поступающий на вход 42 сигнал переводит коммутатор 35 в режим приема сигнала с выхода сдвигового регистра 34, который устанавливается поступающим на вход 44 сигналом в режим сдвига. Формируемый выходной сигнал с коммутатора 35 через буферный элемент 36 поступает на выход блока. Таким образом, в каждом такте Т формируется импульс длительностью кТ/8 и задержкой nТ/8, где к-количество последовательных бит значений одного логического уровня, а n-количество последовательных бит значений другого логического уровня. Поочередная подача значений одного и другого уровня в течение одного такта Т позволяет сформировать в течение такта несколько импульсов с запрограммированной задержкой и длительностью, минимальные значения задержки и длительности при этом ограничиваются частотой, подаваемой на входы тактирования 41 и 43, и равны Т/8. Источники информации 1. А.c. СССР по заявке № 4726836/21 от 15.06.1989 г. 3 28350 Фиг. 1 Фиг. 2 Фиг. 3 4 28350 __________________________________________________________ ДП "Український інститут промислової власності" (Укрпатент) Україна, 01133, Київ-133, бульв. Лесі Українки, 26 (044) 295-81-42, 295-61-97 __________________________________________________________ Підписано до друку ________ 2002 р. Формат 60х84 1/8. Обсяг ______ обл.-вид. арк. Тираж 34 прим. Зам._______ __________________________________________________________ УкрІНТЕІ, 03680, Київ-39 МСП, вул. Горького, 180. (044) 268-25-22 __________________________________________________________ 5

ДивитисяДодаткова інформація

Назва патенту англійськоюAutomated system for test control and diagnostics of digital microprocessor blocks

Автори англійськоюLokaziuk Viktor Mykolaiovych, Khmelnytskyi Yurii Vladyslavovych, Ohnevyi Oleksandr Viktorovych, Cheshun Viktor Mykolaiovych, Hluschak Serhii Valerianovych

Назва патенту російськоюStarwriterавтоматизированная система тестового контроля и диагностики цифровых микропроцессорных блоков

Автори російськоюЛоказюк Виктор Николаевич, Хмельницкий Юрий Владиславович, Огневой Александр Викторович, Чешун Виктор Николаевич, Глущак Сергей Валерианович

МПК / Мітки

МПК: G01R 31/28, G01F 17/00

Мітки: тестового, блоків, контролю, цифрових, система, мікропроцесорних, автоматизована, діагностування

Код посилання

<a href="https://ua.patents.su/5-28350-avtomatizovana-sistema-testovogo-kontrolyu-i-diagnostuvannya-cifrovikh-mikroprocesornikh-blokiv.html" target="_blank" rel="follow" title="База патентів України">Автоматизована система тестового контролю і діагностування цифрових мікропроцесорних блоків</a>

Попередній патент: Пристрій для лікування сколіозу

Наступний патент: Пристрій для стерілізації харчових консервів за допомогою нвч енергії

Випадковий патент: Склад комплексного поживного середовища для отримання ентомоцидного біопрепарату