Дешифратор семисегментного коду в унітарний

Номер патенту: 108579

Опубліковано: 25.07.2016

Автори: Гаврілов Дмитро Володимирович, Бєлов Олександр Едуардович, Ситай Юрій Вікторович, Басич Богдан Вікторович

Формула / Реферат

Перетворювач коду семисегментного індикатора в двійково-десятковий код, що містить шість вхідних шин, чотири вихідних шини, п'ять інверторів, четвертий з яких з'єднаний з шостою вхідною шиною, який відрізняється тим, що в нього введено шостий інвертор, двадцять два елементи І, три транзистори, шість резисторів, сьома вхідна шина та шість вихідних шин, причому вхід першого інвертора з'єднаний з першою вхідною шиною, вхід другого інвертора з'єднаний з другою вхідною шиною , вхід третього інвертора з'єднаний з п'ятою вхідною шиною, вхід п'ятого інвертора з'єднаний з колектором першого транзистора, вхід шостого інвертора з'єднаний з четвертою вхідною шиною, входи першого елемента І з'єднані з п'ятою та шостою вхідними шинами, входи другого елемента І з'єднані з третьою вхідною шиною та виходом другого інвертора, входи третього елемента І з'єднані з виходами другого та третього інверторів, а вихід під'єднаний до п'ятої вихідної шини, входи четвертого елемента І з'єднані з першою та другою вхідними шинами, входи п'ятого елемента І з'єднані з сьомою вхідною шиною та виходом першого інвертора, входи шостого елемента І з'єднані з четвертою вхідною шиною та виходом першого елемента І, входи сьомого елемента І з'єднані з четвертою та сьомою вхідними шинами, входи восьмого елемента І з'єднані з виходами другого та сьомого елементів І, входи дев'ятого елемента І з'єднані з виходом п'ятого елемента І та колектором другого транзистора, входи десятого елемента І з'єднані з виходами четвертого та п'ятого елемента І, а вихід з'єднаний з четвертою вихідною шиною, входи одинадцятого елемента І з'єднані з першою вхідною шиною та третім інвертором, входи дванадцятого елемента І з'єднані з другою та третьою вхідними шинами, входи тринадцятого елемента І з'єднані з виходами сьомого та одинадцятого елементів І, входи чотирнадцятого елемента І з'єднані з шостою вхідною шиною та виходом дванадцятого елемента І, входи п'ятнадцятого елемента І з'єднані з четвертою та шостою вхідними шинами, входи шістнадцятого елемента І з'єднані з другою та сьомою вхідними шинами, входи сімнадцятого елемента І з'єднані з виходами третього та четвертого інвертора, входи вісімнадцятого елемента І з'єднані з виходами тринадцятого та чотирнадцятого елементів І, а вихід з'єднаний з дев'ятою вихідною шиною, входи дев'ятнадцятого елемента І з'єднані з виходами дванадцятого та п'ятнадцятого елементів І, а вихід з'єднаний з третьою вихідною шиною, входи двадцятого елемента І з'єднані з виходами шостого та шістнадцятого елементів І, а вихід з'єднаний з восьмою вихідною шиною, входи двадцять першого елемента І з'єднані з виходами шостого інвертора та шостого елемента І, а вихід з'єднаний з нульовою вихідною шиною, входи двадцять другого елемента І з'єднані з виходом сімнадцятого елемента І та колектором третього транзистора, а також база першого транзистора з'єднана з третьою вхідною шиною та першим резистором, емітер першого транзистора з'єднаний з виходом першого елемента І, колектор першого транзистора з'єднаний з першою вихідною шиною та другим резистором, база другого транзистора з'єднана з базою першого транзистора та третім резистором, емітер другого транзистора з'єднаний додатнім полюсом джерела постійної напруги, колектор другого транзистора з'єднаний з четвертим резистором, база третього транзистора з'єднана з виходом сьомого елемента І та п'ятим резистором, емітер третього транзистора з'єднаний з додатнім полюсом джерела постійної напруги, колектор третього транзистора з'єднаний з шостим резистором, один із полюсів першого резистора з'єднаний з базою першого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, перший з'єднаний з колектором першого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один з полюсів третього резистора з'єднаний з базою другого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів четвертого резистора з'єднаний з колектором другого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів п'ятого резистора з'єднаний з базою третього транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів шостого резистора з'єднаний з колектором третього транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги.

Текст

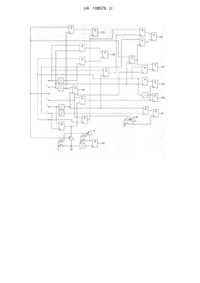

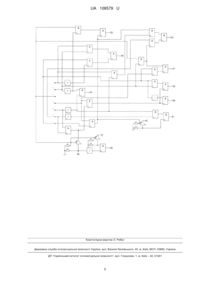

Реферат: Перетворювач коду семисегментного індикатора в двійково-десятковий код містить шість вхідних шин, чотири вихідних шини, п'ять інверторів, четвертий з яких з'єднаний з шостою вхідною шиною. Додатково в нього введено шостий інвертор, двадцять два елементи І, три транзистори, шість резисторів, сьома вхідна шина та шість вихідних шин. UA 108579 U (54) ДЕШИФРАТОР СЕМИСЕГМЕНТНОГО КОДУ В УНІТАРНИЙ UA 108579 U UA 108579 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до цифрової техніки, а саме до цифрових комбінаційних приладів, і може бути використана в індикаторних пристроях цифрових вимірювальних приладів. Відомий перетворювач двійкового коду в унітарний код (А. св. СРСР №1481896 м. кл. Н03М7/00 опубл. 23,05,89), який складається з блоків оперативної пам'яті, постійної пам'яті, тригера, першого і другого суматорів, першого-п'ятого блоків затримки, блока порівняння, дешифратора, елемента ВИКЛЮЧНЕ АБО, першого і другого елемента, елемента І-НІ, інформаційного входу, входу пуску, першого та другого тактових входів, першого та другого входів синхронізації перших та других управляючих входів, першого та другого виходів. Недоліком такого дешифратора є складність конструкції та не здатність працювати з вхідним кодом семисегментного індикатора. Найбільш близьким до пристрою, що заявляється, є перетворювач коду семисегментного індикатора в двійково-десятковий код (А. св. СРСР №1112553 м. кл. Н03К13/24, опубл. 07,09,84), який складається з шести вхідних шин, чотирьох вихідних шин, п'ятьох інверторів, чотирьох елементів ВИКЛЮЧНЕ АБО та сімох елементів 1-І lit, причому входи першого елемента ВИКЛЮЧНЕ АБО з'єднані з другою та третьою вхідними шинами, а вихід - з виходом третього інвертора, входи другого елемента ВИКЛЮЧНЕ АБО з'єднані з першою та четвертою вхідними шинами, а вихід з входом четвертого інвертора, входи третього елемента ВИКЛЮЧНЕ АБО з'єднані з виходами першого і другого інверторів, а вихід з першим входом четвертого елемента ВИКЛЮЧНЕ АБО, другий вхід якого з'єднаний з виходом третього інвертора, а вихід з четвертою вхідною шиною, крім того, входи першого елемента І-НІ з'єднані з першою і п'ятою вхідними шинами, а вихід з'єднаний з першими входами другого і третього елементів І-НІ, другі входи яких з'єднані відповідно з виходом четвертого і входом третього інверторів, а виходи відповідно з першою вихідною шиною і входом п'ятого інвертора, вихід якого з'єднаний з третьою вихідною шиною, при цьому перші входи четвертого і п'ятого елементів І-НІ з'єднані відповідно з четвертою і п'ятою вхідними шинами, їхні другі входи з'єднані з виходом першого інвертора, а виходи з'єднані з першими входами відповідно шостого і сьомого елементів І-НІ, другі входи яких з'єднані з виходами відповідно п'ятого інвертора і шостого елемента І-НІ, вихід сьомого елемента І-НІ з'єднаний з другою вихідною шиною. Недоліком прототипу є вузькі функціональні можливості, погребує інвертованого вхідного коду семисегментного індикатора. В основу корисної моделі поставлено задачу створення дешифратора семисегментного коду в унітарний, в якому за рахунок введення нових елементів та зв'язків між ними досягається можливість використання пристроїв виведення інформації, які керуються унітарним кодом, у приладах з вихідним кодом семисегментного індикатора. Це приводить до розширення функціональних можливостей пристрою. Поставлена задача вирішується за рахунок того, що в нього введено шостий інвертор, двадцять два елементи І, три транзистори, шість резисторів і сьома вхідна шина та шість вихідних шин, причому перший інвертор, вхід якого з'єднаний з першою вхідною шиною, другий інвертор, вхід якого з'єднаний з другою вхідною шиною, третій інвертор, вхід якого з'єднаний з п'ятою вхідною шиною, п'ятий інвертор, вхід якого з'єднаний з колектором першого транзистора, шостий інвертор, вхід якого з'єднаний з четвертою вхідною шиною, перший елемент І, входи якого з'єднані з п'ятою та шостою вхідними шинами, другий елемент І, входи якого з'єднані з третьою вхідною шиною та виходом другого інвертора, третій елемент І, входи якого з'єднані з виходами другого та третього інверторів, а вихід під'єднаний на п'яту вихідну шину, четвертий елемент І, входи якого з'єднані з першою та другою вхідними шинами, п'ятий елемент І, входи якого з'єднані з сьомою вхідною шиною та виходом першого інвертора, шостий елемент І, входи якого з'єднані з четвертою вхідною шиною та виходом першого елемента І, сьомий елемент І, входи якого з'єднані з четвертою та сьомою вхідними шинами, восьмий елемент І, входи якого з'єднані з виходами другого та сьомого елементів І, дев'ятий елемент І, входи якого з'єднані з виходом п'ятого елемента І та колектором другого транзистора, десятий елемент І, входи якого з'єднані з виходами четвертого та п'ятого елемента І, а вихід з'єднаний з четвертою вихідною шиною, одинадцятий елемент І, входи якого з'єднані з першою вхідною шиною та третім інвертором, дванадцятий елемент І, входи якого з'єднані з другою та третьою вхідними шинами, тринадцятий елемент І, входи якого з'єднані з виходами сьомого та одинадцятого елементів І, чотирнадцятий елемент І, входи якого з'єднані з шостою вхідною шиною та виходом дванадцятого елемента І, п'ятнадцятий елемент І, входи якого з'єднані з четвертою та шостою вхідними шинами, шістнадцятий елемент І, входи якого з'єднані з другою та сьомою вхідними шинами, сімнадцятий елемент І, входи якого з'єднані з виходами третього та четвертого інвертора, вісімнадцятий елемент І, входи якого з'єднані з виходами тринадцятого та 1 UA 108579 U 5 10 15 20 25 30 35 40 45 50 55 60 чотирнадцятого елементів І, а вихід з'єднаний з дев'ятою вихідною шиною, дев'ятнадцятий елемент І, входи якого з'єднані з виходами дванадцятого та п'ятнадцятого елементів І, а вихід з'єднаний з третьою вихідною шиною, двадцятий елемент І, входи якого з'єднані з виходами шостого та шістнадцятого елементів І, а вихід з'єднаний з восьмою вихідною шиною, двадцять перший елемент І, входи якого з'єднані з виходами шостого інвертора та шостого елемента І, а вихід з'єднаний з нульовою вихідною шиною, двадцять другий елемент І, входи якого з'єднані з виходом сімнадцятого елемента І та колектором третього транзистора, а також перший транзистор, база якого з'єднана з третьою вхідною шиною та першим резистором, емітер першого транзистора з'єднаний з виходом першого елемента І, а колектор з'єднаний з першою вихідною шиною та другим резистором, а також другий транзистор, база якого з'єднана з базою першого транзистора та третім резистором, емітер якого з'єднаний додатнім полюсом джерела постійної напруги, а колектор з'єднаний з четвертим резистором, а також третій транзистор, база якого з'єднана з виходом сьомого елемента І та п'ятим резистором, емітер якого з'єднаний з додатнім полюсом джерела постійної напруги, а колектор з'єднаний з шостим резистором, а також перший резистор, один з полюсів якого з'єднаний з базою першого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, другий резистор, один з полюсів якого з'єднаний з колектором першого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, третій резистор, один з полюсів якого з'єднаний з базою другого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, четвертий резистор, один з полюсів якого з'єднаний з колектором другого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, п'ятий резистор, один з полюсів якого з'єднаний з базою третього транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, шостий резистор, один з полюсів якого з'єднаний з колектором третього транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги. На кресленні представлено електричну принципову схему пристрою. Дешифратор семисегментного коду в унітарний містить сім вхідних шин 1-7, шість інверторів 8-13, двадцять два елементи І 14-35, три транзистори 36-38, шість резисторів 39-44, десять вихідних шин 45-54, причому вхід першого інвертора 8 з'єднаний з першою вхідною шиною 1, вхід другого інвертора 9 з'єднаний з другою вхідною шиною 2, вхід третього інвертора 10 з'єднаний з п'ятою вхідною шиною 5, вхід четвертого інвертора 11 з'єднаний з шостою вхідною шиною 6, вхід п'ятого інвертора 12 з'єднаний з колектором першого транзистора 36, вхід шостого інвертора 13 з'єднаний з четвертою вхідною шиною 4. Входи першого елемента І 14 з'єднані з п'ятою 5 та шостою 6 вхідними шинами, входи другого елемента І 15 з'єднані з третьою вхідною шиною 3 та виходом другого інвертора 9, входи третього елемента І 16 з'єднані з виходами другого 9 та третього 10 інверторів, а вихід під'єднаний на п'яту вихідну шину 49, входи четвертого елемента І 17 з'єднані з першою 1 та другою 2 вхідними шинами, входи п'ятого елемента І 18 з'єднані з сьомою вхідною шиною 7 та виходом першого інвертора 8, входи шостого елемента І 19 з'єднані з четвертою вхідною шиною 4 та виходом першого елемента І 14, входи сьомого елемента І 20 з'єднані з четвертою 4 та сьомою 7 вхідними шинами, входи восьмого елемента 1 21 з'єднані з виходами другого 15 та сьомого 20 елементів І, а вихід з'єднаний з шостою вихідною шиною 50, входи дев'ятого елемента 1 22 з'єднані з виходом п'ятого елемента І 18 та колектором другого транзистора 37, входи десятого елемента І 23 з'єднані з виходами четвертого 17 та п'ятого 18 елементів І, а вихід з'єднаний з четвертою вихідною шиною 48, входи одинадцятого елемента І 24 з'єднані з першою вхідною шиною 1 та третім інвертором 10, входи дванадцятого елемента І 25 з'єднані з другою 2 та третьою 3 вхідними шинами, входи тринадцятого елемента І 26 з'єднані з виходами сьомого 20 та одинадцятого 24 елементів І, входи чотирнадцятого елемента І 27 з'єднані з шостою вхідною шиною 6 та виходом дванадцятого елемента І 25, входи п'ятнадцятого елемента І 28 з'єднані з четвертою 4 та шостою 6 вхідними шинами, входи шістнадцятого елемента І 29 з'єднані з другою 2 та сьомою 7 вхідними шинами, входи сімнадцятого елемента І 30 з'єднані з виходами третього 10 та четвертого 11 інвертора, входи вісімнадцятого елемента І 31 з'єднані з виходами тринадцятого 26 та чотирнадцятого 27 елементів І, а вихід з'єднаний з дев'ятою вихідною шиною 53, входи дев'ятнадцятого елемента І 32 з'єднані з виходами дванадцятого 25 та п'ятнадцятого 28 елементів І, а вихід з'єднаний з третьою вихідною шиною 47, входи двадцятого елемента І 33 з'єднані з виходами шостого 19 та шістнадцятого елементів І 29, а вихід з'єднаний з восьмою вихідною шиною 52, входи двадцять першого елемента І 34 з'єднані з виходами шостого інвертора 13 та шостого елемента І 17, а вихід з'єднаний з нульовою вихідною шиною 54, входи двадцять другого елемента І 35 з'єднані з виходом сімнадцятого елемента І 30 та колектором третього транзистора 38. База першого транзистора 36 з'єднана з третьою вхідною 2 UA 108579 U 5 10 15 20 шиною 3 та першим резистором 39, емітер першого транзистора 36 з'єднаний з виходом першого елемента І 14, колектор першого транзистора 36 з'єднаний з першою вихідною шиною 1 та другим резистором 40, база другого транзистора 37 з'єднана з базою першого транзистора 36 та третім резистором 41, емітер другого транзистора 37 з'єднаний додатнім полюсом джерела постійної напруги, колектор другого транзистора 37 з'єднаний з четвертим резистором 42, база третього транзистора 38 з'єднана з виходом сьомого елемента І 20 та п'ятим резистором 43, емітер третього транзистора 38 з'єднаний з додатнім полюсом джерела постійної напруги, колектор третього транзистора 38 з'єднаний з шостим резистором 44. Один із полюсів першого резистора 39 з'єднаний з базою першого транзистора 36, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один з полюсів другого резистора 40 з'єднаний з колектором першого транзистора 36, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один з полюсів третього резистора 41 з'єднаний з базою другого транзистора 37, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів четвертого резистора 42 з'єднаний з колектором другого транзистора 37, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів п'ятого резистора 43 з'єднаний з базою третього транзистора 38, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів шостого резистора 44 з'єднаний з колектором третього 38 транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги. Пристрій працює наступним чином. Всі можливі вихідні комбінації в залежності від вхідних представлено в таблиці відповідності табл.1. Робота пристрою описана на прикладі вхідного коду, який відповідає цифрі 3. Цифр 1 2 3 4 5 6 7 8 9 0 25 30 А 1 0 1 1 0 1 1 1 1 1 1 в 2 0 1 1 1 0 0 1 1 1 1 Вхідні шини с D Е 3 4 5 0 0 1 0 1 1 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 F 6 1 0 0 1 1 1 0 1 1 1 G 7 0 1 1 1 1 1 0 1 1 0 1 45 1 0 0 0 0 0 0 0 0 0 2 46 0 1 0 0 0 0 0 0 0 0 3 47 0 0 1 0 0 0 0 0 0 0 4 48 0 0 0 1 0 0 0 0 0 0 Вихідні шини 5 6 49 50 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 7 51 0 0 0 0 0 0 1 0 0 0 8 52 0 0 0 0 0 0 0 1 0 0 9 53 0 0 0 0 0 0 0 0 1 0 0 54 0 0 0 0 0 0 0 0 0 1 Якщо на вхідних шинах 1,2,3,4 та 6, що відповідають сегментам A, B,C, D та G відповідно семисегментного індикатора, які з'єднані з входами дванадцятого 25 та п'ятнадцятого 28 елементів І, при тому на всіх інших вхідних шинах напруга відсутня, то на їх виходах, які з'єднані з входами дев'ятнадцятого елемента І 32, з'являється напруга, яка відповідає рівню логічної одиниці. Оскільки на обох входах дев'ятнадцятого елемента І присутня напруга, то на його виході, який з'єднаний з третьою вихідною шиною 3, також з'являється напруга, яка відповідає рівню логічної одиниці. На всіх інших вихідних шинах напруга відсутня. При других вхідних комбінаціях спрацьовують інші елементи за подібним принципом. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 35 40 45 Перетворювач коду семисегментного індикатора в двійково-десятковий код, що містить шість вхідних шин, чотири вихідних шини, п'ять інверторів, четвертий з яких з'єднаний з шостою вхідною шиною, який відрізняється тим, що в нього введено шостий інвертор, двадцять два елементи І, три транзистори, шість резисторів, сьома вхідна шина та шість вихідних шин, причому вхід першого інвертора з'єднаний з першою вхідною шиною, вхід другого інвертора з'єднаний з другою вхідною шиною, вхід третього інвертора з'єднаний з п'ятою вхідною шиною, вхід п'ятого інвертора з'єднаний з колектором першого транзистора, вхід шостого інвертора з'єднаний з четвертою вхідною шиною, входи першого елемента І з'єднані з п'ятою та шостою вхідними шинами, входи другого елемента І з'єднані з третьою вхідною шиною та виходом другого інвертора, входи третього елемента І з'єднані з виходами другого та третього інверторів, а вихід під'єднаний до п'ятої вихідної шини, входи четвертого елемента І з'єднані з першою та другою вхідними шинами, входи п'ятого елемента І з'єднані з сьомою вхідною шиною 3 UA 108579 U 5 10 15 20 25 30 35 та виходом першого інвертора, входи шостого елемента І з'єднані з четвертою вхідною шиною та виходом першого елемента І, входи сьомого елемента І з'єднані з четвертою та сьомою вхідними шинами, входи восьмого елемента І з'єднані з виходами другого та сьомого елементів І, входи дев'ятого елемента І з'єднані з виходом п'ятого елемента І та колектором другого транзистора, входи десятого елемента І з'єднані з виходами четвертого та п'ятого елемента І, а вихід з'єднаний з четвертою вихідною шиною, входи одинадцятого елемента І з'єднані з першою вхідною шиною та третім інвертором, входи дванадцятого елемента І з'єднані з другою та третьою вхідними шинами, входи тринадцятого елемента І з'єднані з виходами сьомого та одинадцятого елементів І, входи чотирнадцятого елемента І з'єднані з шостою вхідною шиною та виходом дванадцятого елемента І, входи п'ятнадцятого елемента І з'єднані з четвертою та шостою вхідними шинами, входи шістнадцятого елемента І з'єднані з другою та сьомою вхідними шинами, входи сімнадцятого елемента І з'єднані з виходами третього та четвертого інвертора, входи вісімнадцятого елемента І з'єднані з виходами тринадцятого та чотирнадцятого елементів І, а вихід з'єднаний з дев'ятою вихідною шиною, входи дев'ятнадцятого елемента І з'єднані з виходами дванадцятого та п'ятнадцятого елементів І, а вихід з'єднаний з третьою вихідною шиною, входи двадцятого елемента І з'єднані з виходами шостого та шістнадцятого елементів І, а вихід з'єднаний з восьмою вихідною шиною, входи двадцять першого елемента І з'єднані з виходами шостого інвертора та шостого елемента І, а вихід з'єднаний з нульовою вихідною шиною, входи двадцять другого елемента І з'єднані з виходом сімнадцятого елемента І та колектором третього транзистора, а також база першого транзистора з'єднана з третьою вхідною шиною та першим резистором, емітер першого транзистора з'єднаний з виходом першого елемента І, колектор першого транзистора з'єднаний з першою вихідною шиною та другим резистором, база другого транзистора з'єднана з базою першого транзистора та третім резистором, емітер другого транзистора з'єднаний додатнім полюсом джерела постійної напруги, колектор другого транзистора з'єднаний з четвертим резистором, база третього транзистора з'єднана з виходом сьомого елемента І та п'ятим резистором, емітер третього транзистора з'єднаний з додатнім полюсом джерела постійної напруги, колектор третього транзистора з'єднаний з шостим резистором, один із полюсів першого резистора з'єднаний з базою першого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, перший з'єднаний з колектором першого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один з полюсів третього резистора з'єднаний з базою другого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів четвертого резистора з'єднаний з колектором другого транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів п'ятого резистора з'єднаний з базою третього транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги, один із полюсів шостого резистора з'єднаний з колектором третього транзистора, а другий полюс з'єднаний з від'ємним полюсом джерела постійної напруги. 4 UA 108579 U Комп’ютерна верстка О. Рябко Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03M 13/00, H03M 7/00

Мітки: дешифратор, унітарний, семисегментного, коду

Код посилання

<a href="https://ua.patents.su/7-108579-deshifrator-semisegmentnogo-kodu-v-unitarnijj.html" target="_blank" rel="follow" title="База патентів України">Дешифратор семисегментного коду в унітарний</a>

Попередній патент: Пристрій вимірювання індукції магнітного поля

Наступний патент: Спосіб комплексного лікування обмежених форм нейродерміту

Випадковий патент: Двотактний симетричний підсилювач струму