Однорозрядний суматор

Формула / Реферат

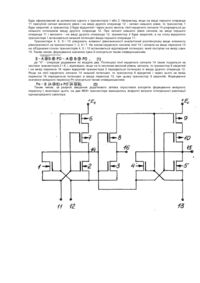

Однорозрядний суматор, який має в своєму складі п'ять МОН транзисторів n-типу і п'ять МОН транзисторів р-типу, входи першого і другого операндів, вхід переноса та виходи суми і переноса, причому витік першого транзистора n-типу з'єднаний з заслонами других транзисторів n- і р-типів, заслони перших транзисторів n-і р-типів з'єднані між собою і під'єднані до витоків другого і третього транзисторів n-типу, стоки першого транзистора n-типу і других транзисторів n- і р-типів з'єднані між собою і під'єднані до заслонів третіх і п'ятих транзисторів n- і р-типів та до витоку четвертого транзистора n-типа, витік п'ятого транзистора n-типу з'єднаний з заслонами четвертих транзисторів n- і р-типів, витоки першого і четвертого транзисторів р-типів під'єднані до шини живлення, стік першого транзистора р-типу з'єднаний з витоком другого транзистора р-типу, стік четвертого транзистора р-типу з'єднаний з витоком п'ятого транзистора р-типу, при цьому вхід першого операйда під'єднаний до витоку першого транзистора n-типу, вхід другого операнда під'єднаний до витоку другого транзистора n-типу, вхід переносу - до входу п'ятого транзистора n-типу, а стоки третіх транзисторів n- і р-типів з'єднані між собою і під'єднані до виходу переносу, стоки четвертого транзистора n-типу і п'ятих транзисторів n- і р-типів з'єднані між собою і під'єднані до виходу суми, який відрізняється тим, що витік третього транзистора р-типу з'єднаний зі входом переносу.

Текст

Винахід відноситься до обчислювальної техніки і може бути використаний для побудови обчислювальних вузлів в складі спеціалізованих ВІС на основі КМОН транзисторів. Відомий однорозрядний суматор, який має в своєму складі вісім МОН транзисторів n-типу і шість МОН транзисторів р-типу [Авт. св СРСР № 1439578 кл G 06 F 7/50. 1988]. Реалізація даного однорозрядного суматора на МОН транзисторах вимагає значних апаратних витрат Найбільш близьким до пропонованого є відомий однорозрядний суматор, який має в своєму складі п'ять МОН транзисторів n-типу і п'ять МОН транзисторів р-типу. входи першого і др угого операндів, вхід переноса та виходи суми і переноса, причому витік першого транзистора n-типу з'єднаний з заслонами других транзисторів n- і р-типів, заслони перших транзисторів n- і р-типів з'єднані між собою і під'єднані до витоків другого і третього транзисторів n-типу, стоки першого транзистора n-типу і других транзисторів n- і р-типів з'єднані між собою і під'єднані до заслонів третіх і п'ятих транзисторів n- і р-типів та до витоку че твертого транзистора nтипа, витік п'ятого транзистора n-типу з'єднаний з заслонами четвертих транзисторів n- і р-типів, витоки першого і четвертого транзисторів р-типів під'єднані до шини живлення, стік першого транзистора р-типу з'єднаний з витоком другого транзистора р-типу, стік четвертого транзистора р-типу з'єднаний з витоком п'ятого транзистора р-типу, при цьому вхід першого операнда під'єднаний до витоку першого транзистора nтипу, вхід другого операнда - до витоку другого транзистора n-типу, вхід переносу - до входу п'ятого транзистора n-типу, а стоки третіх транзисторів n- і р-типів з'єднані між собою і під'єднані до виходу переносу, стоки четвертого транзистора n-типу і п'ятих транзисторів n- і р-типів з'єднані між собою і під'єднані до виходу суми [Авт. св. №1509874, кл. G 06 F 7/50, 1989]. Додатково у складі відомого однорозрядного суматора для формування вихідного переносу використані один транзистор n-типу, один транзистор р-типу і один резистор. Для виготовлення в складі ВІС резистора необхідно виконати додаткові технологічні операції. А також, якщо на вході переноса присутній сигнал низького рівня, а на входах операндів встановлені сигнали різних рівнів, то на виході переноса формується сигнал логічного нуля, рівний падінню напруги на резисторі, що знижує надійність і завадостійкість вузлів ВІС в цілому. Таким чином інтегральна реалізація відомого однорозрядного суматора вимагає шість МОН транзисторів n-типу, шість транзисторів р-типу і одного резистора. В основу винаходу поставлене завдання створити однорозрядний суматор, в якому нові взаємозв'язки дозволили б спростити формування вихідного переноса і, за рахунок цього, зменшити апаратні витрати Інтегральної реалізації приладу. Поставлене завдання досягається за рахунок того, що однорозрядний суматор, який має в своєму складі п'ять МОН транзисторів n-типу і п'ять МОН транзисторів р-типу, входи першого і другого операндів, вхід переноса та виходи суми і переноса, причому витік першого транзистооа n-типу з'єднаний з заслонами других транзисторів n- і р-типів, заслони перших транзисторів n- і р-типів з'єднані між собою і під'єднані до витоків другого і третього транзисторів n-типу, стоки першого транзистора n-типу і други х транзисторів n- і р-типів з'єднані між собою і під'єднані до заслонів третіх і п'яти х транзисторів n- і р-типів та до витоку четвертого транзистора n-типа, витік п'ятого транзистора n-типу з'єднаний з заслонами четвертих транзисторів n- і ртипів, витоки першого і четвертого транзисторів р-типів під'єднані до шини живлення, стік першого транзистора р-типу з'єднаний з витоком другого транзистора р-типу, стік четвертого транзистора р-типу з'єднаний з витоком п'ятого транзистора р-типу, при цьому вхід першого операнда під'єднаний до витоку першого транзистора n-типу, вхід другого операнда - до витоку другого транзистора n-типу, вхід переносу - до входу п'ятого транзистора n-типу, а стоки третіх транзисторів n- і р-типів з'єднані між собою і під'єднані до виходу переносу, стоки четвертого транзистора n-типу і п'ятих транзисторів n- і р-типів з'єднані між собою і під'єднані до виходу суми, згідно винаходу, відрізняється тим, що витік третього транзистора р-типа з'єднаний зі входом переносу. Введення нового зв'язка зменшило апаратні витрати інтегральної реалізації однорозрядного суматора на два МОН транзистори і один резистор, в порівнянні з відомим пристроєм, за рахунок спрощення алгоритму формування значення вихідного переносу: якщо рівні вхідних операндів однакові, то значення вихідного переносу співпадає зі значенням одного з операндів, в Ін шому випадку, вихідний перенос рівний вхідному. На кресленні представлена принципова електрична схема запропонованого однорозрядного суматора. Однорозрядний суматор складається з п'яти МОН транзисторів n-типу 1...5 і п'яти МОН транзисторів ртипу 6...10, входів операндів 11, 12 та переносу 13, виходів суми 15 та переносу 16, причому стоки транзисторів 1, 2, 7 за допомогою лінії керуючого сигнала 14 з'єднані з заслонами транзисторів 3, 5, 8, 10 і з витоком транзистора 4, витік транзистора 7 під'єднаний до стоку транзистора 6, витік транзистора 10 під'єднаний до стоку транзистора 9, а витоки транзисторів 6 і 9 - до шини живлення, при цьому вхід першого операнда 11 під'єднаний до об'єднаних витоку транзистора 1 і заслонів транзисторів 2 та 7, вхід другого операнда 12 під'єднаний до об'єднаних витоків транзисторів 2 і 3 та заслонів транзисторів 1 та 6, вхід переносу 13 під'єднаний до об'єднаних витоків транзисторів 5, 8 та заслонів транзисторів 4 і 9, вихід суми 15 з'єднаний з об'єднаними стоками транзисторів 4, 5 і 10, вихід переноса 16 з'єднаний з об'єднаними стоками транзисторів 3 і 8. Транзистори 1, 2, 6 і 7 складають елемент рівнозначності, тобто, якщо на входи операндів 11 і 12 подано однакові рівні сигналів, то на лінії керуючого сигнала 14 встановиться високий рівень. Наприклад, якщо на входа х операндів 11 і 12 присутні сигнали низьких рівнів і, відповідно, на заслонах транзисторів 1, 2, 6 і 7 тоже, то транзистори 1 і 2 закриються, а транзистори 6, 7 відкриються і на лінію керуючого сигнала 14 поступить високий потенціал шини живлення. Якщо на входах операндів 11 і 12 будуть сигнали високого рівня, то транзистори 6 і 7 закриються. В такому випадку, на лінію керуючого сигнала 14 поступить високий потенціал зі входів операндів 11 і 12 через відкриті транзистори 112. Якщо на входах операндів 11 і 12 присутні сигнали різних рівнів, то на лінії керуючого сигнала 14 встановиться низький потенціал. Тобто, в такому випадку, один з транзисторів 6 або 7 буде закритий і високий потенціал шини живлення не поступить на стік транзистора 7. Низький потенціал на лінії керуючого сигнала 14 буде зформований за допомогою одного з транзисторів 1 або 2. Наприклад, якщо на вході першого операнда 11 присутній сигнал високого рівня і на вході другого операнда 12 - сигнал низького рівня, то транзистор 1 буде закритий, а транзистор 2 буде відкритий і через нього ємність лінії керуючого сигнала 14 розрядиться до низького потенціала входу другого операнда 12. При сигналі низького рівня сигнала на вході першого операнда 11 і високого - на вході др угого операнда 12, транзистор 2 буде закритий, а на стоку відкритого транзистора 1 встановиться низький потенціал входа першого операнда 11. Транзистори 4, 5, 9 і 10 утворюють елемент рівнозначності аналогічний розглянутому вище елементу рівнозначності на транзисторах 1, 2, 6 і 7. На основі керуючого сигнала лінії 14 і сигнала на вході переноса 13 на об'єднаних стоках транзисторів 4, 5 і 10 встановиться відповідний потенціал, який поступає на вихід суми 15. Таким чином, формування значення суми S описується таким співвідношенням де "Å" - операція додавання по модулю два. Потенціал лінії керуючого сигнала 14 також подається на заслони транзисторів 3 і 8, і, відповідно, якщо на їх заслонах високий рівень сигнала, то транзистор 8 закритий і на вихід переноса 16 через відкритий транзистора 3 передається потенціал зі входа другого операнда 12. Якщо на лінії керуючого сигнала 14 низький потенціал, то транзистор 8 відкритий і через нього на вихід переноса 16 передається потенціал зі входа переноса 13, при цьому транзистор З закритий. Формування значення вихідного переноса Рn описується таким співвідношенням Таким чином, за рахунок введення додаткового зв'язка спростився алгоритм формування вихідного переносу І, внаслідок цього, на два МОН транзистори зменшились апаратні витрати інтегральної реалізації однорозрядного суматора.

ДивитисяДодаткова інформація

Назва патенту англійськоюSingle-digit adder

Автори англійськоюPankov Ruslan Stepanovych

Назва патенту російськоюОдноразрядный сумматор

Автори російськоюПаньков Руслан Степанович

МПК / Мітки

МПК: G06F 7/48, G06F 7/503

Мітки: однорозрядний, суматор

Код посилання

<a href="https://ua.patents.su/2-23108-odnorozryadnijj-sumator.html" target="_blank" rel="follow" title="База патентів України">Однорозрядний суматор</a>

Наступний патент: Спосіб одержання елагової кислоти

Випадковий патент: Спосіб хірургічного лікування первинної глаукоми