Спосіб термострумового тренування інтегральної схеми

Номер патенту: 3923

Опубліковано: 27.12.1994

Формула / Реферат

1. Способ термотоковой тренировки интегральной схемы, включающий нагрев интегральной схемы и подачу на нее переменного напряжения, отличающийся тем что нагрев интегральной схемы осуществляют на пластине после формирования на неї структуры металлизации при температуре 85-2500С, а переменное напряжение выбирают синусоидальное или импульсное, которое прикладывают между металлизацией на пластине и подложкой интегральное схемы.

2. Способ по п. 1, отличающийся тем, что пластины собирают в пакете размещенными между ними электродами прокладками из токопроводящей резины.

Текст

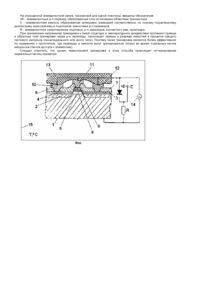

Изобретение относится к области микроэлектроники и может быть использовано в технологии полупроводниковых приборов и интегральных схем для отбраковки потенциально-ненадежных изделий. Известен способ электротермотренировки интегральных схем [1], в котором входы ИС через ограничивающие резисторы подключают к генератору псевдослучайного кода-сигнала, выводы питания через контакты коммутатора подключают к половине напряжения питания. Тактовая частота следования импульсов выбирается высокой (1 МГц). Коммутатор подключает все выводы ИС к генератору псевдослучайного кода к блоку питания с частотой 1-50 Гц. Тренировка выходных каскадов обеспечивается подключением к выходам ИС половинного напряжения питания. Таким образом, по этому способу напряжение тренировки - от генератора псевдослучайного кода и напряжение питания -подают на выводы ИС. Если считать эти напряжения переменными, то можна заключить, что от внешних выводов, вдоль поверхности кристалла микросхемы в корпусе прикладывается импульснопеременное напряжение, которое обеспечивает ее тренировку. Этот способ является трудоемким, дорогостоящим, направлен на отбраковку уже готовых изделий; кроме того, он не является достаточно эффективным, так как температура тренировки ограничена типом применяемого корпуса микросхем, например, для пластмассовых корпусов она составляет 85-1250С; не обеспечивается эффективная электрическая тренировка полностью всех элементов ИС из-за невозможности подачи на них сигналов от внешних источников, что обусловлено логикой функционирования ИС или же требуется разработка специальных тестовы х последовательностей подачи сигналов. В качестве прототипа выбран способ геармотоковой тренировки микросхем, герметизированных пластмассой [2], например, для микросхем, изготовленных по n-МОП и k-МОП-те хнологии, при температуре, не превышающей 850С и позволяет не только выявлять ранние отказы, но и уменьшать интенсивность отказов при дальнейшей эксплуатации. Отмечается сильная зависимость интенсивности отказов микросхем при термотоковой тренировке от процесса старения герметизируемой пластмассы. Поэтому для значений энергии активации 0,7-1,0 эВ, характерных для процессов, происходящих в интегральных схемах, изготовляемых в пластмассовых корпусах, проведение электротермотоковой тренировки при температуре окружающей среды выше 85 0 недопустимо из-за возможности образования дефектов. К числу указанных процессов относятся электромиграция, зарядовая инжекция, образование поверхностного заряда, дрейф порогового напряжения, взаимодействие алюминия и золота в термокомпрессионных соединениях, поверхностная инверсия, обусловленная поверхностными загрязнениями. Таким образом, данный метод термотоковой тренировки выше +850С не эффективен и вызывает деградацию электропараметров микросхем, кроме того, дорогостоящий и малоинформативен. В основу изобретения поставлена задача усовершенствования способа термотоковой тренировки интегральной схемы путем изменения параметров ее нагрева и направления приложения переменноимпульсного напряжения, что улучшает электропараметры микросхемы и, тем самым, повышает эффективность способа и снижает затраты на электротермотренировку. Поставленная задача решается тем, что в способе термотоковой тренировки интегральной схемы, включающем нагрев интегральной схемы и подачу на нее переменного напряжения, согласно изобретению нагрев интегральной схемы осуществляют на пластине после формирования на ней структур с металлизацией при температуре 85-2500С, а переменное напряжение выбирают синусоидальное или импульсное, которое прикаладывают между металлизацией на пластине и подложкой интегральной схемы. Кроме того пластины собирают в пакет с размещенными между ними электродами-прокладками из токопроводящей резины. В предложенном способе термотоковой тренировки структур (кристаллов) ИС на пластине, в котором переменно-импульсное напряжение прикладывается между поверхностью металлизации cтруктур и подложкой. Прикладываемое таким образом напряжение необходимо для тренировки элементов ИС за счет прохождения токов от поверхности металлизации через p-n переходы и емкости структур к подложке. Несмотря на то, что вся поверхность металлизации пластины находится под одним потенциалом (переменным) тренировка структур происходит, и весьма эффективны за счет прохождения токов между каждым элементом даже не на уровне транзисторов (а на уровне их составляющих элементов, например, для МОП ИС - стоков, истоков, затворов) и подложкой. Эффективности тренировки способствуют возможность повышения температуры до 2500С, что невозможно применять для собранных микросхем из-за потери работоспособности кремниевых стр уктур при таких температурах, и тем, что таких температур в большинстве случаев не выдерживают корпусные детали (например, пластмассовые, клеи) и подключающая оснастка. Известно, что в кристалле любой ИС, каждый ее элемент прямо, через контакт к изоляции, или косвенно, т.е. через другие элементы, подключен к металлизации - разводке и контактным площадкам. Поэтому приложение через токопроводящую прокладку напряжения к поверхности пластины обеспечивает подключение к нему прямо или косвенно всех без исключения элементов структур на пластине, а при подключении второго электрода к подложке -прохождение тока тренировки. В качестве примера можно рассмотреть n-канальную МОП ИС со структурой кремний-на-изоляторе с упрощенной эквивалентной электрической схемой тренировки, показанной на чертеже. ИС содержит подложку p-типа 1, например КДБ-80, в которой сформированы участки утопленного локального окисла 2. На такую пластину нанесена методом LPCVD поликремниевая пленка толщиной 0,5 мкм, проведена ее лазерная рекристаллизация и далее извеастными методами по самосовмещенной поликремниевой технологии в нее сформированы: истоковая область транзистора 3, стоковая - 4, подканальная - 5, Сток-истоковые n-области расположены над участком локального окисла, подканальная p-область - над затравкой, т.е. подложкой и имеет с ней оммический контакт, является продолжением кристаллографической структуры подложки. Над стокистоковыми областями 3, 4 и поликремниевым затвором 9, сформированы участки межслойного диэлектрика из окисла кремния 6, под поликремниевыми затвором 9 - тонкий подзатворный окисел 8. Области стока, истока и затвора через контактные окна в межслойном окисле 7 подключены соответственно к алюминиевым электродам 10, 12, 11. Между алюминиевыми электродами 10, 11, 12 через токопроводящую прокладку 13 и подложкой 1 подается переменное напряжение от генератора 14. Вся структура помещена в камеру тепла 15 с температурой ТС. На упрощенной эквивалентной схеме, показанной для одной пластины, введены обозначения VD - эквивалентный р-n переход, образованный сток-истоковыми областями транзистора С - эквивалентная емкость образованная затворами, разводкой соответственно по тонкому подзатворному диэлектрику, межслойному и подложкой; емкостями р-n переходов; R - эквивалентное сопротивление подложки, р-n переходов, контактов к ним, прокладки. При приложении напряжения тренировки к такой структуре и температурного воздействия протекают прямые и обратные токи тренировки через р-n переходы, происходят заряды и разряды емкостей в процессе каждого тактового импульса (синусоидального или иного типа). Поэтому такая тренировка является более эффективной по сравнению с прототипом, где переходы и емкости могут тренироваться только во время отдельных тактов импульсов (тактов доступа к элементам). Следует отметить, что кроме термотоковой тренировки в этом способа происходит геттерирование заряженных частиц примесей.

ДивитисяДодаткова інформація

Назва патенту англійськоюBurn-in method for integrated circuitry

Автори англійськоюKohut Ihor Tymofiiovych, Novosiadlyi Stepan Petrovych

Назва патенту російськоюСпособ термотоковой тренировки интегральной схемы

Автори російськоюКогут Игорь Тимофеевич, Новосядлый Степан Петрович

МПК / Мітки

МПК: H01L 21/70

Мітки: термострумового, схемі, тренування, інтегральної, спосіб

Код посилання

<a href="https://ua.patents.su/2-3923-sposib-termostrumovogo-trenuvannya-integralno-skhemi.html" target="_blank" rel="follow" title="База патентів України">Спосіб термострумового тренування інтегральної схеми</a>

Попередній патент: Спосіб лікування коніотуберкульозу

Наступний патент: Радіолокаційний пристрій для визначення дальності та швидкості цілі

Випадковий патент: Пристрій для об'єднання декількох потоків штучних виробів