Вузол формування переносу

Формула / Реферат

Вузол формування переносу, який має у своєму складі три МОН транзистори р-типу, три МОН транзистори n-типу, входи першого та. другого операндів, вхід І вихід переносу, причому стоки перших МОН транзисторів р-1 n-типу з'єднані з витоками других МОН транзисторів р-1 n-типу, витік першого МОН транзистора р-типу під'єднаний до шини живлення, витік першого МОН транзистора n-типу - до загальної шини, об'єднані заслони других МОН транзисторів р- І η-типу одночасно є входом переносу, стоки других І третіх МОН транзисторів р-1 n-типу з'єднані між собою і одночасно є виходом переносу, який відрізняється тим, що додатково містить два МОН транзистора р-типу І два МОН транзистора η-типу, причому стоки четвертих МОН транзисторів р-1 n-типу з'єднані з витоками других МОН транзисторів р- І n-типу, стоки п'ятих МОН транзисторів р-1 n-типу з'єднані з витоками третіх МОН транзисторів р- і n-типу, витоки четвертого 1 п'ятого МОН транзисторів р-типу під'єднані до шини живлення, витоки четвертого І п'ятого МОН транзисторів n-типу до загальної шини, заслони четвертих І п'ятих МОН транзисторів р-1 n-типу з'єднані між собою і одночасно є входом першого операнда, заслони перших І третіх МОН транзисторів р- і n-типу з'єднані між собою І одночасно є входом другого операнда.

Текст

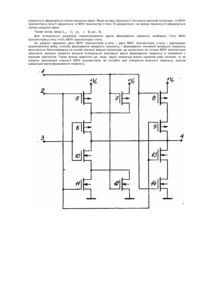

Винахід відноситься до обчислювальної техніки і може бути використаний при Інтегральній реалізації багаторозрядних суматорів з послідовним розповсюдженням переносу. Відомий вузол формування переносу, який містить логічний елемент 2I—НІ, логічний елемент 2АБО-НІ, три Інвертори, МОН транзистор р-типа, МОН транзистор n-типа, входи першого І другого операндів та вхід І вихід переносу [Авт.св. СРСР № 1291969, кл. G 06 F 7/50, опублік 1987]. Інтегральна реалізація -відомого вузла формування переносу вимагає значних апаратних витрат. Найбільш близьким до пропонованого є вузол формування переносу, який має у своєму складі три МОН транзистори р-типу, три МОН транзистори n-типу, входи першого та др угого операндів, вхід І ви хід переносу, причому стоки перших МОН транзисторів р-1 n-типу з'єднані з витоками других МОН транзисторів р-1 n-типу, витік першого МОН транзистора р-типу під'єднаний до шини живлення, витік першого МОН транзистора nтипу - до загальної шини, об'єднані заслони других МОН транзисторів р- і n-типу одночасно є входом переносу, стоки других І третіх МОН транзисторів р-1 n-типу з'єднані між собою і одночасно є виходом переносу [Авт.св. СРСР № 1363189, кл. G 06 F 7/50, опублік. 1987]. Для вибору способу формування вихідного переносу (передача вхідного переносу або генерація власного переносу) 1 утворення значення вихідного переносу відомий вузол формування переносу додатково містить логічні елементи 2І-НІІ 2АБО-НІ, Загальні апаратні витрати інтегральної реалізації відомого вузла формування переносу становлять 14 КМОН транзисторів. В основу винаходу поставлене завдання створити вузол формування переносу, в якому нові елементи і відповідні взаємозв'язки дозволили б відмовитись від використання допоміжних логічних елементів 1 формувати значення вихідного переносу безпосередньо на основі значень вхідних операндів і, відповідно, за рахунок цього, зменшити загальні апаратні витрати інтегральної реалізації повного однорозрядного суматора. Поставлене завдання досягається за рахунок того, що вузол формування переносу, який має у своєму складі три МОН транзистори р-типу, три МОН транзистори n-типу, входи першого та другого операндів, вхід і вихід переносу, причому стоки перших МОН транзисторів р-1 n-типу з'єднані з витоками других МОН транзисторів р-1 n-типу, витік першого МОН транзистора р-типу під'єднаний до шини живлення, витік першого МОН транзистора n-типу - до загальної шини, об'єднані заслони других МОН транзисторів р- І n-типу одночасно є входом переносу, стоки других і третіх МОН транзисторів р-1 n-типу з'єднані між собою і одночасно є виходом переносу, згідно з винаходом, додатково містить два МОН транзистори р-типу і два МОН транзистори n-типу, причому стоки четвертих МОН транзисторів р-1 n-типу з'єднані з витоками других МОН транзисторів р-1 n-типу, стоки п'ятих МОН транзисторів р- і n-типу з'єднані з витоками третіх МОН транзисторів р- І n-типу, ви токи четвертого і п'ятого МОН транзисторів р-типу під'єднані до шини живлення, витоки четвертого І п'ятого МОН транзисторів n-типу - до загальної шини, заслони четвертих і п'яти х МОН транзисторів р- І n-типу з'єднані між собою І одночасно є входом першого операнда, заслони перших І третіх МОН транзисторів р-I n-типу з'єднані між собою і одночасно є входом другого операнду. Введення двох МОЙ транзисторів р-типу, двох МОН транзисторів n-типу І відповідних взаємозв'язків зменшило загальні апаратні витрати Інтегральної реалізації вузла формування переносу, за рахунок вилучення генерації проміжних функцій і утворення значення вихідного переносу безпосередньо на основі значень вхідних операндів. На кресленні представлена принципова схема вузла формування переносу. Вузол формування переносу має в своєму складі входи першого 1 і другого 2 операндів, вхід З та вихід 4 переносу, МОН транзистори ртипу 5, 6, 7, 8 І 9, МОЙ транзистори n-гипу 10, 11, 12, 13 І 14, причому витік МОН транзистора р-типу 5 під'єднаний до стоків МОН транзисторів р-типу 6 і 7, стік МОН транзистора р-типу 7 з'єднаний з витоком МОН транзистора р-типу 8, витік МОН транзистора n-типу 10 під'єднаний до стоків МОН транзисторів n-типу Ці 12, витік МОН транзистора n-типу 13 з'єднаний зі стоком МОН транзистора n-типу 14, заслони МОН транзисторів р-типу 7 і 8, n-типу 12 І 14 об'єднані між собою і одночасно є входом першого операнда 1, заслони МОН транзисторів р-типу 6 і 9, n-типу 11 і 13 об'єднані між собою і одночасно є входом другого операнда 2, об'єднані заслони МОН транзисторів р-типу 5 і n-типу 10 одночасно є входом переносу 3, стоки МОН транзисторів р-типу 5 і 9, n-тип у 10 І 13 об'єднані між собою І одночасно є виходом переносу 4, витоки МОН транзисторів р-типу 6, 7· І 8 під'єднані до шини живлення, витоки МОН транзисторів n-типу 11, 12 і 14 під'єднані до загальної шини. Якщо на входах операндів 1 і 2 присутні однакові сигнали низького рівня, високий потенціал шини живлення через відкриті МОН транзистори 8 І 9 поступить на вихід переносу 4, при цьому МОЙ транзистори nтипу 13114 будуть закриті. У випадку, якщо на вхід переносу 3 поступить низький потенціал, то через відкриті МОН транзистори р-типу 5, 6 і 7 на вихід переносу 4 також буде переданий високий потенціал. При цьому, якщо на вхід переноса 3 поступить високий потенціал, який відкриває МОН транзистор n-типу 10, то закриті МОН транзистори n-типу 11 І 12 заборонять передачу низького потенціалу загальної шини. Якщо на входи операндів 1 І 2 поступлять однакові сигнали високого рівня, то на вихід переносу 4 через відкриті МОН транзистори n-типу 13 і 14 буде переданий низький потенціал загальної шини, при цьому МОН транзистори р-типу 8 І 9 будуть закриті, Причому, якщо на вхід переноса З поступить низький потенціал, який відкриває МОН транзистор р-типу 5, то закриті МОН транзистори р-типу заборонять передачу високого рівня шини живлення. У випадку, якщо на вхід переносу З поступить високий потенціал, то через відкриті МОН транзистори n-типу 10, 11 112 на вихід переносу 4 також буде переданий низький потенціал загальної шини. Якщо на входах операндів 1 і 2 присутні сигнали різних рівнів, то один з пари МОН транзисторів р-типу 8 і 9 або n-типу 13 і 14, які з'єднані послідовно, буде відкритий , а другий - закритий І тому передача на вихід переносу 4, відповідно, високого потенціалу шини живлення або низького потенціалу загально! шини буде заборонена. В такому випадку, один з пари МОН транзисторів р-типу 6 і 7, які з'єднані паралельно, буде відкритий І передасть на витік МОН транзистора р-типу 5 високий потенціал шини живлення. Аналогічно, один з пари МОН транзисторів n-типу 11 і 12, які з'єднані паралельно, також буде відкритий і передасть на витік МОН транзистора n-типу 10 низький потенціал загальної шини. При цьому, якщо на вхід переносу 3 поступить низький потенціал, який відкриє МОН транзистор р-типу 5 і закриє МОН транзистор n-типу 10, то на виході переносу 4 зформується сигнал високого рівня. Якщо на вхід переносу 3 поступить високий потенціал, то МОН транзистор р-типу 5 закриється, а МОН транзистор n-типу 10 відкриється і на виході переносу 4 зформується сигнал низького рівня. Таким чином, вихід Ci +1 - Ci × ( A i v B i )vA i × B i Для Інтегральної реалізації запропонованого вузла формування переносу необхідно п'ять МОН транзисторів р-типу і п'ять МОН транзисторів n-типу. За рахунок введення двох МОН транзисторів р-типу І двох МОН транзисторів n-типу і відповідних взаємозв'язків вибір способу формування вихідного переносу І формування значення вихідного переносу виконується безпосередньо на основі значень вхідних операндів, що дозволило на чотири МОН транзистори зменшити загальні апаратні витрати інтегральної реалізації вузла формування переносу в порівнянні з відомим пристроєм. Також можна відмітити що, якщо .вхідні операнди мають однакові рівні сигнали, то за рахунок зменшення кількості МОН транзисторів, які потрібні для утворення власного переносу, зросла швидкодія вузла формування переносу.

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for generating a carry signal

Автори англійськоюPankov Ruslan Stepanovych

Назва патенту російськоюУстройство для формирования сигнала переноса

Автори російськоюПаньков Руслан Степанович

МПК / Мітки

МПК: G06F 7/503, G06F 7/48

Мітки: вузол, формування, переносу

Код посилання

<a href="https://ua.patents.su/2-23899-vuzol-formuvannya-perenosu.html" target="_blank" rel="follow" title="База патентів України">Вузол формування переносу</a>

Попередній патент: Мастильна композиція для пересування виробів із сталей та сплавів

Наступний патент: Жалюзійно-вихровий пиловловлювач

Випадковий патент: Лінія для виробництва ігристого вина