Прилад для тестування напівпровідникової пам’яті

Номер патенту: 40675

Опубліковано: 27.04.2009

Автори: Андрієнко Володимир Олександрович, Рябцев Володимир Григорович, Уткіна Тетяна Юріївна

Формула / Реферат

Прилад для тестування напівпровідникової пам'яті, який містить змінне джерело електроживлення, блок зв'язку з персональним комп'ютером, блок керування та індикації, входи/виходи яких через шину зв'язку з'єднані з першими входами/виходами интерфейсного блока, другі входи/виходи якого з'єднані з входами/виходами генератора тактових імпульсів, а треті входи/виходи інтерфейсного блока з'єднані з входами/виходами формувача синхросигналів, виходи якого підключені до перших входів адаптера зв'язку з пристроєм, що тестується, входи/виходи адаптера є входами/виходами пристрою та підключаються до входів/виходів пристрою, що тестується, який відрізняється тим, що в нього додатково введені лічильник адреси мікрокоманд, постійний запам'ятовуючий пристрій (ПЗП) мікрокоманд, блок формування адреси, блок формування кодів операцій, лічильник (11), лічильник (12), формувач кодів функцій Уолша, блок формування даних і блок порівняння даних, причому виходи лічильника адреси мікрокоманд з'єднані з входами ПЗП мікрокоманд і першими входами інтерфейсного блока, виходи ПЗП з'єднані з першими входами лічильника адреси мікрокоманд, блока формування кодів операцій, лічильника (11), лічильника (12), блока формування адреси, блока формування даних і блока порівняння даних, виходи блока формування кодів операцій з'єднані з другими входами адаптера зв'язку, перші виходи блока формування адреси і виходи блока формування даних з'єднані з третіми й четвертими виходами адаптера зв'язку відповідно, виходи якого з'єднані з другими входами блока порівняння даних, треті входи якого з'єднані з виходами блока формування даних, вихід генератора тактових імпульсів з'єднаний з входами лічильника адреси мікрокоманд, блока формування кодів операцій, лічильника (11), лічильника (12), блока формування даних і блока порівняння даних, перші виходи лічильника (11), лічильника (12), блока формування адреси і блока порівняння даних з'єднані з другими входами лічильника адреси мікрокоманд, треті входи якого з'єднані з четвертими виходами інтерфейсного блока, виходи якого з'єднані з четвертими входами блока порівняння даних, треті виходи блока формування адреси з'єднані з третіми входами формувача функцій Уолша, виходи якого з'єднані з третіми входами блока формування даних, а другі виходи лічильників (11) і (12) з'єднані з першими і другими входами формувача функцій Уолша відповідно.

Текст

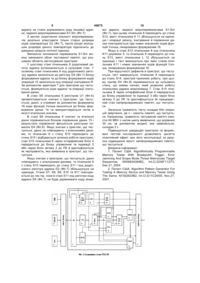

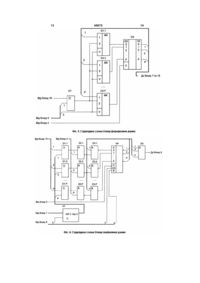

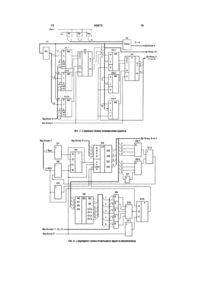

Прилад для тестування напівпровідникової пам'яті, який містить змінне джерело електроживлення, блок зв'язку з персональним комп'ютером, блок керування та індикації, входи/виходи яких через шину зв'язку з'єднані з першими входами/виходами интерфейсного блока, другі входи/виходи якого з'єднані з входами/виходами генератора тактових імпульсів, а треті входи/виходи інтерфейсного блока з'єднані з входами/виходами формувача синхросигналів, виходи якого підключені до перших входів адаптера зв'язку з пристроєм, що тестується, входи/виходи адаптера є входами/виходами пристрою та підключаються до входів/виходів пристрою, що тестується, який відрізняється тим, що в нього додатково введені лічильник адреси мікрокоманд, постійний запам'ятовуючий пристрій (ПЗП) мікрокоманд, блок формування адреси, блок формування кодів операцій, лічильник (11), лічильник (12), формувач кодів функцій Уолша, блок формування даних і блок порівняння даних, причому виходи лічильника адреси U 2 40675 1 3 40675 4 рних відмов запам'ятовуючих пристроїв, що тесвходами формувача кодів функцій Уолша відповітуються. дно. Мета корисної моделі - підвищення достовірВ основу зображення приладу поставлена заності результатів тестування напівпровідникової дача підвищення достовірності результатів теступаняті за рахунок виконання тесту, який забезпевання напівпровідникової пам'яті шляхом викорисчує отримання всіх можливих комбінацій кодів датання запропонованого рішення, ознаки якого них, які зберігаються в суміжних комірках та отовказані в частині формули зображення, яка відрізчують базові комірки, що приведе до виявлення няється від аналогу і виявляє в процесі взаємодії відмов, викликаних взаємним впливом запам'ятохарактерні особливості, які дають позитивний вуючих комірок, при цьому зменшується трудоємефект. ність синтезу програми тесту шляхом використанТаким чином, запропоноване рішення задовоня апаратно мікропрограмного способу льняє критерію «суттєвої відмінності». формування тесту, який поєднує високу швидкоНа Фіг.1 наведена структурна схема пристрою дію з невеликими апаратними затратами. для тестування напівпровідникової пам'яті. Вказана мета досягається тим, що в прилад На Фіг.2 зображена структурна схема формудля тестування напівпровідникової пам'яті, який вача кодів функцій Уолша. містить змінне джерело електроживлення, блок На Фіг.3 наведена структурна схема лічильнизв'язку з ПК, блок управління та індикації, вхоків К і L. ди/виходи яких через шину зв'язку з'єднані з перНа Фіг.4 зображена структурна схема блоку шими входами/виходами інтерфейсного блоку, формування кодів операцій. другі входи/виходи якого з'єднані з входаНа Фіг.5 наведена структурна схема блоку фоми/виходами генератора тактових імпульсів, а рмування даних. треті входи/виходи інтерфейсного блоку з'єднані з На Фіг.6 зображена структурна схема блоку входами/виходами формувача синхросигналів, порівняння даних. виходи якого підключені до перших входів адаптеНа Фіг.7 наведена структурна схема блоку фора зв'язку з пристроєм, що тестується, вхормування адреси. ди/виходи адаптера є входами/виходами приладу На Фіг.8 зображена структурна схема лічильй підключаються до входів/виходів напівпровідниника адреси мікрокоманд. кової пам'яті, що тестується, додатково введений На Фіг.9 наведений алгоритм роботи приладу лічильник мікрокоманд, постійний запам'ятовуюдля тестової діагностики напівпровідникової пам'ячий пристрій мікрокоманд, блок формування адреті. си, блок формування кодів операцій, лічильник К, На Фіг.1 наведена структурна схема пристрою лічильник L, формувач кодів функцій Уолша, блок для тестування напівпровідникової пам'яті, яка формування даних та блок порівняння даних, до містить змінне джерело електроживлення 1, блок того ж виходи лічильника адреси микрокоманд зв'язку з ПК 2, блок управління та індикації 3, вхоз'єднані з виходами ПЗП мікрокоманд і входами ди/виходи яких через шину зв'язку з'єднані з перінтерфейсного блоку, виходи ПЗП мікрокоманд шими входами/виходами інтерфейсного блоку 4, з'єднані з першими входами лічильника адреси другі входи/виходи якого з'єднані входамікрокоманд, блоку формування кодів операцій, ми/виходами генератора тактових імпульсів 5, а лічильника К, лічильника L, блоку формування треті входи/виходи інтерфейсного блоку з'єднані в адреси, блоку формування даних і блоку поріввходами/виходами формувача синхросигналів 6, няння даних, виходи блоку формування кодів опевиходи якого підключені до перших входів адаптерацій з'єднані з другими входами адаптера зв'язку ра зв'язку 7, входи/виходи адаптера є входаз пристроєм, що тестується, перші виходи блоку ми/виходами приладу, виходи лічильника адреси формування адреси і виходи блоку формування мікрокоманд 8 з'єднані з входами ПЗП мікрокоданих з'єднані з третіми та четвертими входами манд 9 і входами інтерфейсного блоку 4, виходи адаптера зв'язку відповідно, виходи якого з'єднані ПЗП 9 з'єднані з першим входами лічильника адз другими входами блоку порівняння даних, треті реси мікрокоманд 8, блоку формування кодів опевходи якого з'єднані з виходами блоку формуванрацій 10, лічильника К 11, лічильника L 12, блоку ня даних, вихід генератора тактових імпульсів формування адреси 13, блоку формування даних з'єднаний з входами лічильника адреси мікроко14 та блоку порівняння даних 15, виходи блоку манд, блоку формування синхросигналів, блоку формування кодів операцій 10 з'єднані з другими формування адреси, блоку формування кодів опевходами адаптера зв'язку 7, перші виходи блоку рацій, лічильника К, лічильника L, блоку формуформування адреси 13 і виходи блоку формуванвання даних й блоку порівняння даних, перші виня даних 14 з'єднані з третіми й четвертими вхоходи лічильника К, лічильника L, блоку дами адаптера зв'язку 7 відповідно, виходи якого формування адреси, блоку порівняння даних з'єдз'єднані з другими входами блоку порівняння данані з другими входами лічильника адреси мікроних 15, треті входи якого з'єднані з виходами блоку команд, треті входи/виходи якого з'єднані з четвеформування даних 14, вихід генератора тактових ртими входами/виходами інтерфейсного блоку, імпульсів 5 з'єднаний з входами лічильника адреси виходи якого з'єднані з четвертими входами блоку мікрокоманд 8, блоку формування синхросигналів порівняння даних, треті виходи блоку формування 6, блоку формування адреси 13, блоку формуванадреси з'єднані з третіми входами формувача коня кодів операцій 10, лічильника К 11, лічильника L дів функцій Уолша, виходи якого з'єднані з третіми 12, блоку формування даних 14 та блоку поріввходами блоку формування даних, а другі виходи няння даних 15, перші виходи лічильника К 11, лічильників К і L з'єднані з першими й другими лічильника L 12, блоку формування адреси 13 і 5 40675 6 блоку порівняння даних 15 з'єднані з другими вхоWal(0, 2, x, y)=0~y2; дами лічильника адреси мікрокоманд 8, треті вхоWal(0, 3, x, y)=0~(y2 Å y1); ди якого з'єднані з четвертими виходами інтерWal(1, 0, x, y)=x1~0; фейсного блоку 4, виходи якого з'єднані з Wal(1, 1, x, y)=x1~y1; четвертими входами блоку порівняння даних 15, Wal(1, 2, x, y)=x1~y2; треті виходи блоку формування адреси 13 з'єднані Wal(1, 3, x, y)=х1~(y2 Å y1); з третіми входами формувача кодів функцій УолWal(2, 0, x, y)=x2~0; ша 16, виходи якого з'єднані з третіми входами Wal(2, 1, x, y)=x2~y1; блоку формування даних 14, а другі виходи лічиWal(2, 2, x, y)=x2~y2; льників К і L з'єднані з першими й другими входами формувача кодів функцій Уолша 16 відповідно. Wal(2, 3, x, y)=x2~(y2 Å y1); На Фіг.2 наведена структурна схема формуваWal(3, 0, x, y)=(x2 Å х1)~0; ча кодів функцій Уолша, що складається з семи Wal(3, 1, x, y)=(x2 Å x1)~y1; елементів ВИКЛЮЧАЮЧЕ АБО D1-D7. Коди двовимірних функцій Уолша Wal{3, 2, x, y)=(x2 Å х1)~y2; Wal(k, l, х, у) = F{H(k, x), H(l, у)} Wal(3, 3, x, у)=(x2 Å x1)~(у2 Å y1). утворюються за допомогою операції еквівалеЗагальна кількість комбінацій кодів двовимірнтності (~) між елементами множини рядків них функцій Уолша при цьому рівна 16, що відпоК4={0,х1,х2,х2 Å х1} першої матриці Адамара H(k,х) і відає числу всіх можливих співставлень кодів в чотирьох суміжних запам'ятовуючих комірках, що елементами множини стовбців L4={0, y1,y2,y2 Å y1} оточують базову комірку пристрою, що тестується. Другої матриці H(l, у). Всі комбінації кодів даних, які отримуються за Значення кодів двовимірних функцій Уолша допомогою формувача кодів функцій Уолша, різні, при допустимих значеннях змінних k = 0,3 та таким чином в матриці Адамара відсутні рядки з однаковими елементами. l = 0,3 можна визначити за наступними формулаРозподіл кодів даних, які утворюються в сисми: темі взаємодіючих комірок п'ятого порядку навеWal(0, 0, x, y)=1; дено в таблиці 1. Wal(0, 1, x, y)=0~y1; Таблиця 1 Розподіл кодів даних в комірках Коди даних в комірках пам'яті при значеннях змінної l 1 2 Значення k 0 1 2 3 0 1 111 1 0 111 0 1 000 0 0 000 1 Якщо доповнити отримані комбінації кодів даних інверсними значеннями, то утворяться 32 послідовності контрольних даних, що забезпечують отримання всіх можливих комбінацій кодів в суміжних комірках, коли базові комірки зберігають l або 0. На Фіг.3 наведена структурна схема дворозрядного лічильника, два таких лічильника виконують функції лічильників К і L приладу. Лічильник складається з двох JK- тригерів D1 і D3, інвертора D2 та елемента 2U D4. Переключення тригерів в початкове положення здійснюється при подачі мікрооперації МК0. 1 010 1 0 010 0 1 101 0 0 101 1 0 100 0 1 100 1 0 011 1 1 011 0 3 0 001 0 1 001 1 0 110 1 1 111 0 Розрахунок стану тригерів здійснюється по мікро операції МК1. На виході елемента D4 формується ознака, яка відповідає одиничному стану обох тригерів. На Фіг.4 наведена структура блоку формування кодів операцій запису W і зчитування R, що складається з двох D - тригерів, які при подачі синхронізуючого сигналу запам'ятовують коди, що надходять з ПЗП мікрокоманд. На Фіг.5 наведена структура блоку формування даних, яка складається з елемента ВИКЛЮЧАЮЧЕ АБО D1, мультиплексорів D2.1-D2.P і регістра D3. Регістр може зберігати дані (Т:=Т) або запам'ятати коди функцій Уолша в прямому або 7 40675 8 інверсному коді Т:= Wal(k, l, х, у),Т:= not (Wal (к, l, Коди з виходів лічильника D5 передаються на х, у)). входи ПЗП мікрокоманд та забезпечують формуВибір режимів роботи регістра даних здійснювання послідовності мікрокоманд в процесі викоється за допомогою кодів мікрооперацій, що наднання тесту. ходять з ПЗП мікрокоманд. Коди з виходів ПЗП мікрокоманд, що надхоНа Фіг.6 наведена структурна схема блоку подять до входів лічильника D5 відповідає кодам рівняння зчитаних та еталонних даних, що складаадреси переходів, які виконуються при дотриманні ється з регістра реакцій U1, елементів ВИКЛЮвідповідних умов переходів, що надходять до вхоЧАЮЧЕ АБО D1.1 - D1.P, елементів 2І-HI D2.1 дів елементів D8 з виходів лічильників К, L, блоку D2.P, D3.1 - D3.P, регістра D4 й елемента І, що формування адреси, блоку порівняння даних, примає P входів. Зчитані дані надходять з виходів чому ознака переходу з виходу блоку формування адаптера зв'язку з об'єктом тестування, і запам'яадреси використовується двічі, в станах лічильнитовуються регістром реакції U1, еталонні дані надка D5, рівна "1001" і "1010". ходять з виходів блоку формування даних. Дозвіл Формування режиму паралельного запису копорівняння здійснюється при подачі на входи блодів адреси переходів забезпечують дешифратор ку кодів (Ip-I1) дозволу порівняння, що надходять з станів D6 і логічні елементи D8, D10, D11 та тригер виходів інтерфейсного блоку. До того ж дані буD13, сигнал, з виходу якого надходить до входу дуть зчитуватися лише в тих розрядах, в яких код LOAD лічильника D5 і забезпечує реалізацію мікдозволу порівняння зберігає одиницю. Однократно рокоманд умовного переходу. зафіксована помилка за допомогою елементів D3 Стани лічильника адреси мікрокоманд, що заблокує одиничний стан тих розрядів регістра, в фіксовані після завершення тесту або після прияких зафіксована помилка. Управління режимом пинення його виконання при виявленні відмов роботи регістра помилок D4 здійснюється за допристрою, що тестується, передаються до входів помогою кодів мікрооперацій, що надходять з виінтерфейсного блоку та використовуються блоком ходів ПЗП мікрокоманд. Результати порівняння управління та індикації для фіксування результату кодів об'єднуються на входах елемента D5 і перетестування або через блок зв'язку передаються в даються на вихід блоку. ПК для ідентифікації результатів тестування. На Фіг.7 наведена структурна схема блоку фоПристрій для тестової діагностики працює за рмування адреси, що складається з мультиплекалгоритмом, що наведений на Фіг.9. Перемикання сорів D1.1-D1.m, D3.1-D3.m, регістрів D2, D4, інрежимів роботи та станів основних вузлів прикриментора U1, цифрового компаратора U2 і строю здійснюється синхронно під управлінням перемикачів S1-Sm. тактових сигналів (CLK), формованих генератором Допоміжний регістр D2 може зберігати дані тактових імпульсів 5. Установка пристрою у вихід(D:=D), збільшувати код адреси на одиницю ний стан здійснюється за допомогою сигналу (D:=Inс) або переключаться в нульовий стан "RST", а початок виконання тесту забезпечується (D:=0), що відповідає установці початкового коду сигналом "Run", який формується блоком управадреси, рівного нулю. ління та індикації 3 або надходять від ПК через Компаратор U2 порівнює коди, що зберігаютьблок зв'язку 2. ся в регістрі D2 з кодами, що формуються перемиУ нульовому стані лічильника адреси мікрококачами S1-Sm, які визначають максимальний обманд 9 лічильник L 12 встановлюється також в сяг тестованої пам'яті. Результат порівняння нульовий стан за допомогою мікро операції компаратора передається на вхід лічильника адМК2=1, яка формується ПЗП мікрокоманд 9. В реси мікрокоманд. Коди регістра D2 передаються першому стані лічильника 8 до додаткового регістна входи блоку формування кодів функцій Уолша. ру адреси D2 (Фіг.7) заноситься код рівний нулю Регістр D4 може зберігати дані або запам'ятопри надходженні мікрооперації МК4=1. вувати коди, що формуються регістром D2. УправУ другому та третьому станах лічильника 8 ління режимами роботи регістрів D2 та D4 здійсапаратним способом за допомогою формувача 16 нюється за допомогою кодів мікрооперацій, що коди додаткового регістру адреси, лічильника К 11 надходять з виходів ПЗП мікрокоманд. і лічильника L 12 перетворюються в код функції На Фіг.8 наведена структурна схема лічильниУолша. У четвертому стані лічильника 8 по мікрока адреси мікрокоманд, яка складається з логічних команді ПЗП мікрокоманд 8 за допомогою блоку елементів D1, D2, D3, D7, D8, D9, D10, D11, D12, D формування коду операції 10, блоку формування - тригерів D4, D13, лічильника D5 і дешифратора адреси 13, блоку формування даних 14 утворюD6. ється код операції запису W, код адреси і код даТригер D4 фіксує робочий стан приладу та пених відповідно й за допомогою адаптера зв'язку 7 реключається в одиничний стан по сигналу "Пуск", дані коди передаються на входи пристрою, що який надходить з інтерфейсного блоку. Тригер D4 тестується, для виконання операції запису даних. переключається в нульовий стан при досягненні Якщо в п'ятому стані лічильника 8 код поточної лічильником D5 станів "1111" чи "1110", що фіксуадреси не дорівнює коду кінцевої адреси, яка ється елементами D7, D9.1, D9.2 та D12. При цьовстановлюється мікроперемикачами S1-Sm (Фіг.7), му стан "1111" відповідає виявленню відмов у які розташовані на блоці формування адреси 13, приладі, що тестується, і він вважається забракото відбувається перехід лічильника 8 до другого ваним, проте стан "1110" відповідає стану, коли стану й одночасно код додаткового регістру адрепри виконанні тесту відмов в приладі, що тестуси D2 (Фіг.7) збільшується на одиницю. ється, не зафіксовано і він вважається справним. Стани S2, S3, S4, S5 лічильника 8 повторюється до тих пір, поки код додаткового регістру 9 40675 10 адреси не стане дорівнювати коду кінцевої адревої адреси, заданої мікроперемикачами S1-Sm си, заданої мікроперемикачами S1-Sm (Фіг.7). (Фіг.7), при цьому лічильник 8 переходить до стану З метою скорочення кількості мікроперемикаS12, вміст лічильника К 11 збільшується на одиничів доцільно комутувати тільки старші розряди цю і операції запису, зчитування й порівняння дакодів компаратора U2 (Фіг.7), проте входи молодних повторюються при нових значеннях кодів фунших розрядів даного компаратора підключить до кцій Уолша, генерованих формувачем 16. джерела напруги логічної одиниці. Якщо в стані S12 лічильника 8 код лічильника Змінюючи положення перемикачів S1-Sm моK11 дорівнює 3, то лічильник 8 переходить до стажна змінювати обсяг тестованої пам'яті, що розну S13, вміст лічильника L 12 збільшується на ширює область застосування пристрою. одиницю і тест виконується при зміні станів лічиУ шостому стані лічильника 8 додатковий рельника K11 і нових значеннях кодів функцій Уолгістр адреси встановлюється в нульовий стан. У ша, генерованих формувачем 16. сьомому стані лічильника 8 код додаткового регісПри відсутності дефектів в пристрої, що тестутру адреси заноситься до регістру D4 (Фіг.7) блоку ється, тест завершиться, лічильник 8 переходить формування адреси та до блоку формування кодів до стану S14, пристрій припиняє роботу, при цьооперацій 10 заноситься код операції зчитування R. му тригер D4 (Фіг.8) перемикається до нульового За допомогою адаптера 7 для пристрою що тестустану, що знімає сигнал, який дозволяє роботу ється, формуються коди адреси та операції зчитулічильника адреси мікрокоманд 7. Стан S14 лічивання даних. льника 8 через інтерфейсний блок 4 передається В стані S8 лічильника 8 регістром U1 (Фіг.6) до блоку управління та індикації 3 або через блок запам'ятовуються зчитані з пристрою, що тестузв'язку 2 до ПК та ідентифікується як працездатється, данні, а отримані за допомогою формувача ний стан напівпровідникової пам'яті, що тестуєть16 коди функцій Уолша заносяться до блоку форся. мування даних 14 та використовуються потім в Загальна тривалість тесту складає 64n операякості еталонних значень. цій звертання, де n - ємність пам'яті, що тестуєтьВ стані S9 лічильника 8 зчитані та еталонні ся. Наприклад, тривалість тестування пам'яті ємніданні порівнюються блоком порівняння даних 15 і стю 64 Мбіт з часом циклу виявлення, що дорівнює результати порівняння фіксуються регістром по30 не, за допомогою моделі, яка заявляється, милок D4 (Фіг.6). Якщо зчитані з пристою, що тесскладає 2 с тується, данні не співпадають з еталонними даниПідвищується швидкодія пристрою та формоми, то лічильник 8 з стану S10 переходить до вані тестові послідовності дозволяють досягти стану S15 і відбувається зупинка роботи пристрою, позитивний ефект при його експлуатації за рахустан S15 лічильника 8 через інтерфейсний блок 4 нок підвищення якості напівпровідникової пам'яті, передається до блоку управління та індикації 3 що тестується. або через блок зв'язку 2 до ПК й ідентифікується Джерела інформації: як несправність, яка виявлена в пристрої, що тес1. Патент США. Algorithmically Programmable тується. Memory Tester With Breakpoint Trigger, Error Якщо зчитані з пристрою, що тестується, данні Jamming And Scope Mode Threat Memorizes Target співпадають з еталонними даними, то лічильник 8 Sequences. N006834364B2, Int.Cl.GO6F11/273, з стану S10 переходить до стану S11 і код додатDec.21, 2004. кового регістра адреси D2 (Фіг.7) збільшується на 2. Патент США. Algorithm Pattern Generator For одиницю. Стани S7, S8, S9, S10 та S11 повторюTesting A Memory Device and Memory Tester Using ються до тих пір, поки в стані S11 код регістра коду The Same. N7302623B2, Int.Cl.G11C29/00, Nov.27, адреси D4 (Фіг.7) не буде дорівнювати коду кінце2007. 11 40675 12 13 40675 14 15 40675 16 17 Комп’ютерна верстка Г. Паяльніков 40675 Підписне 18 Тираж 28 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for testing semiconductor memory

Автори англійськоюAndrienko Volodymyr Oleksandrovych, Riabtsev Volodymyr Hryhorovych, Utkina Tetiana Yuriivna

Назва патенту російськоюПрибор для тестирования полупроводниковой памяти

Автори російськоюАндриенко Владимир Александрович, Рябцев Владимир Григорьевич, Уткина Татьяна Юрьевна

МПК / Мітки

МПК: G11C 29/00

Мітки: напівпровідникової, прилад, пам'яті, тестування

Код посилання

<a href="https://ua.patents.su/9-40675-prilad-dlya-testuvannya-napivprovidnikovo-pamyati.html" target="_blank" rel="follow" title="База патентів України">Прилад для тестування напівпровідникової пам’яті</a>

Попередній патент: Експериментальний вентильний індукторно-реактивний привод

Наступний патент: Апарат лікувальний “піраміда сім’ї руденко”

Випадковий патент: Композиція для виготовлення сирокопченої ковбаси для гурманів