Мікросхема напівпровідникової пам’яті з вбудованими засобами самотестування та ремонту

Номер патенту: 69073

Опубліковано: 25.04.2012

Автори: Пилипець Сергій Сергійович, Рябцев Володимир Григорович, Уткіна Тетяна Юріївна, Андрієнко Володимир Олександрович

Формула / Реферат

Мікросхема напівпровідникової пам'яті з вбудованими засобами самотестування та ремонту, що містить основний масив запам'ятовуючих комірок, контролер самотестування, генератори кодів адреси та даних, мультиплексори кодів операцій МХ1, адреси МХ2 і даних МХ3, компаратор, причому перші, другі та треті виходи контролера самотестування підключені до перших входів мультиплексора кодів операцій МХ1, генератора кодів адреси і генератора кодів даних відповідно, другі входи мультиплексорів МХ1, МХ2, МХ3 підключені до виводів WR, Sys_Address, Sys_Data мікросхеми відповідно, виходи генератора кодів адреси і генератора кодів даних підключені до перших входів мультиплексорів МХ2 і МХ3 відповідно, виходи мультиплексорів МХ1, МХ2 підключені до перших та других входів основного масиву запам'ятовуючих комірок відповідно, виходи генератора кодів даних підключені до перших входів компаратора, на другі входи якого надходять дані з виходів основного масиву запам'ятовуючих комірок, перший вихід компаратора підключений до першого входу контролера самотестування мікросхеми, яка відрізняється тим, що в неї додатково введені запасний масив запам'ятовуючих комірок, шифратор, реконфігуратор вхідних даних і реконфігуратор вихідних даних, виходи якого підключені до виводів Data мікросхеми, перші та другий входи реконфігуратора вихідних даних підключені до виходів основного та запасного масивів запам'ятовуючих комірок відповідно, треті входи реконфігуратора вихідних даних і перші входи реконфігуратора вхідних даних підключені до виходів шифратора, входи якого підключені до других виходів компаратора, перший вихід якого підключений до виводу Т мікросхеми, вихід мультиплексора МХ3 підключений до других входів реконфігуратора вхідних даних, перші та другий виходи якого підключені до третіх входів основного та запасного масивів запам'ятовуючих комірок відповідно, другі та треті входи запасного масиву запам'ятовуючих комірок підключені до виходів мультиплексора МХ2 і мультиплексора МХ1 відповідно, вихід запасного масиву запам'ятовуючих комірок підключений до третього входу компаратора, четверті входи якого підключені до четвертих виходів контролера самотестування, третій, четвертий і п'ятий входи якого підключені до виводів ST, CLK, RST мікросхеми відповідно.

Текст

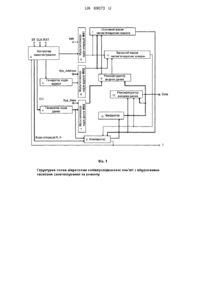

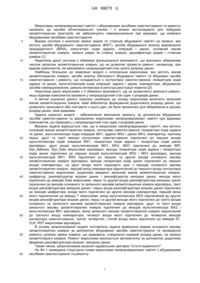

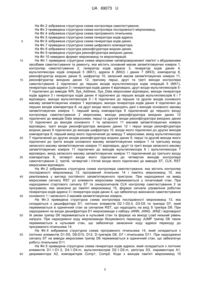

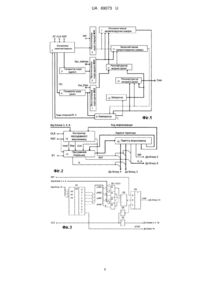

Реферат: Мікросхема напівпровідникової пам'яті з вбудованими засобами самотестування та ремонту належить до засобів обчислювальної техніки і її можна застосовувати для побудови запам'ятовуючих пристроїв, які забезпечують самовідновлення при відмовах, що виявлені вбудованими засобами самотестування. Включення запасного масиву запам'ятовуючих комірок забезпечує формування додаткового розряду даних і дозволить записувати або зчитувати з нього дані, які були призначені для збереження в одному розряді даних, який відмовив. UA 69073 U (12) UA 69073 U UA 69073 U 5 10 15 20 25 30 35 40 45 50 55 60 Мікросхема напівпровідникової пам'яті з вбудованими засобами самотестування та ремонту належить до засобів обчислювальної техніки і її можна застосовувати для побудови запам'ятовуючих пристроїв, які забезпечують самовідновлення при відмовах, що виявлені вбудованими засобами самотестування. Відома система з аналізом заміни рядків та стовпців вбудованої пам'яті на запасні, яка містить засоби вбудованого самотестування (BIST), засоби вбудованого аналізу відновлення працездатності (BIRA), комутатори кодів адреси, операцій і даних, основний масив запам'ятовуючих комірок, запасні рядки та стовпці комірок, дешифратори рядків і стовпців комірок [1]. Недоліком даної системи є обмежені функціональні можливості, що викликані обмеженим числом запасних запам'ятовуючих комірок, що не дозволяє провести ремонт, наприклад, при відмові компонентів, які викликають непрацездатний стан цілого розряду даних. Найбільш близькою до заявленої моделі є інтегральна мікросхема, яка містить масив запам'ятовуючих комірок, засоби аналізу збитковості вбудованої пам'яті та вбудовані засоби самотестування і ремонту, що складаються з контролера самотестування, генераторів кодів адреси та даних, мультиплексорів кодів операцій, адреси і даних, компаратора, вбудованих засобів самовідновлення, демультиплексора й регістра реєстрації помилок [2]. Недоліком даної мікросхеми є її обмежені можливості, що не дозволяють виконати ремонт, якщо відмови компонентів призвели у непрацездатний стан один з розрядів даних. З метою усунення даного недоліку необхідно до складу мікросхеми включити запасний масив запам'ятовуючих комірок, який забезпечує формування додаткового розряду даних, що дозволить записувати або зчитувати з нього дані, які були призначені для збереження в одному розряді даних, який відмовив. Задача корисної моделі - забезпечення виконання ремонту за допомогою вбудованих засобів самотестування та відновлення мікросхеми напівпровідникової пам'яті при відмовах компонентів, що приводять у непрацездатний стан один з розрядів даних. Вказана задача вирішується тим, що в мікросхему напівпровідникової пам'яті, яка містить основний масив запам'ятовуючих комірок, контролер самотестування, генератори кодів адреси та даних, мультиплексори кодів операцій МХ1, адреси МХ2 і даних МХ3, компаратор, причому перші, другі та треті виходи контролера самотестування підключені до перших входів мультиплексора кодів операцій МХ1, генератора кодів адреси і генератора кодів даних відповідно, другі входи мультиплексорів МХ1, МХ2, МХ3 підключені до виводів WR, Sys_Address, Sys_Data мікросхеми відповідно, виходи генератора кодів адреси і генератора кодів даних підключені до перших входів мультиплексорів МХ2 і МХ3 відповідно, виходи мультиплексорів МХ1, МХ2 підключені до перших та других входів основного масиву запам'ятовуючих комірок відповідно, виходи генератора кодів даних підключені до перших входів компаратора, на другі входи якого надходять дані з виходів основного масиву запам'ятовуючих комірок, перший вихід компаратора підключений до першого входу контролера самотестування мікросхеми, додатково введенні запасний масив запам'ятовуючих комірок, шифратор, реконфігуратор вхідних даних і реконфігуратор вихідних даних, виходи якого підключені до виводів Data мікросхеми, перші та другий входи реконфігуратора вихідних даних підключені до виходів основного та запасного масивів запам'ятовуючих комірок відповідно, треті входи реконфігуратора вихідних даних і перші входи реконфігуратора вхідних даних підключені до виходів шифратора, входи якого підключені до других виходів компаратора, перший вихід якого підключений до виводу Т мікросхеми, вихід мультиплексора МХ3 підключений до других входів реконфігуратора вхідних даних, перші та другий виходи якого підключені до третіх входів основного та запасного масивів запам'ятовуючих комірок відповідно, другі та треті входи запасного масиву запам'ятовуючих комірок підключені до виходів мультиплексора МХ2 і мультиплексора МХ1 відповідно, вихід запасного масиву запам'ятовуючих комірок підключений до третього входу компаратора, четверті входи якого підключені до четвертих виходів контролера самотестування, третій, четвертий і п'ятий входи якого підключені до виводів ST, CLK, RST мікросхеми відповідно. В основу запропонованої моделі поставлена задача виявлення відмов основного масиву запам'ятовуючих комірок за допомогою вбудованих засобів самотестування та проведення ремонту шляхом заміни комірок, що відмовили, утворюючи окремий розряд даних, на запасні запам'ятовуючі комірки. Ремонт мікросхеми виконується автоматично за допомогою додатково введених реконфігураторів вхідних і вихідних даних. Таким чином, запропоноване рішення задовольняє критерію "істотні відмінності". На Фіг.1 приведена структурна схема мікросхеми напівпровідникової пам'яті з вбудованими засобами самотестування та ремонту. 1 UA 69073 U 5 10 15 20 25 30 35 40 45 50 55 60 На Фіг.2 зображена структурна схема контролера самотестування. На Фіг.3 приведена структурна схема контролера послідовності мікрокоманд. На Фіг.4 зображена структурна схема програмного лічильника. На Фіг.5 приведена структурна схема генератора кодів адреси. На Фіг.6 зображена структурна схема генератора кодів даних. На Фіг.7 приведена структурна схема цифрового компаратора. На Фіг.8 зображена структура реконфігуратора вхідних даних. На Фіг.9 приведена структура реконфігуратора вихідних даних. На Фіг.10 наведено формат мікрокоманд та мікрооперацій. На Фіг.1 приведена структурна схема мікросхеми напівпровідникової пам'яті з вбудованими засобами самотестування та ремонту, яка містить основний масив запам'ятовуючих комірок 1, контролер самотестування 2, генератор кодів адреси 3, генератор кодів даних 4, мультиплексори кодів операцій 5 (МХ1), адреси 6 (МХ2) і даних 7 (МХ3), компаратор 8, реконфігуратор вхідних даних 9, шифратор 10, запасний масив запам'ятовуючих комірок 11, реконфігуратор вихідних даних 12, причому перші, другі та треті виходи контролера самотестування 2 підключені до перших входів мультиплексора кодів операцій 5 (МХ1), генератора кодів адреси 3 і генератора кодів даних 4 відповідно, другі входи мультиплексорів 57 підключені до виводів WR, Sys_Address, Sys_Data мікросхеми відповідно, виходи генератора кодів адреси 3 і генератора кодів даних 4 підключені до перших входів мультиплексорів 6 і 7 відповідно, виходи мультиплексорів 5 і 6 підключені до перших та других входів основного масиву запам'ятовуючих комірок 1 відповідно, виходи генератора кодів даних 4 підключені до перших входів компаратора 8, на другі входи якого надходять дані з виходів основного масиву запам'ятовуючих комірок 1, перший вихід компаратора 8 підключений до першого входу контролера самотестування 2 мікросхеми, виходи реконфігуратора вихідних даних 12 підключені до виводів Data мікросхеми, перші та другий входи реконфігуратора вихідних даних 12 підключені до виходів основного 1 та запасного 11 масивів запам'ятовуючих комірок відповідно, треті входи реконфігуратора вихідних даних 12 і перші входи реконфігуратора вхідних даних 9 підключені до виходів шифратора 10, входи якого підключені до других виходів компаратора 8, перший вихід якого підключений до виводу Т мікросхеми, вихід мультиплексора 7 підключений до других входів реконфігуратора вхідних даних 9, перші та другий виходи якого підключені до третіх входів основного масиву запам'ятовуючих комірок 1 та третьому входу запасного масиву запам'ятовуючих комірок 11 відповідно, другі та треті входи запасного масиву запам'ятовуючих комірок 11 підключені до виходів мультиплексора 6 і мультиплексора 7 відповідно, вихід запасного масиву запам'ятовуючих комірок 11 підключений до третього входу компаратора 8, четверті входи якого підключені до четвертих виходів контролера самотестування 2, третій, четвертий і п'ятий входи якого підключені до виводів ST, CLK, RST мікросхеми відповідно. На Фіг.2 зображена структурна схема контролера самотестування, яка містить контролер послідовності мікрокоманд 13, програмний лічильник 14 і пам'ять мікрокоманд 15, яка реалізована у вигляді постійного запам'ятовуючого пристрою. При надходженні на вивід мікросхеми сигналу RST усі елементи мікросхеми перемикаються у початковий стан. При надходженні стартового сигналу ST та синхросигналів CLK контролер самотестування 2 за програмою, яка занесена до пам'яті мікрокоманд 15, формує сигнали управління роботою генератора кодів адреси 3 і генератора кодів даних 4, що забезпечує виконання самотестування основного 1 і запасного 2 масивів запам'ятовуючих комірок. На Фіг.3 приведена структурна схема контролера послідовності мікрокоманд 13, яка складається з дешифратора D1, логічних елементів D2.1-D2.4, D3-D5 та тригера D7, який перемикається в одиничний стан за сигналом RST, що надходить на вхід S тригера D6. При надходженні на входи дешифратора D1 мікрокоманди з набору JANN, JANG, JKNZ і відповідної їй умови тригер D6 перемикається в нульовий стан та формує на виході Load низький рівень напруги. При надходженні коду мікрокоманди безумовного переходу JUMP тригер D6 також перемикається в нульовий стан, що забезпечує занесення коду адреси переходу до програмного лічильника 14. На Фіг.4 зображена структурна схема програмного лічильника 14, який складається з логічних елементів D1-D5, D8-D10, D12, D-тригерів D6, D7 і лічильника D11. При надходженні сигналу ST на виводи мікросхеми тригер D6 перемикається в одиничний стан, що забезпечує роботу лічильника D11. На Фіг.5 приведена структурна схема генератора кодів адреси, який складається з логічних елементів D1.1-D1.3, D4.1-D4.m, мультиплексорів D2.1-D2.m, регістра D3, інкриментора А1, декриментора А2, компараторів Comp1, Comp2. Коди з виходів пам'яті мікрокоманд 15 2 UA 69073 U 5 10 15 20 25 надходять на входи генератора кодів адреси 3 і забезпечують формування наступних мікрооперацій: А:=А, А:=not A, A:=A+1, A:=A-1, A:=N, А:=G, де А - поточний код адреси, N - код кінцевої адреси комірок пам'яті, G - код початкової адреси комірок пам'яті. Компаратор Comp1 формує прапор переходу A=N, компаратор Соmр2 - ознаку переходу А=G, які використовуються контролером послідовності мікрокоманд 13 для реалізації мікрокоманд умовного переходу. На Фіг.6 зображена структурна схема генератора кодів даних 4, який складається з логічних елементів D1.1-D1.2, D4.1-D4.p+1, D5.1-D5.p+1, мультиплексорів D2.1-D2.p+1 і регістра D3. Коди з виходів пам'яті мікрокоманд 15 надходять на входи генератора кодів даних 4 і забезпечують формування наступних робочих мікрооперацій: Т:=Т, Т:=not T, T:=S, де S - код занесення даних, які надходять з виходів пам'яті мікрокоманд 15. Коди даних запам'ятовуються регістром D3 і передаються на виходи генератора кодів даних 4. На Фіг.7 приведена структурна схема цифрового компаратора 8, що містить елементи HEВИКЛЮЧАЮЧЕ АБО D1.1-D1.p+1, 2I D2, 2І-НІ D3.1-D3.p+1, регістр D4, багатовхідний елемент І D5, буферний елемент D6 та регістр U1. На Фіг.8 зображена структура реконфігуратора вхідних даних 9 для 8-ми розрядного запам'ятовуючого пристрою, який складається з буферних елементів D1, D9 та мультиплексорів D2-D8. На перші входи реконфігуратора вхідних даних 9 надходять коди з виходів генератора кодів даних 4. На другі входи реконфігуратора вхідних даних 9 надходять коди з виходів шифратора 10, що забезпечує заміну розрядів даних, що відмовили, основного масиву запам'ятовуючих комірок 1 на запасний масив запам'ятовуючих комірок 11. На Фіг.9 приведена структура реконфігуратора вихідних даних 12, який складається з мультиплексорів D1-D8, на перший вхід реконфігуратора вхідних даних 12 надходять дані з виходу запасного масиву запам'ятовуючих комірок 11, на другі входи реконфігуратора вихідних даних 12 надходять дані з виходів основного масиву запам'ятовуючих комірок 1. На управляючі входи мультиплексорів D1-D8 надходять коди з виходів шифратора 10, що забезпечує заміну розряду даних, що відмовив, основного масиву даних на дані, які надходять з виходу запасного масиву запам'ятовуючих комірок 11. Таблиця істинності шифратора 10 для 8-ми розрядного коду даних має вид, наведений нижче. 30 Таблиця 1 Коди для розрядів 8 0 0 0 0 0 0 0 0 0 1 35 40 7 0 0 0 0 0 0 0 0 1 X 6 0 0 0 0 0 0 0 1 0 X на вході 5 4 3 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 0 0 0 0 0 X X X для інших кодів 2 0 0 0 1 0 0 0 0 0 X 1 0 0 1 0 0 0 0 0 0 X 0 0 1 0 0 0 0 0 0 0 X 7 0 0 0 0 0 0 0 0 1 0 0 6 0 0 0 0 0 0 0 1 1 0 0 5 0 0 0 0 0 0 1 1 1 0 0 на виході 4 3 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 0 0 0 2 0 0 0 1 1 1 1 1 1 0 0 1 0 0 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 На Фіг.10 наведено формат мікрокоманд та мікрооперацій, який складається з наступних полів: - коду мікрокоманди; - робочих мікрооперацій запису (W), зчитування (R) та порівняння (А); - коду мікрооперацій адреси; - коду мікрооперацій даних; - адреси переходу. Для формування тестів використовуються наступні мікрокоманди: NOOP - відсутність операції, забезпечує перехід до наступної мікрокоманди; JANN - перехід до команди, код адреси якої записано у полі адреси переходу, якщо поточна адреса комірок пам'яті не дорівнює адресі кінцевої комірки (A≠N); JANG - перехід до команди, код адреси якої записано у полі адреси переходу, якщо поточна адреса комірок пам'яті не дорівнює адресі початкової комірки (A≠G); 3 UA 69073 U 5 10 15 20 25 30 35 JUMP - безумовний перехід до команди, код адреси якої записано у полі адреси переходу; JKNZ - умовний перехід до команди, адреса переходу якої записана у полі адреси переходу, якщо при порівнянні зчитаних даних з еталонними значеннями виявлена розбіжність кодів (К≠0); STOP - зупинка виконання тесту. Приклад програми тесту MarchC наведено нижче. При виконанні тесту MarchC відбувається 10 n циклів звертання до масиву комірок пам'яті: 5 n циклів для запису та 5 n циклів для зчитування. Мікросхема напівпровідникової пам'яті працює наступним чином. Для ініціалізації мікросхеми на вхід RST подається сигнал високого рівня напруги, який забезпечує встановлення в початковий стан усіх компонентів мікросхеми, які забезпечують виконання самотестування. Після подачі на вхід ST мікросхеми стартового сигналу на виході тригера D6 програмного лічильника 14 формується сигнал високого рівня напруги, який дозволяє роботу генератора кодів адреси 3, генератора кодів даних 4, за програмою, що занесена до пам'яті мікрокоманд 15. При виконанні самотестування зчитані дані з виходів блоків 1, 11 надходять на входи компаратора 8 і запам'ятовуються ним. Еталонні дані надходять з виходів генератора кодів даних 4. Порівняння кодів здійснюють елементи HE-ВИКЛЮЧАЮЧЕ АБО D1.1-D1.p+1 компаратора 8. Результати порівняння через елементи D3.1-D3.p+1 надходять на входи регістра D4 і запам'ятовуються ним. Одноразово зафіксована розбіжність кодів зчитаних та еталонних даних за допомогою елементів D3.1D3.p+1 фіксує одиночний стан тих розрядів, в яких зафіксована помилка. Управління режимом роботи регістрів U1 і D4 блока 8 здійснюється за допомогою кодів мікрооперацій, що надходять від пам'яті мікрокоманд 15 і контролера послідовності мікрокоманд 13. Результат самотестування через багатовхідний елемент І D5 та буфер D6 передаються на вивід Т і використовується для визначення працездатного стану мікросхеми. За станом напруги на виході Т ідентифікується стан мікросхеми. За наявності високого рівня напруги на виході Т мікросхема вважається непрацездатною, але вона підлягає відновленню. Коди результатів самотестування, зафіксовані у регістрі D4 компаратора 8, забезпечують управління реконфігураторами вхідних даних 9 та вихідних даних 12 таким чином, що забезпечується заміна вихідних даних розряду основного масиву запам'ятовуючих комірок 1, який відмовив, на дані, що надходять з виходів запасного масиву запам'ятовуючих комірок 11. Таким чином виконується автоматичний ремонт мікросхеми напівпровідникової пам'яті. Техніко-економічний ефект при застосуванні заявленої моделі досягається за рахунок підвищення надійності роботи мікросхеми напівпровідникової пам'яті шляхом відновлення 4 UA 69073 U 5 10 15 20 25 30 35 працездатного стану після виникнення відмов. Як масив пам'яті може бути використана динамічна оперативна пам'ять, статична оперативна пам'ять або будь-яка інша оперативна пам'ять, що має структурований масив запам'ятовуючих елементів. Джерела інформації: 1. Патент США. Built-in spare row and column replacement analysis System for embedded memories. N6304989, Int.Cl. G01R 31/28. Oct. 16, 2001. 2. Патент США. Redundancy analysis for embedded memories with built-in self test and built-in self repair. N6067262, Int.Cl. G11С 7/00. May 23, 2000. ФОРМУЛА КОРИСНОЇ МОДЕЛІ Мікросхема напівпровідникової пам'яті з вбудованими засобами самотестування та ремонту, що містить основний масив запам'ятовуючих комірок, контролер самотестування, генератори кодів адреси та даних, мультиплексори кодів операцій МХ1, адреси МХ2 і даних МХ3, компаратор, причому перші, другі та треті виходи контролера самотестування підключені до перших входів мультиплексора кодів операцій МХ1, генератора кодів адреси і генератора кодів даних відповідно, другі входи мультиплексорів МХ1, МХ2, МХ3 підключені до виводів WR, Sys_Address, Sys_Data мікросхеми відповідно, виходи генератора кодів адреси і генератора кодів даних підключені до перших входів мультиплексорів МХ2 і МХ3 відповідно, виходи мультиплексорів МХ1, МХ2 підключені до перших та других входів основного масиву запам'ятовуючих комірок відповідно, виходи генератора кодів даних підключені до перших входів компаратора, на другі входи якого надходять дані з виходів основного масиву запам'ятовуючих комірок, перший вихід компаратора підключений до першого входу контролера самотестування мікросхеми, яка відрізняється тим, що в неї додатково введені запасний масив запам'ятовуючих комірок, шифратор, реконфігуратор вхідних даних і реконфігуратор вихідних даних, виходи якого підключені до виводів Data мікросхеми, перші та другий входи реконфігуратора вихідних даних підключені до виходів основного та запасного масивів запам'ятовуючих комірок відповідно, треті входи реконфігуратора вихідних даних і перші входи реконфігуратора вхідних даних підключені до виходів шифратора, входи якого підключені до других виходів компаратора, перший вихід якого підключений до виводу Т мікросхеми, вихід мультиплексора МХ3 підключений до других входів реконфігуратора вхідних даних, перші та другий виходи якого підключені до третіх входів основного та запасного масивів запам'ятовуючих комірок відповідно, другі та треті входи запасного масиву запам'ятовуючих комірок підключені до виходів мультиплексора МХ2 і мультиплексора МХ1 відповідно, вихід запасного масиву запам'ятовуючих комірок підключений до третього входу компаратора, четверті входи якого підключені до четвертих виходів контролера самотестування, третій, четвертий і п'ятий входи якого підключені до виводів ST, CLK, RST мікросхеми відповідно. 5 UA 69073 U 6 UA 69073 U 7 UA 69073 U 8 UA 69073 U Комп’ютерна верстка А. Рябко Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 9

ДивитисяДодаткова інформація

Назва патенту англійськоюSemiconductor memory microcircuit with built-in self-testing and repair means

Автори англійськоюAndrienko Volodymyr Oleksandrovych, Pylypets Serhii Serhiiovych, Riabtsev Volodymyr Hryhorovych, Utkina Tetiana Yuriivna

Назва патенту російськоюМикросхема полупроводниковой памяти со встроенными средствами самотестирования и ремонта

Автори російськоюАндриенко Владимир Александрович, Пилипец Сергей Сергеевич, Рябцев Владимир Григорьевич, Уткина Татьяна Юрьевна

МПК / Мітки

МПК: G11C 7/00

Мітки: мікросхема, пам'яті, напівпровідникової, ремонту, засобами, самотестування, вбудованими

Код посилання

<a href="https://ua.patents.su/11-69073-mikroskhema-napivprovidnikovo-pamyati-z-vbudovanimi-zasobami-samotestuvannya-ta-remontu.html" target="_blank" rel="follow" title="База патентів України">Мікросхема напівпровідникової пам’яті з вбудованими засобами самотестування та ремонту</a>

Попередній патент: Спосіб посилення антиноціцептивного ефекту електромагнітного екранування

Наступний патент: Суха суміш для обробки вогнетривких основ та процес обробки вогнетривких основ

Випадковий патент: Гідродинамічне гальмо