Мікросхема напівпровідникової пам`яті з вбудованими засобами самотестування

Номер патенту: 47842

Опубліковано: 25.02.2010

Автори: Уткіна Тетяна Юріївна, Рябцев Володимир Григорович, Андрієнко Володимир Олександрович

Формула / Реферат

Мікросхема напівпровідникової пам'яті з вбудованими засобами самотестування, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора 1 і комутатора 2 відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виводів даних мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті інструкцій, входи якої підключені до виходів програмного лічильника, перший вхід якого підключений до виводу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті інструкцій підключені до перших входів контролера послідовності інструкцій, треті виходи пам'яті інструкцій підключені до входів арифметико-логічного пристрою (АЛП) адреси, четверті виходи пам'яті інструкцій підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключений до виводу мікросхеми, на який видається результат тестування Т1, перші входи комутатора 1 і комутатора 2 підключені до виходів буфера адреси, входи якого є адресними входами мікросхеми, другі і треті виходи АЛП адреси підключені до других входів комутатора 1 і комутатора 2 відповідно, перші виходи контролера послідовності інструкцій підключені до перших входів програмного лічильника, а група виходів контролера послідовності інструкцій використовується для керування режимами роботи компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми підключені до виводів мікросхеми, на які подаються керуючі сигнали CS, AS, WE, OE, а виводи даного контролера використовуються для видачі сигналів, що визначають режими роботи мікросхеми, яка відрізняється тим, що в неї додатково введені формувач кодів функцій Уолша (ФКФУ), буферний елемент і вивід для подачі синхронізуючого сигналу CLK, причому перші входи ФКФУ підключені до третіх виходів АЛП адреси, другі входи ФКФУ підключені до п'ятих виходів пам'яті інструкцій, треті виходи ФКФУ підключені до других виходів контролера послідовності інструкцій, перші виходи ФКФУ підключені до других входів АЛП даних, другі виходи ФКФУ підключені до перших входів контролера послідовності інструкцій, вхід буферного елемента підключений до виводу CS мікросхеми, а вихід буферного елемента підключений до другого входу контролера послідовності інструкцій, третій, четвертий і п'ятий входи якого підключені до виводу мікросхеми, на який подається синхронізуючий сигнал CLK, другого виходу компаратора даних та третього виходу АЛП адреси відповідно, шості виходи пам'яті інструкцій підключені до третіх входів програмного лічильника, другі виходи якого підключені до п'ятих входів контролера послідовності інструкцій.

Текст

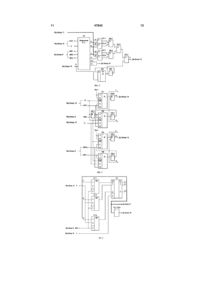

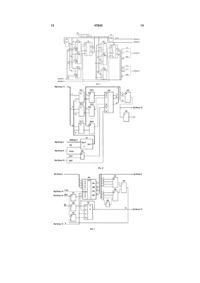

Мікросхема напівпровідникової пам'яті з вбудованими засобами самотестування, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора 1 і комутатора 2 відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виводів даних мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті інструкцій, входи якої підключені до виходів програмного лічильника, перший вхід якого підключений до виводу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті інструкцій підключені до перших входів контролера послідовності інструкцій, треті виходи пам'яті інструкцій підключені до входів арифметико-логічного пристрою (АЛП) адреси, четверті виходи пам'яті інструкцій підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключений до виводу мікросхеми, на який видається результат тестування Т1, перші входи комутатора 1 і комутатора 2 підключені до виходів U 2 UA 1 3 з контролера станів цифрового автомату, генератора адреси, генератора даних і комутатора, а також регістра несправностей, модуля ремонту і регістру сканування [1]. Недоліком даної мікросхеми запам'ятовуючого пристрою є низькі діагностичні властивості тестових дій, набір яких визначається алгоритмом роботи контролера цифрового автомату з кінцевим числом станів. Найбільш близьким до запропонованого є метод тестування пам'яті й інтегральна напівпровідникова мікросхема [2], яка містить масив пам'яті, дешифратор адреси X, дешифратор адреси Y, підсилювачі зчитування, буфер адреси, елементи введення/виведення, контролер схеми, програмний лічильник, пам'ять інструкцій, контролер послідовності інструкцій, АЛП адреси, АЛП даних, комутатор адреси X, комутатор адреси Y, компаратор, що здійснює порівняння даних. Недоліком даної мікросхеми є необхідність застосування більшої ємності пам'яті інструкцій для зберігання програми тесту, який забезпечує отримання усіх можливих сполучень кодів даних, що зберігаються в суміжних комірках пам'яті, які оточують базові комірки, що може викликати найбільший взаємний вплив комірок масиву пам'яті, а, відповідно, призведе до виникнення найбільш імовірних відмов мікросхеми. При збільшенні об'єму пам'яті інструкцій знижується ступінь інтеграції мікросхеми, що приводить до зменшення кількості комірок пам'яті, тобто інформаційної ємності мікросхеми. Мета корисної моделі - підвищення вірогідності результатів тестування напівпровідникової пам'яті за рахунок виконання тесту, який забезпечує отримання усіх можливих сполучень кодів даних, що зберігаються в суміжних комірках, які оточують базові комірки, що приводить до виявлення відмов, викликаних взаємним впливом запам'ятовуючих комірок, при цьому зменшується ємність програми тесту шляхом використання апаратно мікропрограмного способу формування тесту, який поєднує високу швидкодію з невеликими апаратними витратами. Вказана мета досягається тим, що в інтегральну напівпровідникову мікросхему, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора 1 і комутатора 2 відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виводів даних мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті інструкцій, входи якої підключені до виходів програмного лічильника, перший вхід якого підключено до виводу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті інструкцій підключені до перших входів контролера послідовності інструкцій, треті виходи пам'яті інструкцій підключені до входів АЛП адреси, четверті виходи пам'яті інструкцій підключені до перших входів 47842 4 АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, вихід якого підключено до виводу мікросхеми, на який видається результат тестування ТІ, перші входи комутатора 1 і комутатора 2 підключені до виходів буфера адреси, входи якого є адресними входами мікросхеми, другі і треті виходи АЛП адреси підключені до других входів комутатора 1 і комутатора 2 відповідно, перші виходи контролера послідовності інструкцій підключені до перших входів програмного лічильника, а група виходів контролера послідовності інструкцій використовується для керування режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми підключені до виводів мікросхеми, на які подаються керуючі сигнали CS, AS, WE, OE, а виводи даного контролера використовуються для видачі сигналів, які визначають режими роботи мікросхеми, додатково введені ФКФУ, буферний елемент і вивід для подачі синхронізуючого сигналу CLK, причому перші входи ФКФУ підключені до третіх виходів АЛП адреси, другі входи ФКФУ підключені до п'ятих виходів пам'яті інструкцій, треті входи ФКФУ підключені до других виходів контролера послідовності інструкцій, перші виходи ФКФУ підключені до других входів АЛЛ даних, другі виходи ФКФУ підключені до перших входів контролера послідовності інструкцій, вхід буферного елемента підключено до виводу CS мікросхеми, а вихід буферного елемента підключено до другого входу контролера послідовності інструкцій, третій, четвертий і п'ятий входи якого підключені до виводу мікросхеми, на який подається синхронізуючий сигнал CLK, другого виходу компаратора даних, третього виходу АЛП адреси відповідно, шості виходи пам'яті інструкцій підключені до третіх входів програмного лічильника, другі виходи якого підключені до п'ятих входів контролера послідовності інструкцій. В основу запропонованої мікросхеми поставлена задача підвищення вірогідності результатів тестування напівпровідникової пам'яті шляхом застосування запропонованого рішення, ознаки якого вказані в частині формули корисної моделі, яка відрізняється від аналогу і виявляє в процесі взаємодії характерні особливості, які надають позитивний ефект. Таким чином, запропоноване рішення задовольняє критерію "істотні відмінності". На Фіг.1 наведена структурна схема мікросхеми напівпровідникової пам'яті з вбудованими засобами самотестування. На Фіг.2 зображена структурна схема формувача кодів функцій Уолша. На Фіг.3 наведена структурна схема лічильників К і L. На Фіг.4 зображена структурна схема АЛП даних. На Фіг.5 наведена структурна схема АЛП адреси. На Фіг.6 зображена структурна схема компаратора даних. На Фіг.7 наведена структурна схема програм 5 ного лічильника. На Фіг.8 зображена структурна схема контролера послідовності інструкцій. На Фіг.9 наведено алгоритм роботи мікросхеми напівпровідникової пам'яті в режимі самотестування. На Фіг.1 наведена структурна схема мікросхеми напівпровідникової пам'яті з вбудованими засобами самотестування, яка містить масив комірок пам'яті 1, оснащений дешифратором адреси X 2 і дешифратором адреси Y 3, входи яких підключені до виходів першого комутатора 14 і другого комутатора 15 відповідно, підсилювачі зчитування 4, входи/виходи яких підключені до перших входів/виходів селектора 17 і перших входів компаратора даних 16, другі входи/виходи селектора 17 підключені до перших входів/виходів елементів введення/виведення 6, другі входи/виходи яких підключені до виводів даних Data мікросхеми, треті входи елементів введення/виведення 6 і другі входи підсилювачів зчитування 4 підключені до перших виходів пам'яті інструкцій 9, входи якої підключені до виходів програмного лічильника 8, перший вхід якого підключено до виводу мікросхеми ST, на який подається стартовий сигнал, другі виходи пам'яті інструкцій 9 підключені до перших входів контролера послідовності інструкцій 10, треті виходи пам'яті інструкцій 9 підключені до входів АЛП адреси 11, четверті виходи пам'яті інструкцій 9 підключені до перших входів АЛП даних 13, перші виходи якого підключені до третіх входів селектора 17, а другі виходи АЛП даних 13 підключені до других входів компаратора даних 16, перший вихід якого підключено до виводу мікросхеми Т1, на який видається результат тестування, перші входи першого комутатора 14 і другого комутатора 15 підключені до виходів буфера адреси 5, входи якого є адресними входами AD мікросхеми, другі і треті виходи АЛП адреси 11 підключені до других входів першого комутатора 14 і другого комутатора 15 відповідно, перші виходи контролера послідовності інструкцій 10 підключені до перших входів програмного лічильника 8, а група виходів контролера послідовності інструкцій 10 використовується для керування режимами роботи компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми 7 підключені до виводів мікросхеми, на які подаються керуючі сигнали CS, AS, WE, OE, а виводи контролера мікросхеми 7 використовуються для видачі сигналів, які визначають режими роботи мікросхеми, яка також містить ФКФУ 12, буферний елемент 18 і вивід для подачі синхронізуючого сигналу CLK, причому перші входи ФКФУ 12 підключені до третіх виходів АЛП адреси 11, другі входи ФКФУ 12 підключені до п'ятих виходів пам'яті інструкцій 9, треті входи ФКФУ 12 підключені до других виходів контролера послідовності інструкцій 10, перші виходи ФКФУ 12 підключені до других входів АЛП даних 13, другі виходи ФКФУ 12 підключені до перших входів контролера послідовності інструкцій 10, вхід буферного елемента 18 підключено до виводу CS мікросхеми, а вихід буферного елемента підключено до другого входу контролера послідовності інструкцій 10, третій, 47842 6 четвертий і п'ятий входи якого підключені до виводу мікросхеми, на який подається синхронізуючий сигнал CLK, другого виходу компаратора даних 16, третього виходу АЛП адреси 11 відповідно, шості виходи пам'яті інструкцій 9 підключені до третіх входів програмного лічильника 8, другі виходи якого підключені до п'ятих входів контролера послідовності інструкцій 10. На Фіг.2 зображена структурна схема ФКФУ, що містить лічильники К і L, які розміщені в блоці U1, елементи ВИКЛЮЧАЮЧЕ АБО D1.1, D1.2, D2.1, D2.2, D4.1, D4.2, D4.3, D4.4, D-тригер D3 та інвертор D5. Виходи k0 і k1, лічильника К підключені до перших входів елементів Dl.l I D1.2 відповідно, другі входи яких підключені до входів B0, B1. Виходи l 0, l1, лічильника L підключені до перших входів елементів D2.1 і D2.2 відповідно. Другі входи елементів D2.1 і D2.2 підключені до входів В2 і ВЗ відповідно. На входи В0, В1, В2, ВЗ надходять коди від АЛП адреси 11 і їм відповідають Х0, X1, Y0, Y1 коди адреси рядків і стовпців масиву комірок пам'яті 1. На входи лічильників L, R надходять керуючі сигнали від пам'яті інструкцій 9 і контролера послідовності інструкцій 10. На Фіг.3 наведена структурна схема двохрозрядних лічильників К і L, яка містить 4 J-К-тригера D1-D4, елементи 21 D5.1, D5.2, D5.3 та інвертори D6.1, D6.2. На входи лічильників К і L надходять коди мікрооперацій з пам'яті інструкцій 9 і контролера послідовності інструкцій 10. На Фіг.4 зображена структурна схема АЛП даних, яка містить мультиплексори D1.1-D1.p, регістр D2 і групу буферних елементів D3. Число мультиплексорів і число розрядів регістра D2 АЛП даних рівне числу інформаційних розрядів масиву комірок пам'яті 1. Регістр D2 може зберігати дані (Т :=Т) або запам'ятовувати коди функцій Уолша в прямому та інверсному коді: T:=Wal(k,l,x,y), T:=notWal(k,l,x,y). Вибір режиму роботи регістра D2 здійснюється за допомогою кодів мікрооперацій, що надходять з пам'яті Інструкцій 9. Для отримання прямих та інверсних функцій Уолша необхідно тестування виконати два рази. Перед кожним початком тестування тригер D3 (Фіг.2) змінює свій стан, що забезпечує інверсію кодів елементом D4.4 (Фіг.2). Коди двохмірних функцій Уолша Wal(k, l, х, y)=F{H(k, x), H(l, у)} формуються за допомогою операції еквівалентності (~) між елементами множини рядків першої матриці Адамара H(k, х) і елементами множини стовпців другої матриці Адамара Н(l, у). Значення кодів двохмірних функцій Уолша при припустимих значеннях змінних k 0,3 та l можна визначити за наступними формулами: Wal(0,0,x,y)=l; Wal(0,1,x,y)=0~y0; Wal(0,2,x,y)=0~y1; 0,3 7 47842 Wal(0,3,x,y)=0~(y1 y0); Wed(1,0,x,y)=x0~0; Wal(1,1,x,y)=x0~y0; Wal(1,2,x,y)=x0~y1; Wal(1,3,x,y)=x0~(y1 Wal(2,0,x,y)=x1,~0; Wal(2,1,x,y)=xl~y0; Wal(2,2,x,y)=x1~y1; y0); Wal(2,3,x,y)=x1~(y1 y0); Wal(3,0,х,у)=(х1 х0)~0; Wal(3,l,x,y)=(x1 x0)~y0; Wal(l,2,x,y)=(x1 x0)~y1; Wal(3,3,х,у)=(х1 x0)~(у1 y0). Загальне число комбінацій кодів двохмірних функцій Уолша при цьому рівне 16, що відповідає числу всіх можливих сполучень кодів в чотирьох суміжних комірках пам'яті, які оточують базову комірку. Всі комбінації кодів даних, які отримуються за допомогою функцій Уолша різні, оскільки в матрицях Адамара відсутні рядки з однаковими елементами. Розподіл інформації для запам'ятовуючого пристрою ємністю 16 біт, отриманий за допомогою двохмірних функцій Уолша, наведено в таблиці 1. Таблиця 1 Розподіл інформації для запам'ятовуючого пристрою ємністю 16 біт Таблиця 1 (Продовження) Розподіл інформації для запам'ятовуючого пристрою ємністю 16 біт В таблиці 1 заштриховане поле відповідає 1, незаштриховане - 0. При кількості комірок пам'яті більше 16 комбінацій коди мультиплікуються по всьому об'єму пам'яті. Наприклад, для змінних k=l=1 в якості тестових даних використовується "шаховий" код, який буде записуватися у всі комірки пам'яті. Якщо доповнити отримані комбінації кодів даних, наведені в таблиці 1, інверсними значеннями, 8 то утворюється тестова послідовність, яка забезпечує отримання усіх можливих комбінацій кодів в суміжних комірках, коли базові комірки зберігають 1 або 0. На Фіг.5 наведена структурна схема АЛП адреси, що складається з мультиплексорів D1.1D1.m, допоміжного регістра D2, мультиплексорів D3.1-D3.m, регістра адреси D4, інкрементора U1 і цифрового компаратора U2. Число розрядів регістрів і кількість мультиплексорів визначається ємністю масиву комірок пам'яті. За квадратної конфігурації комірок пам'яті половина кодів адреси з виходу регістру D4 надходить на входи першого комутатора 14, а друга частина кодів адреси - на входи другого комутатора 15. Допоміжний регістр D2 може зберігати дані (D:=D), збільшувати код адреси на одиницю (D:=Inc) або перемикатися в нульовий стан (D:=0), що відповідає встановленню початкового коду адреси, рівного нулю. Цифровий компаратор U2 порівнює коди, що зберігаються в регістрі D2 з кодами кінцевої адреси, які визначають максимальний об'єм пам'яті, що тестується. Результат порівняння (B=N) передається на вхід контролера послідовності інструкцій 10. Коди регістра D2 передаються на входи ФКФУ 12. Регістр D4 може зберігати дані або запам'ятовувати коди, що формуються регістром D2. Керування режимами роботи регістрів D2 та D4 здійснюється за допомогою кодів мікрооперацій, які надходять з виходів пам'яті інструкцій 9. На Фіг.6 наведена структурна схема цифрового компаратора даних 16, що містить елементи HE-ВИКЛЮЧАЮЧЕ АБО D1.1-D1.p, 2ІD2, 2І-HI D3.1-D3.p, регістр D4, багатовхідний елемент І D5, буферний елемент D6 та регістр U1. Зчитані дані з виходів підсилювачів зчитування 4 надходять на входи регістра U1 і запам'ятовуються ним. Еталонні дані надходять з виходів АЛП даних 13. Порівняння кодів здійснюють елементи НЕ-ВИКЛЮЧАЮЧЕ АБО D1.1-D1.p. Результат порівняння через елементи D3.1-D3.p надходить на входи регістру D4 і запам'ятовуються ним. Однократно зафіксована розбіжність кодів зчитаних та еталонних даних за допомогою елементів D3.1-D3.p фіксує одиничний стан тих розрядів, в яких зафіксована помилка. Керування режимом роботи регістрів U1 і D4 здійснюється за допомогою кодів мікрооперацій, що надходять від пам'яті інструкцій 9 і контролера послідовності інструкцій 10. Результати тестування через багатовхідний елемент І D5, через буфер D6 передаються на вивід Т1 і використовуються для визначення працездатного стану мікросхеми. На Фіг.7 наведена структурна схема програмного лічильника, який складається з логічних елементів D1-D3, D6-D9, тригера D5 і лічильника D4. Тригер D5 фіксує стан мікросхеми, при якому здійснюється самотестування, і перемикається в одиничний стан при надходженні стартового сигналу ST. Тригер D5 перемикається в нульовий стан при досягненні лічильником D4 станів "1111" або "1110", що фіксується елементами D6-D9. При цьому стан "1111" відповідає виявлення відмов в 9 мікросхемі, що тестується, і вона вважається забракованою. На вивід ТІ при цьому видається сигнал високого рівня напруги. Стан "1110" лічильника D4 відповідає події, коли в мікросхемі, що тестується, відмов не виявлено і вона вважається справною. На виводі Т1 мікросхеми залишається напруга низького рівня. Коди з виходів лічильника D4 передаються на входи пам'яті інструкцій 9, яка виконана у вигляді постійного запам'ятовуючого пристрою і забезпечує формування послідовності мікрокоманд в процесі самотестування мікросхеми. На Фіг.8 наведена структурна схема контролера послідовності інструкцій 10, яка складається з дешифратора D1, логічних елементів D2-D5 та тригера D6. Коди з виходів програмного лічильника 8 надходять на входи дешифратора D1, який дешифрує стан процесу самотестування і видає сигнали високого рівня напруги на перші входи елементу D2, на другі входи якого надходять умови переходів, що надходять з виходів лічильників К, L, АЛП адреси 11, компаратора даних 16. Формування режиму паралельного запису кодів адреси переходів лічильника D4 (Фіг.7) забезпечують логічні елементи D2, D3, D5 та тригер D6 (Фіг.8). Сигнал з виходу тригера D6 надходить на вхід Load лічильника D4 (Фіг.7) і забезпечує перемикання даного лічильника в режим паралельного занесення для реалізації мікрокоманд умовного переходу. Алгоритм роботи мікросхеми пам'яті в режимі самотестування наведено на Фіг.9. На початку встановлюються лічильники К і L в нульовий стан k=l=0, потім обирається початкова адреса масиву комірок пам'яті (0 A), в регістр контрольних даних заноситься код двохмірних функцій Уолша (F T) й здійснюється запис інформації (Т IС) в 47842 10 обрану комірку. Значення регістра поточної адреси збільшується на одиницю (А+1 А) і аналогічним чином здійснюється запис кодів двохмірних функцій Уолша в усі комірки пам'яті. Далі знову встановлюється початкова адреса масиву комірок пам'яті, код двохмірних функцій Уолша запам'ятовується в регістрі еталонних даних, здійснюється зчитування обраної комірки (1С М) та порівняння даних (Т=M). Операції повторюються для всіх комбінацій k, l. Для формування інверсних даних тест повторюється двічі. За станом напруги на виводі Т1 ідентифікується стан мікросхеми. За наявності високого рівня на виводі Т1 мікросхема вважається непрацездатною. Загальна тривалість самотестування складає 64n циклів операцій звертання, де n - ємність масиву комірок пам'яті. Наприклад, тривалість тестування мікросхеми пам'яті ємністю 64Мбіт з часом циклу звертання рівним 30 нc. за допомогою заявленої моделі складає 2 с. Техніко-економічні ефект при застосуванні заявленої моделі досягається за рахунок підвищення надійності мікросхем напівпровідникової пам'яті на етапі їх виготовлення за рахунок збільшення числа сполучень кодів даних в суміжних запам'ятовуючих комірках, що забезпечує виявлення відмов та збоїв, викликаних взаємним впливом комірок пам'яті. Література: 1. Патент США. Built-in self repair circuitry utilizing permanent record of defects. N6651202B1, Int.Cl.G01R 31/28, Nov.18,2003. 2. Патент США. Semiconductor integrated circuit and method for testing memory. N6233182B1, Int.C1.G11C 7/00. May 15, 2001. 11 47842 12 13 47842 14 15 Комп’ютерна верстка Л. Купенко 47842 Підписне 16 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюIntegrated circuit of semiconductor memory with built-in self-testing capabilities

Автори англійськоюUtkina Tetiana Yuriivna, Riabtsev Volodymyr Hryhorovych, Andrienko Volodymyr Oleksandrovych

Назва патенту російськоюМикросхема полупроводниковой памяти со встроенными средствами самотестирования

Автори російськоюУткина Татьяна Юрьевна, Рябцев Владимир Григорьевич, Андриенко Владимир Александрович

МПК / Мітки

МПК: G11C 7/00

Мітки: вбудованими, мікросхема, напівпровідникової, засобами, самотестування, пам'яті

Код посилання

<a href="https://ua.patents.su/8-47842-mikroskhema-napivprovidnikovo-pamyati-z-vbudovanimi-zasobami-samotestuvannya.html" target="_blank" rel="follow" title="База патентів України">Мікросхема напівпровідникової пам`яті з вбудованими засобами самотестування</a>

Попередній патент: Автономне джерело енергії

Наступний патент: Трансформоване накриття вантажної платформи автомобіля-пікапа

Випадковий патент: Пристрій для вимірювання електричного сигналу з адитивною завадою