Мікросхема напівпровідникової пам’яті з вбудованими засобами самотестування та захистом від перегрівання

Номер патенту: 56581

Опубліковано: 25.01.2011

Автори: Андрієнко Володимир Олександрович, Рябцев Володимир Григорович, Уткіна Тетяна Юріївна

Формула / Реферат

Мікросхема напівпровідникової пам'яті з вбудованими засобами самотестування та захистом від перегрівання, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора адреси X і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних Data мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мікрокоманд, входи якої підключені до перших виходів програмного лічильника, перший вхід якого підключено до входу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мікрокоманд, треті виходи пам'яті мікрокоманд підключені до перших входів арифметико-логічного пристрою (АЛП) адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключено до виходу Т1 мікросхеми, на який видається результат тестування, другий вихід компаратора даних підключено до другого входу контролера послідовності мікрокоманд, перші входи комутатора адреси X і комутатора адреси Y підключені до виходів буфера адреси, входи якого є адресними входами AD мікросхеми, другі і треті виходи АЛП адреси підключені до других входів комутатора адреси X і комутатора адреси Y відповідно, перші виходи контролера послідовності мікрокоманд підключені до других входів програмного лічильника, а група виходів контролера послідовності мікрокоманд використовується для управління режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми підключені до виводів мікросхеми, на які подаються управляючі сигнали CS, AS, WE, OE, а виходи даного контролера використовуються для видачі сигналів, які визначають режими роботи мікросхеми, яка відрізняється тим, що в неї додатково введені таймер паузи, буферний елемент і вхід для подачі синхронізуючого сигналу CLK, причому перший вхід таймера паузи підключено до другого виходу програмного лічильника, другий вхід таймера паузи, третій вхід програмного лічильника і третій вхід контролера послідовності мікрокоманд підключені до виходу буферного елемента, вхід якого підключено до входу CS мікросхеми, входи AD мікросхеми підключені до входів буфера адреси і третіх входів таймера паузи, четвертий вхід якого підключено до другого виходу контролера послідовності мікрокоманд, третій вихід якого підключено до третіх входів АЛП адреси, АЛП даних, компаратора даних, шостого входу програмного лічильника і четвертого входу таймера паузи, вихід якого підключено до других входів АЛП адреси, АЛП даних і четвертого входу програмного лічильника, шості входи якого підключені до четвертих виходів пам'яті мікрокоманд, вивід CLK мікросхеми підключено до п'ятого входу контролера послідовності мікрокоманд.

Текст

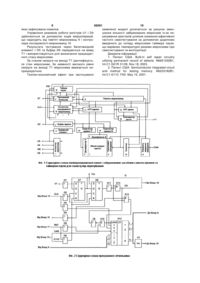

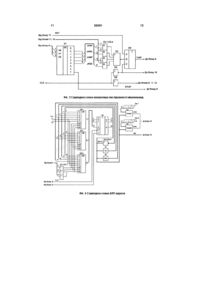

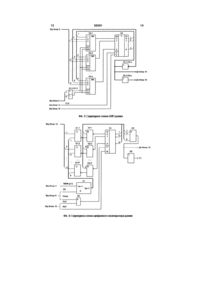

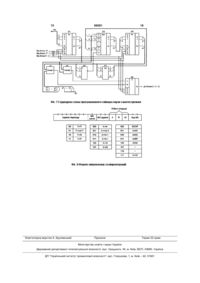

Мікросхема напівпровідникової пам'яті з вбудованими засобами самотестування та захистом від перегрівання, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора адреси X і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних Data мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мікрокоманд, входи якої підключені до перших виходів програмного лічильника, перший вхід якого підключено до входу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мікрокоманд, треті виходи пам'яті мікрокоманд підключені до перших входів арифметико-логічного пристрою (АЛП) адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключено до виходу Т1 мікросхеми, на який видається результат тестування, другий вихід компаратора даних підключено до другого входу контролера послідо U 2 (19) 1 3 56581 4 ної реєстрації дефектів, яка містить запам'ятовуюгі виходи АЛП даних підключені до других входів чий масив комірок з контролером резервних елекомпаратора даних, перший вихід якого підключементів, вбудовані засоби самотестування, які но до виводу Т1 мікросхеми, на який видається складаються з контролера станів цифрового авторезультат тестування, другий вихід компаратора мату, генератора адреси, генератора даних і комуданих підключено до другого входу контролера татора, а також регістра несправностей, модуля послідовності мікрокоманд, перші входи комутаторемонту й регістру сканування [1]. ра адреси X і комутатора адреси Y підключені до Недоліком даної мікросхеми є можливість певиходів буфера адреси, входи якого є адресними ревищення максимально допустимої температури входами AD мікросхеми, другі і треті виходи АЛП кристалу при самотестуванні масиву запам'ятовуадреси підключені до других входів комутатора ючих комірок великої ємності, що приводить до адреси X і комутатора адреси Y відповідно, перші виникнення нових дефектів. виходи контролера послідовності мікрокоманд Найбільш близьким до запропонованого є мепідключені до других входів програмного лічильнитод тестування пам'яті і інтегральна напівпровідка, а група виходів контролера послідовності мікникова мікросхема [2], яка містить масив пам'яті, рокоманд використовується для управління режидешифратор адреси X, дешифратор адреси Y, мами роботи основних компонентів мікросхеми, підсилювачі зчитування, буфер адреси, елементи що забезпечують виконання самотестування, вховведення/виведення, контролер мікросхеми, проди контролера мікросхеми підключені до виводів грамний лічильник, пам'ять мікрокоманд, контромікросхеми, на які подаються управляючи сигнали лер послідовності мікрокоманд, АЛП адреси, АЛП CS, AS, WE, OE, а виходи даного контролера виданих, комутатор адреси X, комутатор адреси Y, користовуються для видачі сигналів, які визначакомпаратор, що здійснює порівняння даних. ють режими роботи мікросхеми, додатково введені Недоліком даної мікросхеми є можливість її таймер паузи, буферний елемент і вхід для подачі перегрівання, оскільки самотестування виконуєтьсинхронізуючого сигналу CLK, причому перший ся без пропусків тактів звертання до мікросхеми, а вхід таймера паузи підключено до другого виходу в реальному режимі експлуатації виникають паузи програмного лічильника, другий вхід таймера паув роботі мікросхеми для обробки даних процесози, третій вхід програмного лічильника і третій вхід ром. Додаткові дефекти, які виникають через переконтролера послідовності мікрокоманд підключені грівання кристалів при виконанні самотестування, до виходу буферного елементу, вхід якого підклюзнижують відсоток виходу придатних виробів. чено до входу CS мікросхеми, входи AD мікросхеЗ метою усунення даного недоліку необхідно ми підключені до входів буфера адреси і третіх до складу мікросхеми включити додаткові апаратні входів таймера паузи, четвертий вхід якого підкзасоби, які забезпечують зниження ефективної лючено до другого виходу контролера послідовночастоти самотестування, що дозволить виключити сті мікрокоманд, третій вихід якого підключено до перегрівання кристалів. третіх входів АЛП адреси, АЛП даних, компаратоМета корисної моделі - забезпечення захисту ра даних, шостого входу програмного лічильника і мікросхеми напівпровідникової пам'яті від перегрічетвертого входу таймера паузи, вихід якого підквання кристалу шляхом зниження ефективної часлючено до других входів АЛП адреси, АЛП даних і тоти самотестування за допомогою включеної до четвертого входу програмного лічильника, шості складу мікросхеми таймера паузи, що забезпечує входи якого підключені до четвертих входів пам'яті однаковий температурний режим мікросхеми при мікрокоманд, вхід CLK мікросхеми підключено до самотестуванні та при експлуатації. п'ятого входу контролера послідовності мікрокоВказана мета досягається тим, що в мікросхеманд. му напівпровідникової пам'яті, яка містить масив В основу запропонованої мікросхеми пам'яті комірок пам'яті, оснащений дешифраторами адрепоставлена задача забезпечення захисту кристалу си X, Y, входи яких підключені до виходів комутавід перегрівання шляхом зниження ефективної тора адреси X і комутатора адреси Y відповідно, і частоти самотестування за допомогою додатково підсилювачами зчитування, входи/виходи яких введеного до складу мікросхеми таймера паузи, підключені до перших входів/виходів селектора і що вирівнює температурні режими мікросхеми при перших входів компаратора даних, другі вхосамотестуванні та експлуатації, оскільки пропуски ди/виходи селектора підключені до перших вхотактів звертання до мікросхеми пам'яті забезпечудів/виходів елементів введення/виведення, другі ються наявністю тактів обробки зчитуваних даних входи/виходи яких підключені до виходів даних процесором. Data мікросхеми, треті входи елементів введенТаким чином, запропоноване рішення задовоня/виведення і другі входи підсилювачів зчитуванльняє критерію "істотні відмінності". ня підключені до перших виходів пам'яті мікрокоНа фіг. 1 приведена структурна схема напівпманд, входи якої підключені до перших виходів ровідникової пам'яті з вбудованими засобами сапрограмного лічильника, перший вхід якого підкмотестування та таймером паузи для захисту від лючено до входу мікросхеми, на який подається перегрівання. стартовий сигнал ST, другі виходи пам'яті мікрокоНа фіг. 2 зображена структурна схема програманд підключені до перших входів контролера много лічильника. послідовності мікрокоманд, треті виходи пам'яті На фіг. 3 приведена структурна схема контромікрокоманд підключені до перших входів АЛП лера послідовності мікрокоманд. адреси, четверті виходи пам'яті мікрокоманд підкНа фіг. 4 зображена структурна схема АЛП лючені до перших входів АЛП даних, перші виходи адреси. якого підключені до третіх входів селектора, а друНа фіг. 5 приведена структурна схема АЛП 5 56581 6 даних. ролера послідовності мікрокоманд 10, третій вихід На фіг. 6 зображена структурна схема цифроякого підключено до третіх входів АЛП адреси 11, вого компаратора даних. АЛП даних 12, компаратора даних 16, шостого На фіг. 7 приведена структурна схема програвходу програмного лічильника 8 і четвертого входу мованого таймера паузи самотестування. таймера паузи 18, вихід якого підключено до друНа фіг. 8 зображено формат мікрокоманд та гих входів АЛП адреси 11, АЛП даних 12 і четвермікрооперацій. того входу програмного лічильника 8, шості входи На фіг. 1 приведена структурна схема напівпякого підключені до четвертих виходів пам'яті мікровідникової пам'яті з вбудованими засобами сарокоманд 9, вивід CLK мікросхеми підключено до мотестування та таймером паузи для захисту від п'ятого входу контролера послідовності мікрокоперегрівання, яка містить масив комірок пам'яті 1, манд 10. оснащений дешифратором адреси X2 і дешифраНа фіг. 2 зображена структурна схема програтором адреси Y3, входи яких підключені до виходів много лічильника, який складається з логічних комутатора адреси X14 і комутатора адреси Y13 елементів D1-D6, D9-D11, D13, D14, D-тригерів D7, відповідно, і підсилювачі зчитування 4, вхоD8, лічильника D12 та інкрементора А1. При подади/виходи яких підключені до перших вхочі сигналу ST на вхід програмного лічильника тридів/виходів селектора 15 і перших входів компарагери D7, D8 перемикаються в одиничний стан і на тора даних 16, другі входи/виходи селектора 15 виході елемента D13 формується одиничний імпідключені до перших входів/виходів елементів пульс, який використовується для запису коду, що введення/виведення 6, другі входи/виходи яких надходить з виходів AD мікросхеми, до регістра підключені до виходів даних Data мікросхеми, треті пускової адреси 18. Одиничний імпульс з виходу входи елементів введення/виведення 6 і другі вхоелемента D13 перемикає комутатор D10 для педи підсилювачів зчитування 4 підключені до перредачі коду з виходів регістра пускової адреси 18 ших виходів пам'яті мікрокоманд 9, входи якої підна входи лічильника D4. Одиничний імпульс з виключені до перших виходів програмного ходу елемента D13 перемикає лічильник D12 в лічильника 8, перший вхід якого підключено до режим паралельного занесення коду пускової адвиходу мікросхеми, на який подається стартовий реси, що заноситься до лічильника D12 по передсигнал ST, другі виходи пам'яті мікрокоманд 9 підньому фронту синхронізуючого сигналу CLK. Лічиключені до перших входів контролера послідовнольник D12 знову перемикається в режим сті мікрокоманд 10, треті виходи пам'яті мікрокопаралельного занесення коду, якщо від контролеманд 9 підключені до входів АЛП адреси 11, ра послідовності мікрокоманд 10 надходить сигнал четверті виходи пам'яті мікрокоманд 9 підключені Load. За наявності сигналу Load до лічильника до перших входів АЛП даних 12, перші виходи D12 заноситься код адреси переходу, який надхоякого підключені до третіх входів селектора 15, а дить з виходів пам'яті мікрокоманд 9. другі виходи АЛП даних 12 підключені до других На фіг. 3 приведена структурна схема контровходів компаратора даних 16, перший вихід якого лера послідовності мікрокоманд 10, який складапідключено до виходу Т1 мікросхеми, на який виється з дешифратора D1, логічних елементів D2.1дається результат тестування, перші входи комуD2.4, D3-D5 та тригера D6, який перемикається в татора адреси X14 і комутатора адреси Y13 підкодиничний стан за сигналом CS, що надходить на лючені до виходів буфера адреси 5, входи якого є вхід S через буферний елемент 17. При надхоадресними входами AD, другі і треті виходи АЛП дженні на входи дешифратора D1 мікрокоманди з адреси 11 підключені до других входів комутатора набору JANN, JANG, JKNZ й відповідної їм умови адреси X14 і комутатора адреси Y13 відповідно, тригер D6 перемикається в нульовий стан та форперші виходи контролера послідовності мікрокомує на виході сигнал Load низьким рівнем напруги. манд 10 підключені до других входів програмного При надходженні мікрокоманди безумовного перелічильника 8, а група виходів контролера послідоходу (JUMP) тригер D6 також перемикається в вності мікрокоманд 10 використовується для нульовий стан, що забезпечує занесення коду адуправління режимами роботи основних компоненреси переходу до програмного лічильника 8. тів мікросхеми, що забезпечують виконання самоНа фіг. 4 зображена структурна схема АЛП тестування, входи контролера мікросхеми 7 підкадреси, який складається з логічних елементів лючені до виходів мікросхеми, на які подаються D1.1-D1.3, D4.1-D1.m, мультиплексорів D2.1-D2.m, управляючи сигнали CS, AS, WE, OE, а виходи регістра D3, інкрементора А1, декрементора А2, даного контролера мікросхеми 7 використовуютькомпараторів Comp1, Comp2. Коди з виходів пася для видачі сигналів, які визначають режими м'яті мікрокоманд 9 надходять на входи АЛП адрероботи мікросхеми, яка також містить таймер пауси і забезпечують формування наступних мікроози 18, буферний елемент 17 і вхід для подачі синперацій: A:=A,A'=not A,A:=A + 1,A:=:A-1,A:=N,A:=G, хронізуючого сигналу CLK, причому перший вхід де А - поточний код адреси, N - код кінцевої адретаймера паузи 18 підключено до другого виходу си комірок пам'яті, G - код початкової адреси коміпрограмного лічильника 8, другий вхід таймера рок пам'яті. Компаратор Comp1 формує прапор паузи 18, третій вхід програмного лічильника 8 і переходу A = N, комутатор Соmр2 - ознака перетретій вхід контролера послідовності микрокоманд ходу A = G, які використовуються контролером 10 підключені до виходу буферного елемента 17, послідовності мікрокоманд 10 для реалізації мікровхід якого підключено до входу CS мікросхеми, команд умовного переходу. входи AD мікросхеми підключені до входів буфера На фіг. 5 приведена структурна схема АЛП адреси 5 і третіх входів таймера паузи 18, четверданих, який складається з логічних елементів тий вхід якого підключено до другого виходу контD1.1-D1.2, D4.1-D4.p, D5.1-D5.p, мультиплексорів 7 56581 8 D2.1-D2.p і регістра D3. Коди з виходів пам'яті мікрокоманд 9 надходять на входи АЛП даних і забезпечують формування наступних робочих операцій: Т :=Т,Т' := not Т, Т := S, де S - код занесення даних, які надходять з виходів пам'яті мікрокоманд 9. Коди даних запам'ятовуються регістром D3 і передаються на виходи АЛП даних 12. На фіг. 6 зображена структурна схема цифрового компаратора даних 16, що містить елементи При виконанні тесту MarchC відбувається 10n HE-ВИКЛЮЧАЮЧЕ АБО D1.1-D1.p, 2І D2, 2І-НІ циклів звертання до масиву комірок пам'яті: 5n D3.1-D3.p, регістр D4, багатовхідний елемент І D5, циклів для запису та 5n циклів для зчитування. буферний елемент D6 та регістр U1. Мікросхема напівпровідникової пам'яті працює На фіг. 7 приведена структурна схема програнаступним чином. Для ініціалізації мікросхеми на мованого таймера паузи самотестування, який вхід CS подається сигнал високого рівня напруги, складається з регістрів D1, D4, логічного елемента який через буферний елемент 17 забезпечує D2, мультиплексора D3, компараторів А1, А2, інвстановлення в початковий стан усіх компонентів крементора A3 та JK-тригера D5. мікросхеми, що забезпечують виконання самотесНа фіг. 8 зображено формат мікрокоманд і мітування. Після подачі стартового сигналу на вхід крооперацій, який складається з наступних полів: SТ мікросхеми на виході програмного лічильника 8 - коду мікрокоманди; формується одиночний імпульс, який забезпечує - робочих мікрооперацій запису (W), зчитуванзанесення двійкового коду з входів AD мікросхеми ня (R), порівняння (А); до реперу D1 таймера паузи 18. Вміст даного регі- коду мікрооперацій адреси; стру визначає період роботи таймера паузи 18. У - коду мікрооперацій даних; наступному такті вміст регістру D1 заноситься до - адреси переходу. регістру D4, який завдяки інкрементору A3 та муДля формування тестів використовуються нальтиплексору D3 виконує функцію лічильника імступні мікрокоманди: пульсів синхронізуючого сигналу CLK. NOOP - відсутність операції, забезпечує переПри рівності кодів, занесених в регістри D1 і хід до наступної мікрокоманди; D4 таймера 18 на виході компаратора А2 формуJANN - перехід до команди, код адреси якої ється сигнал високого рівня напруги, що забезпезаписано у полі адреси переходу, якщо поточна чує перемикання в одиничний стан трігера D5 та адреса комірок пам'яті не дорівнює адресі кінцевої блокування вбудованих компонентів самотестукомірки (AN); вання мікросхеми. Потім завдяки інкрементору A3 і JANG - перехід до команди, код адреси якої мультиплексору D3 вміст регістра D4 зменшується записано у полі адреси переходу, якщо поточна на одиницю в кожному такті синхронізуючого сигадреса комірок пам'яті не дорівнює адресі початналу CLK. При збігу кодів на входах компаратора кової комірки (AG); А1 на його виході формується сигнал високого JUMP - безумовний перехід до команди, код рівня напруги, що забезпечує перемикання тригеадреси якої записано у полі адреси переходу; ра D5 в нульовий стан й дозволяє роботу вбудоJKNZ - умовний перехід до команди, адреса ваних компонентів самотестування. переходу якої записана у полі адреси переходу, Тривалість імпульсу на виході тригера D5 тайякщо при порівнянні зчитаних даних з еталонними мера паузи 18 пропорційна кількості входів р, які значеннями виявлена розбіжність кодів (К0); підключені до загального виводу джерела електSTOP - зупинка виконання тесту. роживлення. При цьому ефективна частота самоПриклад програми тесту: MarchC наведено 2p нижче. тестування мікросхеми знижується на 100 % , 2m де m - кількість розрядів регістрів D1 і D4. Змінюючи код на входах AD при ініціалізації мікросхеми або число розрядів р, підключених до загального виводу, при виготовленні мікросхеми можна забезпечити досягнення допустимого теплового режиму мікросхеми пам'яті при самотестуванні, що виключить вихід з ладу мікросхем від перегрівання кристала. При виконанні самотестування зчитані дані з виходів підсилювачів зчитування 4 надходять на входи регістра U1 компаратора даних 16 і запам'ятовуються ним. Еталонні дані надходять з виходів АЛП даних 12. Порівняння кодів здійснюють елементи HE-ВИКЛЮЧАЮЧЕ АБО D1.1-D1.p. Результат порівняння через елементи D3.1-D3.p надходить на входи регістру D4 і запам'ятовується ним. Однократно зафіксована розбіжність кодів зчитаних та еталонних даних за допомогою елементів D3.1-D3.p фіксує одиничний стан тих розрядів, в 9 56581 10 яких зафіксована помилка. заявленої моделі досягається за рахунок зменУправління режимом роботи регістрів U1 і D4 шення кількості забракованих мікросхем Із-за пездійснюється за допомогою кодів мікрооперацій, регрівання кристалів шляхом зниження ефективної що надходять від пам'яті мікрокоманд 9 і контрочастоти самотестування за допомогою додатково лера послідовності мікрокоманд 10. введеного до складу мікросхеми таймера паузи, Результати тестування через багатовхідний що вирівнює температурні режими мікросхеми при елемент І D5 та буфер D6 передаються на вивід самотестуванні та експлуатації. Т1 і використовуються для визначення працездатДжерела інформації: ного стану мікросхеми. 1. Патент США. Built-in self repair circuitry За станом напруги на виході Т1 ідентифікуєтьutilizing permanent record of defects. N6651202B1, ся стан мікросхеми. За наявності високого рівня Int.C1.G01R 31/28, Nov.18, 2003. напруги на виході Т1 мікросхема вважається не2. Патент США. Semiconductor integrated circuit працездатною. and method for testing memory. N6233182B1, Техніко-економічний ефект при застосуванні Int.C1.G11С 7/00. May 15, 2001. 11 56581 12 13 56581 14 15 Комп’ютерна верстка А. Крулевський 56581 Підписне 16 Тираж 23 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюSemiconductor memory microcircuit chip with built-in for self-testing and protection agaginst overheat

Автори англійськоюAndrienko Volodymyr Oleksandrovych, Riabtsev Volodymyr Hryhorovych, Utkina Tetiana Yuriivna

Назва патенту російськоюМикросхема полупроводниковой памяти co встроенными средствами самотестирования и защитой ot перегревания

Автори російськоюАндриенко Владимир Александрович, Рябцев Владимир Григорьевич, Уткина Татьяна Юрьевна

МПК / Мітки

МПК: G11C 7/00

Мітки: пам'яті, напівпровідникової, вбудованими, засобами, захистом, самотестування, перегрівання, мікросхема

Код посилання

<a href="https://ua.patents.su/8-56581-mikroskhema-napivprovidnikovo-pamyati-z-vbudovanimi-zasobami-samotestuvannya-ta-zakhistom-vid-peregrivannya.html" target="_blank" rel="follow" title="База патентів України">Мікросхема напівпровідникової пам’яті з вбудованими засобами самотестування та захистом від перегрівання</a>

Попередній патент: Імпульсно-запобіжний пристрій

Наступний патент: Адсорбер з поглиначем у вигляді перевернутого глухого циліндра

Випадковий патент: Спосіб отримання наноматеріалу з біоцидними властивостями "шумерське срібло"