Мікросхема напівпровідникової пам’яті з вбудованими засобами багатоверсійного самотестування

Номер патенту: 49179

Опубліковано: 26.04.2010

Автори: Андрієнко Володимир Олександрович, Рябцев Володимир Григорович, Уткіна Тетяна Юріївна

Формула / Реферат

Мікросхема напівпровідникової пам'яті з вбудованими засобами багатоверсійного самотестування, що містить масив комірок пам'яті, оснащений дешифраторами адреси X,Y, входи яких підключені до виходів комутатора адреси Х і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мікрокоманд, входи якої підключені до перших виходів програмного лічильника, перший вхід якого підключено до виходу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мікрокоманд, треті виходи пам'яті мікрокоманд підключені до входів арифметико-логічного пристрою (АЛП) адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключено до виходу Т1 мікросхеми, на який видається результат тестування, перші входи комутатора адреси Х і комутатора адреси Y підключені до виходів буфера адреси, входи якого є адресними входами AD, другі і треті виходи АЛП адреси підключені до других входів комутатора адреси Х і комутатора адреси Y відповідно, перші виходи контролера послідовності мікрокоманд підключені до других входів програмного лічильника, а група виходів контролера послідовності мікрокоманд використовується для керування режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми підключені до виходів мікросхеми, на які подаються керуючі сигнали CS, AS, WE, OE, а виходи даного контролера використовуються для видачі сигналів, які визначають режими роботи мікросхеми, яка відрізняється тим, що в неї додатково введені стек, регістр пускової адреси, буферний елемент і вхід для подачі синхронізуючого сигналу CLK, причому перші входи стеку підключені до других виходів контролера послідовності мікрокоманд, другі входи стеку підключені до других виходів програмного лічильника, виходи стеку підключені до третіх входів програмного лічильника, треті виходи якого підключені до других входів контролера послідовності мікрокоманд, вхід буферного елемента підключено до виходу CS мікросхеми, а вихід буферного елемента підключено до третього входу контролера послідовності мікрокоманд, третього входу програмного лічильника і третього входу стеку, входи AD мікросхеми підключені до перших входів регістра пускової адреси, четверті виходи програмного лічильника підключені до третіх входів регістра пускової адреси, другі виходи якого підключені до п'ятих входів програмного лічильника, третій вихід АЛП адреси підключено до другого входу АЛП даних, п'ятий вихід пам'яті мікрокоманд підключено до третього входу комутатора даних, треті виходи якого підключені до других входів контролера послідовності мікрокоманд, вхід буферного елемента підключено до входу CS мікросхеми, а вихід буферного елемента підключено до третього входу контролера послідовності мікрокоманд, третього входу програмного лічильника і третього входу стеку, входи AD мікросхеми підключені до перших входів регістра пускової адреси, четверті виходи програмного лічильника підключені до третіх входів регістра пускової адреси, другі виходи якого підключені до п'ятих входів програмного лічильника, третій вихід АЛП адреси підключено до другого входу АЛП даних, п'ятий вихід пам'яті мікрокоманд підключено до третього входу компаратора даних, другий вихід якого підключено до третього входу контролера послідовності мікрокоманд, третій вихід якого підключено до другого входу АЛП адреси, третього входу АЛП даних, четвертого входу стеку і четвертого входу компаратора даних, другий вихід якого підключено до четвертого входу контролера послідовності мікрокоманд, п'ятий вхід якого підключено до четвертого виходу АЛП адреси, а шості виходи пам'яті мікрокоманд підключені до четвертих входів програмного лічильника.

Текст

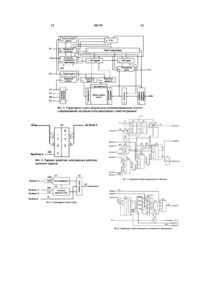

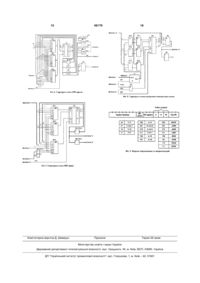

Мікросхема напівпровідникової пам'яті з вбудованими засобами багатоверсійного самотестування, що містить масив комірок пам'яті, оснащений дешифраторами адреси X,Y, входи яких підключені до виходів комутатора адреси Х і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мікрокоманд, входи якої підключені до перших виходів програмного лічильника, перший вхід якого підключено до виходу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мікрокоманд, треті виходи пам'яті мікрокоманд підключені до входів арифметико-логічного пристрою (АЛП) адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключено до виходу Т1 мікросхеми, на який видається результат тестування, перші входи комутатора адреси Х і комутатора адреси Y підключені до виходів буфера адреси, входи якого є адресними входами AD, другі і треті виходи АЛП адреси підключені до других входів комутатора адреси Х і комутатора адреси Y відповідно, перші виходи контролера послідовності мікрокоманд підключені до других входів програмного лічильника, а група виходів контролера послідовності мікрокоманд використовується для керування режимами роботи основних компо З 49179 1 ПАМ'ЯТІ (11) (54) МІКРОСХЕМА НАПІВПРОВІДНИКОВОЇ БАГАТОВЕРСІЙНОГО САМОТЕСТУВАННЯ UA ДЕРЖАВНИЙ ДЕПАРТАМЕНТ ІНТЕЛЕКТУАЛЬНОЇ ВЛАСНОСТІ ОПИС (19) МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ 3 49179 4 компаратора даних, другий вихід якого підключено до четвертого входу контролера послідовності мікрокоманд, п'ятий вхід якого підключено до чет вертого виходу АЛП адреси, а шості виходи пам'яті мікрокоманд підключені до четвертих входів програмного лічильника. Корисна модель відноситься до засобів обчислювальної техніки і може бути використана для побудови напівпровідникових запам'ятовуючих пристроїв, що містять вбудовані засоби для виконання багатоверсійного самотестування, які забезпечують формування кодів адреси, даних, необхідних для запису тестових наборів, зчитування та порівняння даних з еталонними значеннями. Відома мікросхема запам'ятовуючого пристрою з вбудованими засобами ремонту та постійної реєстрації дефектів, яка містить запам'ятовуючий масив з контролером резервних елементів, вбудовані засоби самотестування, які складаються з контролера станів цифрового автомату, генератора адреси, генератора даних І комутатора, а також регістра несправностей, модуля ремонту і регістру сканування [1]. Недоліком даної мікросхеми запам'ятовуючого пристрою є низькі діагностичні властивості тестових дій, набір яких визначається алгоритмом роботи контролера цифрового автомату з кінцевим числом станів. Найбільш близьким до запропонованого є метод тестування пам'яті і інтегральна напівпровідникова мікросхема [2], яка містить масив пам'яті, дешифратор адреси X, дешифратор адреси Y, підсилювачі зчитування, буфер адреси, елементи введення/виведення, контролер схеми, програмний лічильник, пам'ять мІкрокоманд, контролер послідовності мікрокоманд, АЛЛ адреси, АЛЛ даних, комутатор адреси X, комутатор адреси Y, компаратор, що здійснює порівняння даних. Недоліком даної мікросхеми є неможливість зміни програм тестів в убудованих засобах самотестування. Однак на різних етапах життєвого циклу мікросхеми необхідно застосовувати різноманітні тестові набори. Так на етапі виготовлення звичайно використовують тривалі тестові набори, які виявляють велику кількість дефектів. На етапі експлуатації доцільно використовувати тестові набори невеликої тривалості, щоб підвищити коефіцієнт технічної готовності мікросхеми. Для оперативної зміни програм тестів необхідно у складі мікросхеми передбачити додаткові апаратні засоби. Мета корисної моделі - забезпечення оперативної зміни програм тестів для реалізації багатоверсійного діагностування на різних етапах життєвого циклу, що забезпечить виявлення більшості дефектів ще на етапі виготовлення й зменшить витрати часу на виконання тестування на етапі експлуатації. Вказана мета досягається тим, що в інтегральну напівпровідникову мікросхему, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора адреси Х і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора І перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мІкрокоманд, входи якої підключені до перших виходів програмного лічильника, перший вхід якого підключено до виходу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мІкрокоманд, треті виходи пам'яті мікрокоманд підключені до входів АЛЛ адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛЛ даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛЛ даних підключені до других входів компаратора даних, перший вихід якого підключено до виходу ТІ мікросхеми, на який видається результат тестування, перші входи комутатора адреси Х і комутатора адреси Y підключені до виходів буфера адреси, входи якого є адресними входами AD, другі і треті виходи АЛЛ адреси підключені до других входів комутатора адреси Х і комутатора адреси У відповідно, перші виходи контролера послідовності мікрокоманд підключені до других входів програмного лічильника, а група виходів контролера послідовності мікрокоманд використовується для управління режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми підключені до виходів мікросхеми, на які подаються управляючи сигнали CS, AS, WE, OE, а виходи даного контролера використовуються для видачі сигналів, які визначають режими роботи мікросхеми, додатково введені стек, регістр пускової адреси, буферний елемент І вхід для подачі синхронізуючого сигналу CLK, причому перші входи стеку підключені до других виходів контролера послідовності мікрокоманд, другі входи стеку підключені до других виходів програмного лічильника, виходи стеку підключені до третіх входів програмного лічильника, треті виходи якого підключені до других входів контролера послідовності мікрокоманд, вхід буферного елемента підключено до виходу CS мікросхеми, а вихід буферного елемента підключено до третього входу контролера послідовності мікрокоманд, третього входу програмного лічильника і третього входу стеку, входи AD мікросхеми підключені до перших входів регістра пускової адреси, четверті виходи програмного лічильника підключені до третіх входів регістра пускової адреси, другі виходи якого підключені до п'ятих входів програмного 5 лічильника, третій вихід АЛЛ адреси підключено до другого входу АЛЛ даних, п'ятий вихід пам'яті мікрокоманд підключено до третього входу комутатора даних, треті виходи якого підключені до других входів контролера послідовності мікрокоманд, вхід буферного елемента підключено до входу CS мікросхеми, а вихід буферного елемента підключено до третього входу контролера послідовності мікрокоманд, третього входу програмного лічильника і третього входу стеку, входи AD мікросхеми підключені до перших входів регістра пускової адреси, четверті виходи програмного лічильника підключені до третіх входів регістра пускової адреси, другі виходи якого підключені до п'ятих входів програмного лічильника, третій вихід АЛЛ адреси підключено до другого входу АЛЛ даних, п'ятий вихід пам'яті мікрокоманд підключено до третього входу компаратора даних, другий вихід якого підключено до третього входу контролера послідовності мікрокоманд, третій вихід якого підключено до другого входу АЛЛ адреси, третього входу АЛЛ даних, четвертого входу стеку і четвертого входу компаратора даних, другий вихід якого підключено до четвертого входу контролера послідовності мікрокоманд, п'ятий вхід якого підключено до четвертого виходу АЛЛ адреси, а шості виходи пам'яті мікрокоманд підключені до четвертих входів програмного лічильника. В основу запропонованої мікросхеми поставлена задача забезпечення оперативної зміни програм тестів шляхом застосування запропонованого рішення, ознаки якого вказані вчастині формули моделі, яка відрізняється від аналогу І виявляє в процесі взаємодії характерні особливості, які надають позитивний ефект. Таким чином, запропоноване рішення задовольняє критерію "Істотні відмінності". На фіг. 1 наведена структурна схема мікросхеми напівпровідникової пам'яті з вбудованими засобами багатоверсійного самотестування. На фіг. 2 приведено умовне графічне зображення регістра пускової адреси. На фіг. 3 зображена структурна схема стеку. На фіг. 4 приведена структурна схема програмного лічильника. На фіг. 5 зображена структурна схема контролера послідовності мікрокоманд. На фіг. 6 приведена структурна схема АЛЛ адреси. На фіг. 7 зображена структурна схема АЛЛ даних. На фіг. 8 приведена структурна схема цифрового компаратора даних. На фіг. 9 зображено формат мікрокоманд та мікрооперацій. На фіг. 1 наведена структурна схема мікросхеми напівпровідникової пам'яті з вбудованими засобами багатоверсійного самотестування, яка містить масив комірок пам'яті 1, оснащений дешифратором адреси Х 2 і дешифратором адреси Y 3, входи яких підключені до виходів комутатора адреси Х 14 і комутатора адреси Y 13 відповідно, і підсилювачі зчитування 4, входи/виходи яких підключені до перших 49179 6 входів/виходів селектора 15 і перших входів компаратора даних 16, другі входи/виходи селектора 15 підключені до перших входів/виходів елементів введення/виведення 6, другі входи/виходи яких підключені до виходів даних Data мікросхеми, треті входи елементів введення/виведення 6 і другі входи підсилювачів зчитування 4 підключені до перших виходів пам'яті мікрокоманд 9, входи якої підключені до перших виходів програмного лічильника 8, перший вхід якого підключено до виходу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд 9 підключені до перших входів контролера послідовності мікрокоманд 10, треті виходи пам'яті мікрокоманд 9 підключені до входів АЛЛ адреси 11, четверті виходи пам'яті мікрокоманд 9 підключені до перших входів АЛЛ даних 12, перші виходи якого підключені до третіх входів селектора 15, а другі виходи АЛЛ даних 12 підключені до других входів компаратора даних 16, перший вихід якого підключено до виходу ТІ мікросхеми, на який видається результат тестування, перші входи комутатора адреси Х 14 І комутатора адреси Y 13 підключені до виходів буфера адреси 5, входи якого є адресними входами AD, другі і треті виходи АЛЛ адреси 11 підключені до других входів комутатора адреси X 14 і комутатора адреси У ІЗ відповідно, перші виходи контролера послідовності мікрокоманд 10 підключені до других входів програмного лічильника 8, а група виходів контролера послідовності мікрокоманд 10 використовується для управління режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми 7 підключені до виходів мікросхеми, на які подаються управляючи сигнали CS, AS, WE, OE, а виходи даного контролера мікросхеми 7 використовуються для видачі сигналів, які визначають режими роботи мікросхеми, яка також містить стек 19, регістр пускової адреси 18, буферний елемент 17 і вхід для подачі синхронізуючого сигналу CLK, причому перші входи стеку 19 підключені до других виходів контролера послідовності мікрокоманд 10, другі входи стеку 19 підключені до других виходів програмного лічильника 8, виходи стеку 19 підключені до третіх входів програмного лічильника 8, треті виходи якого підключені до других входів контролера послідовності мікрокоманд 10, вхід буферного елемента 17 підключено до входу CS мікросхеми, а вихід буферного елемента підключено до третього входу контролера послідовності мікрокоманд 10, третього входу програмного лічильника 8 і третього входу стеку 19, входи AD мікросхеми підключені до перших входів регістра пускової адреси 18, четверті виходи програмного лічильника 8 підключені до третіх входів регістра пускової адреси 18, другі виходи якого підключені до п'ятих входів програмного лічильника 8, третій вихід АЛЛ адреси 11 підключено до другого входу АЛЛ даних 12, п'ятий вихід пам'яті мікрокоманд 9 підключено до третього входу компаратора даних 16, треті виходи якого підключені до других входів контролера послідовності мікрокоманд 10, вхід буферного 7 елемента 17 підключено до входу CS мікросхеми, а вихід буферного елемента 17 підключено до третього входу контролера послідовності мікрокоманд 10, третього входу програмного лічильника 8 і третього входу стеку 19, входи AD мікросхеми підключені до перших входів регістра пускової адреси 18, четверті виходи програмного лічильника 8 підключені до третіх входів регістра пускової адреси 18, другі виходи якого підключені до п'ятих входів програмного лічильника 8, третій вихід АЛЛ адреси 11 підключено до другого входу АЛЛ даних 12, п'ятий вихід пам'яті мікрокоманд 9 підключено до третього входу компаратора даних 16, другий вихід якого підключено до третього входу контролера послідовності мікрокоманд 10, третій вихід якого підключено до другого входу АЛЛ адреси 11, третього входу АЛЛ даних 12, четвертого входу стеку 19 і четвертого входу компаратора даних 16, другий вихід якого підключено до четвертого входу контролера послідовності мікрокоманд 10, п'ятий вхід якого підключено до четвертого виходу АЛЛ адреси 11, а шості виходи пам'яті мікрокоманд підключені до четвертих входів програмного лічильника 8. На фіг. 2 приведено умовне графічне зображення регістра пускової адреси. Код, що надійшов з входів AD мікросхеми, заноситься в регістр D1 і передається на входи програмного лічильника 8, де використовується в якості пускової адреси. На фіг. 3 зображена структурна схема стеку, що складається з пам'яті стеку, лічильника вершини стеку й блоку управління. За мікрокоманди "Виклик підпрограми" (JSUB) лічильник вершини стеку збільшується на одиницю і до пам'яті стеку заноситься код адреси повернення з підпрограми. За мікрокоманди "Вихід з підпрограми" (RSUB) вміст пам'яті стеку передається до програмного лічильника 8, а вміст лічильника вершини стеку зменшується на одиницю. На фіг. 4 приведена структурна схема програмного лічильника, який складається з логічних елементів D1-D3, D5, D9, D11-D13, комутаторів D6, D10, D-тригерів D7, D8, лічильника D4 та інкрементора А1. При подачі сигналу ST на вхід програмного лічильника тригери D7, D8 перемикаються в одиничний стан й на виході елемента D13 формується одиничний імпульс, який використовується для запису коду, що надходить з виходів AD мікросхеми, до регістра пускової адреси 18. Одиничний імпульс з виходу елемента D13 перемикає комутатор D10 для передачі коду з виходів регістра пускової адреси 18 на входи лічильника D4. Одиничний імпульс з виходу елемента D13 перемикає лічильник D4 в режим паралельного занесення коду пускової адреси, який заноситься до лічильника D4 по передньому фронту синхронізуючого сигналу CLK. Лічильник D4 знову перемикається в режим паралельного занесення коду, якщо від контролера послідовності мікрокоманд 10 надходить сигнал Load або мікрокоманда "Вихід з підпрограми" (RSUB). За наявності сигналу Load до лічильника D4 через комутатори D6 та D10 заноситься код адреси переходу, який надходить з виходів пам'яті мікрокоманд 9. А при надходженні мІкрокоманди 49179 8 RSUB через комутатори D6 та D10 до лічильника D4 заноситься код адреси виходу з підпрограми, який надходить з виходів стеку 19. На фіг. 5 зображена структурна схема контролера послідовності мікрокоманд 10, який складається з дешифратора D1, логічних елементів D2.1-D2.5, D3-D5 та тригера D6, який перемикається в одиничний стан за сигналом CS, що надходить на вхід S через буферний елемент 17. При надходженні на входи дешифратора D1 мІкрокоманди з набору JANN, JANG, JKNZ й відповідної їм умови тригер D6 перемикається в нульовий стан та формує на виході сигнал Load низьким рівнем напруги. При надходженні мікрокоманди безумовного переходу (JUMP) або мІкрокоманди "Виклик підпрограми" (RSUB) тригер D6 також перемикається в нульовий стан, що забезпечує занесення коду адреси переходу до програмного лічильника 8. На фіг. 6 приведена структурна схема АЛЛ адреси, який складається з логічних елементів D1.1D1.3, D4.1-Dl.rn, мультиплексорів D2.1-D2.m, регістра D3, інкрементора А1, декрементора А2, компараторів Cornp1, Cornp2 та схеми додавання по модулю 2. Коди з виходів пам'яті мікрокоманд 9 надходять на входи АЛЛ адреси і забезпечують формування наступних мІкрооперацій: А: = А, А := not А, А := А + 1, А := А - 1, А: = N, А:= G, де А - поточний код адреси, N - код кінцевої адреси комірок пам'яті, G - код початкової адреси комірок пам'яті. Компаратор Cornpl формує прапор переходу A = N, комутатор Cornp2 - ознака переходу A = G, які використовуються контролером послідовності мікрокоманд 10 для реалізації мікрокоманд умовного переходу. На фіг. 7 зображена структурна схема АЛЛ даних, який складається з логічних елементів D1.1-D1.2, D4.1-D4.p, D5.1-D5.p, мультиплексорів D2.1-D2.p і регістра D3. Коди з виходів пам'яті мікрокоманд 9 надходять на входи АЛЛ даних і забезпечують формування наступних робочих операцій: T: = T.T: = not T,T: = S,T: = F, де S - код занесення даних, які надходять з виходів пам'яті мікрокоманд 9, F - доповнення до непарності коду адреси, яке формується схемою додавання по модулю 2 АЛЛ адреси 11. Коди даних запам'ятовуються регістром D3 і передаються на виходи АЛЛ даних 12. На фіг. 8 приведена структурна схема цифрового компаратора даних 16, що містить елементи НЕ-ВИКЛЮЧАЮЧЕ АБО D1.1-D1.p, 2I D2, 2I-HI D3.1-D3.p, регістр D4, багатовхідний елемент І D5, буферний елемент D6 та регістр U1. Зчитані дані з виходів підсилювачів зчитування 4 надходять на входи регістра U1 і запам'ятовуються ним. Еталонні дані надходять з виходів АЛЛ даних 12. Порівняння кодів здійснюють елементи НЕ-ВИКЛЮЧАЮЧЕ АБО D1.1-D1.p. Результат порівняння через елементи D3.1-D3.p надходить на входи регістру D4 і запам'ятовується ним. Однократно зафіксована розбіжність кодів зчитаних та еталонних даних за допомогою елементів D3.1-D3.p фіксує одиничний стан тих розрядів, в яких зафіксована помилка. 9 Управління режимом роботи регістрів U1 і D4 здійснюється за допомогою кодів мікрооперацій, що надходять від пам'яті мікрокоманд 9 і контролера послідовності мікрокоманд 10. Результати тестування через багатовхідний елемент І D5, через буфер D6 передаються на вихід Т1 і використовуються для визначення працездатного стану мікросхеми. На фіг. 9 зображено формат мікрокоманд і мікрооперацій, який складається з наступних полів: - коду мікрокоманди; - робочих мікрооперацій запису (W), зчитування (R), порівняння (А); - коду мікрооперацій адреси; - коду мікрооперацій даних; - адреси переходу. Для формування тестів використовуються наступні мікрокоманди: NOOP- відсутність операції, забезпечує перехід до наступної мікрокоманди; JANN- перехід до команди, код адреси якої записано у полі адреси переходу, якщо поточна адреса комірок пам'яті не дорівнює адресі кінцевої комірки (A N); JANG- перехід до команди, код адреси якої записано у полі адреси переходу, якщо поточна адреса комірок пам'яті не дорівнює адресі початкової комірки (А G), JUMP ~ безумовний перехід до команди, код адреси якої записано у полі адреси переходу; JKNZ - умовний перехід до команди, адреса переходу якої записана у полі адреси переходу, якщо при порівнянні зчитаних даних з еталонними значеннями виявлена розбіжність кодів (К 0); JSUB- виклик підпрограми, код адреси якої записано у полі адреси переходу; RSUB - вихід з підпрограми; STOP - зупинка виконання тесту. Приклад лістингу програми виклику двох версій тестів: МаrсhС і Hammer наведено нижче. 49179 10 Для ініціалізації мікросхеми на axmCS подається сигнал високого рівня напруги, який через буферний елемент 17 забезпечує встановлення в початковий стан усіх компонентів мікросхеми, що забезпечують виконання самотестування. Якщо на входи AD мікросхеми подати код "1000", а потім подати стартовий сигнал ST, то розпочнеться виконання тесту MarchC, а якщо код "011111", то розпочнеться самотестування за допомогою тесту Hammer. Програми тестів MarchC і Hammer наведені нижче. 11 49179 12 При виконанні тесту MarchC відбувається 10w циклів звертання до масиву комірок пам'яті, а при виконанні тесту Hammer - 49м циклів, де п кількість комірок пам'яті. Тест Hammer, який має велику продуктивність, рекомендується виконувати на етапі виготовлення мікросхем пам'яті, а тест MarchC - на етапі їх експлуатації. За станом напруги на виході ТІ ідентифікується стан мікросхеми. За наявності високого рівня напруги на виході ТІ мікросхема вважається непрацездатною. Техніко-економічний ефект при застосуванні заявленої моделі досягається за рахунок підвищення якості мікросхем пам'яті на етапі виготовлення і підвищення коефіцієнта технічної готовності мікросхем на етапі експлуатації, що досягається оперативною зміною програм самотестування. Література 1. Патент США. Built-in self repair circuitry utilizing permanent record of defects. N6651202B1, Int.Cl.G01R 31/28, Nov.18, 2003. 2. Патент США. Semiconductor integrated circuit and method for testing memory. N6233182B1, Int.Cl.GllC 7/00. May 15,2001. 13 49179 14 15 Комп’ютерна верстка Д. Шеверун 49179 Підписне 16 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюSemiconductor memory integrated circuit with built-in multiversion self-testing means

Автори англійськоюUtkina Tetiana Yuriivna, Riabtsev Volodymyr Hryhorovych, Andrienko Volodymyr Oleksandrovych

Назва патенту російськоюМикросхема полупроводниковой памяти со встроенными средствами многоверсионного самотестирования

Автори російськоюУткина Татьяна Юрьевна, Рябцев Владимир Григорьевич, Андриенко Владимир Александрович

МПК / Мітки

МПК: G11C 7/00

Мітки: напівпровідникової, пам'яті, вбудованими, мікросхема, багатоверсійного, самотестування, засобами

Код посилання

<a href="https://ua.patents.su/8-49179-mikroskhema-napivprovidnikovo-pamyati-z-vbudovanimi-zasobami-bagatoversijjnogo-samotestuvannya.html" target="_blank" rel="follow" title="База патентів України">Мікросхема напівпровідникової пам’яті з вбудованими засобами багатоверсійного самотестування</a>

Попередній патент: Антифрикційна композиція

Наступний патент: Штам pasteurella haemolytica 4/08 серовару а-1 для виготовлення діагностичних препаратів

Випадковий патент: Спосіб утворення компенсаційного простору у очисному блоці при підземній розробці рудних покладів