Мікросхема напівпровідникової пам’яті з вбудованими засобами забезпечення допустимого теплового режиму самотестування

Номер патенту: 68985

Опубліковано: 25.04.2012

Автори: Уткіна Тетяна Юріївна, Рябцев Володимир Григорович, Андрієнко Володимир Олександрович

Формула / Реферат

Мікросхема напівпровідникової пам'яті з вбудованими засобами забезпечення допустимого теплового режиму самотестування, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора адреси X і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних Data мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мікрокоманд, перший вхід програмного лічильника підключено до входу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мікрокоманд, треті виходи пам'яті мікрокоманд підключені до перших входів арифметико-логічного пристрою (АЛП) адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключено до виходу ТІ мікросхеми, на який видається результат самотестування, другий вихід компаратора даних підключено до другого входу контролера послідовності мікрокоманд, перші входи комутатора адреси X і комутатора адреси Y підключені до виходів буфера адреси, входи якого є адресними входами AD мікросхеми, другі і треті виходи АЛП адреси підключені до других входів комутатора адреси X і комутатора адреси Y відповідно, перші виходи контролера послідовності мікрокоманд підключені до других входів програмного лічильника, а група виходів контролера послідовності мікрокоманд використовується для управління режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми підключені до виводів мікросхеми, на які подаються управляючі сигнали WE, AS, CS, ОЕ, а виходи даного контролера використовуються для видачі сигналів, які визначають режими роботи мікросхеми, яка відрізняється тим, що в неї додатково введені таймер паузи, буферний елемент, елемент 21, група буферних елементів з трьома станами, комутатор, входи для подачі синхронізуючого сигналу CLK, скидання Reset та відладки Deb, причому перший вхід таймера паузи, третій вхід АЛП адреси та третій вхід АЛП даних підключено до першого виходу програмного лічильника, другий вхід таймера паузи, третій вхід програмного лічильника і третій вхід контролера послідовності мікрокоманд підключені до виходу буферного елемента, вхід якого підключено до входу Reset мікросхеми, третій вхід таймера паузи підключено до другого виходу контролера послідовності мікрокоманд, третій вихід якого підключено до других входів АЛП адреси, АЛП даних, третього входу компаратора даних, шостого входу програмного лічильника і четвертого входу таймера паузи, вихід якого підключено до четвертого входу програмного лічильника, п'яті входи якого і п'яті входи таймера паузи підключені до четвертих виходів пам'яті мікрокоманд, вивід CLK мікросхеми підключено до четвертого входу контролера послідовності мікрокоманд, п'ятий вхід якого підключено до перших виходів АЛП адреси, вхід Deb підключено до першого входу елемента 21, до управляючих входів буферних елементів з трьома станами і управляючого входу комутатора, перші входи якого підключені до других виходів програмного лічильника, а другі входи комутатора підключені до виходів буфера адреси, виходи комутатора підключені до перших входів пам'яті мікрокоманд, вивід WE мікросхеми підключений до другого входу елемента 21, вихід якого підключено до другого входу пам'яті мікрокоманд, треті входи якої підключені до виходів буферних елементів з трьома станами, інформаційні входи яких підключені до виводів Data мікросхеми.

Текст

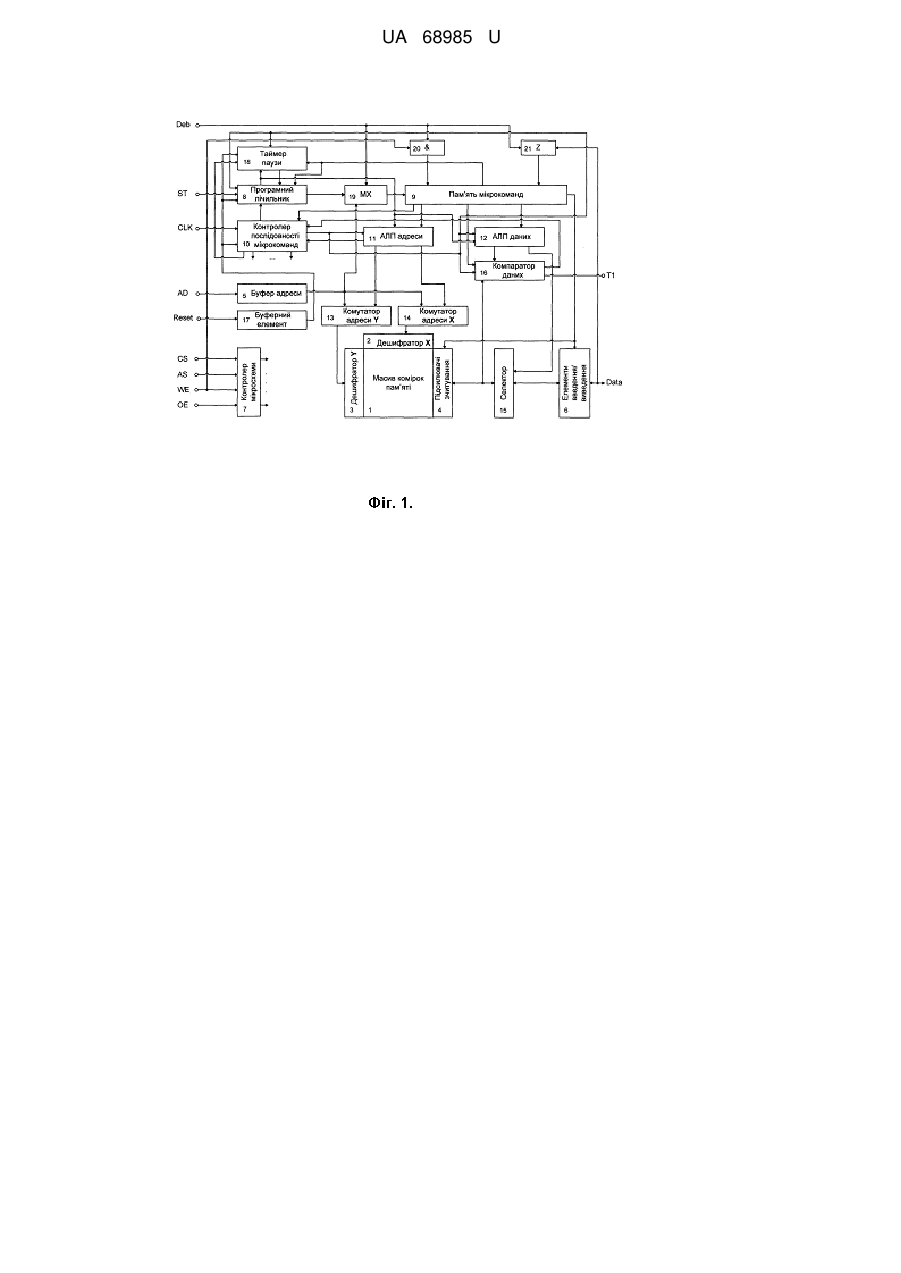

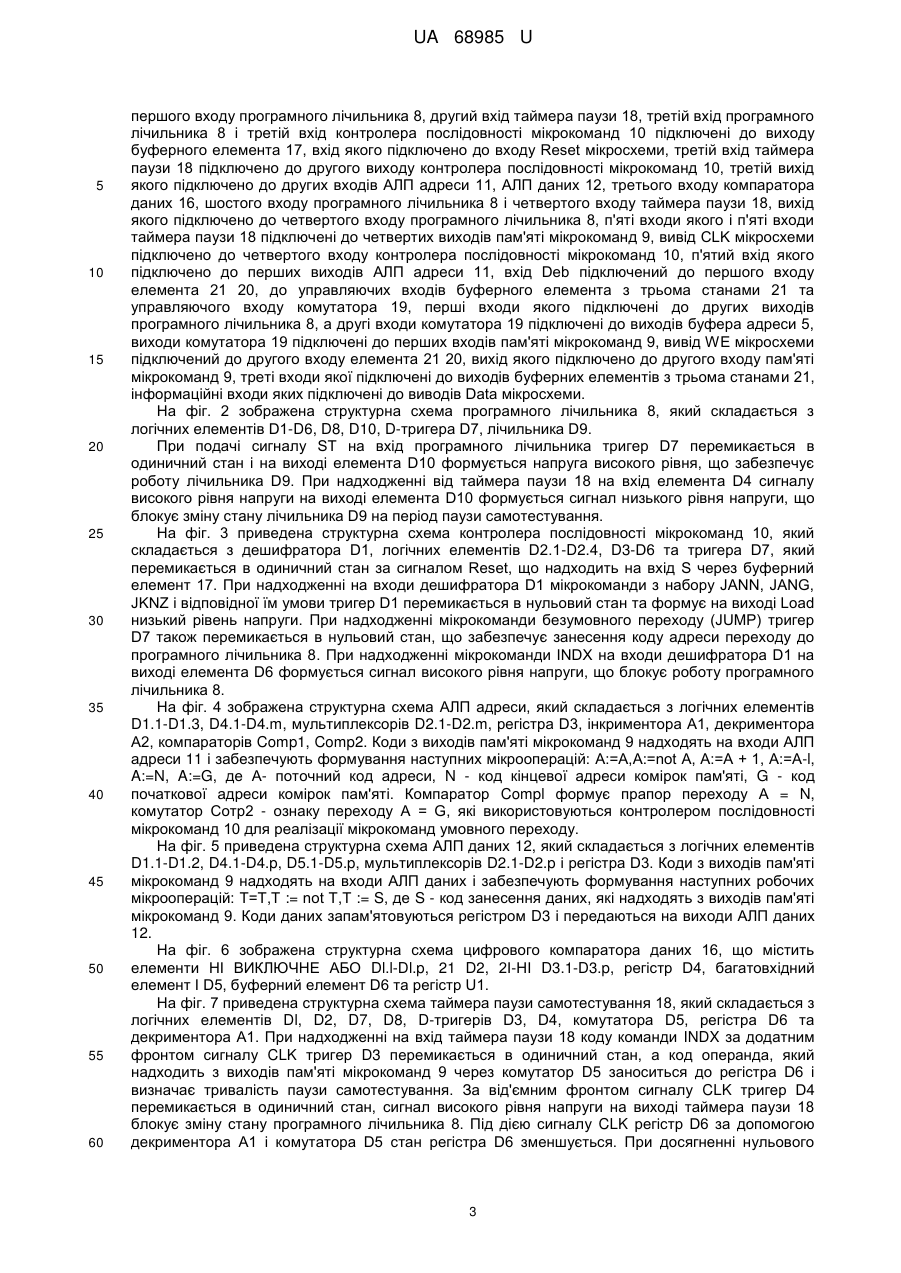

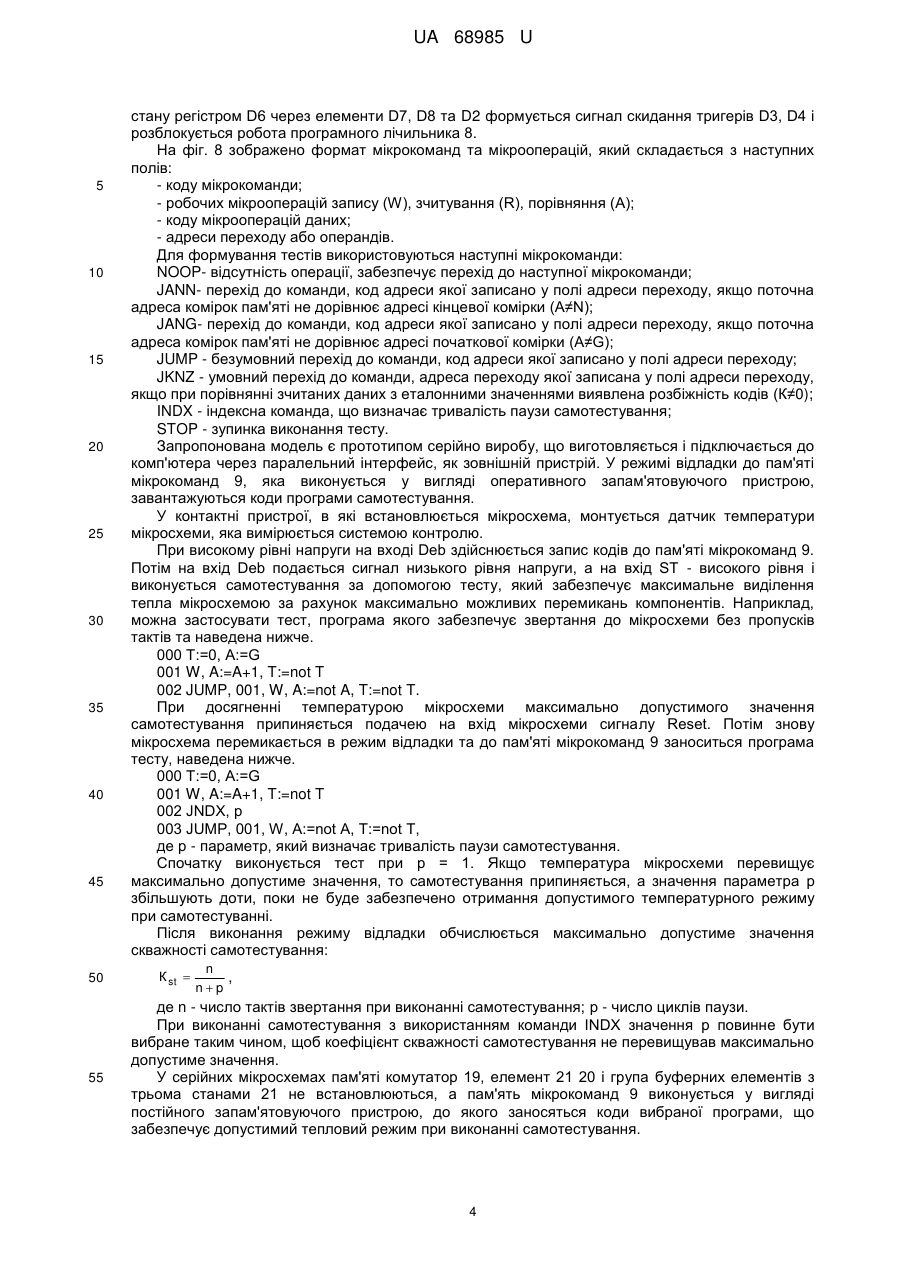

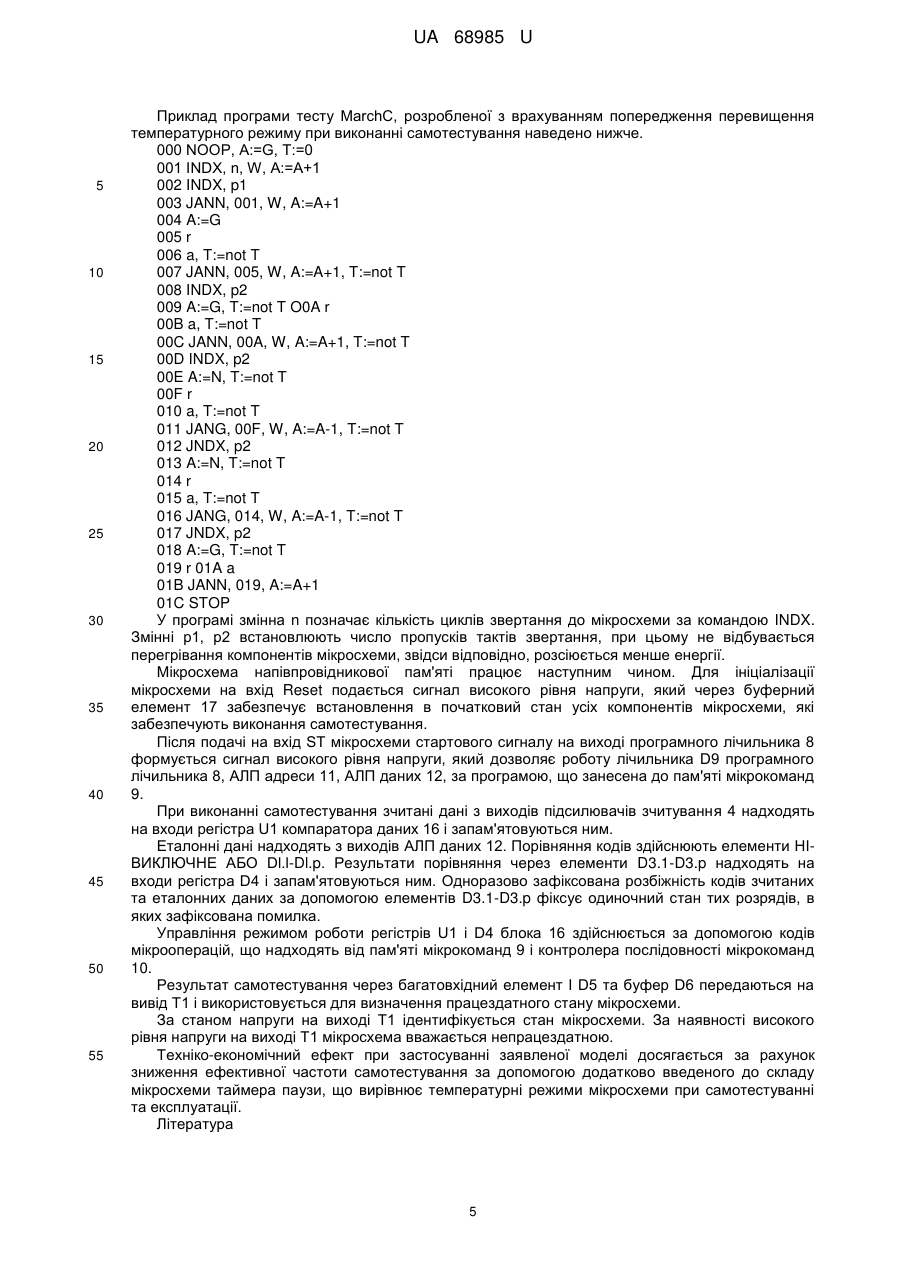

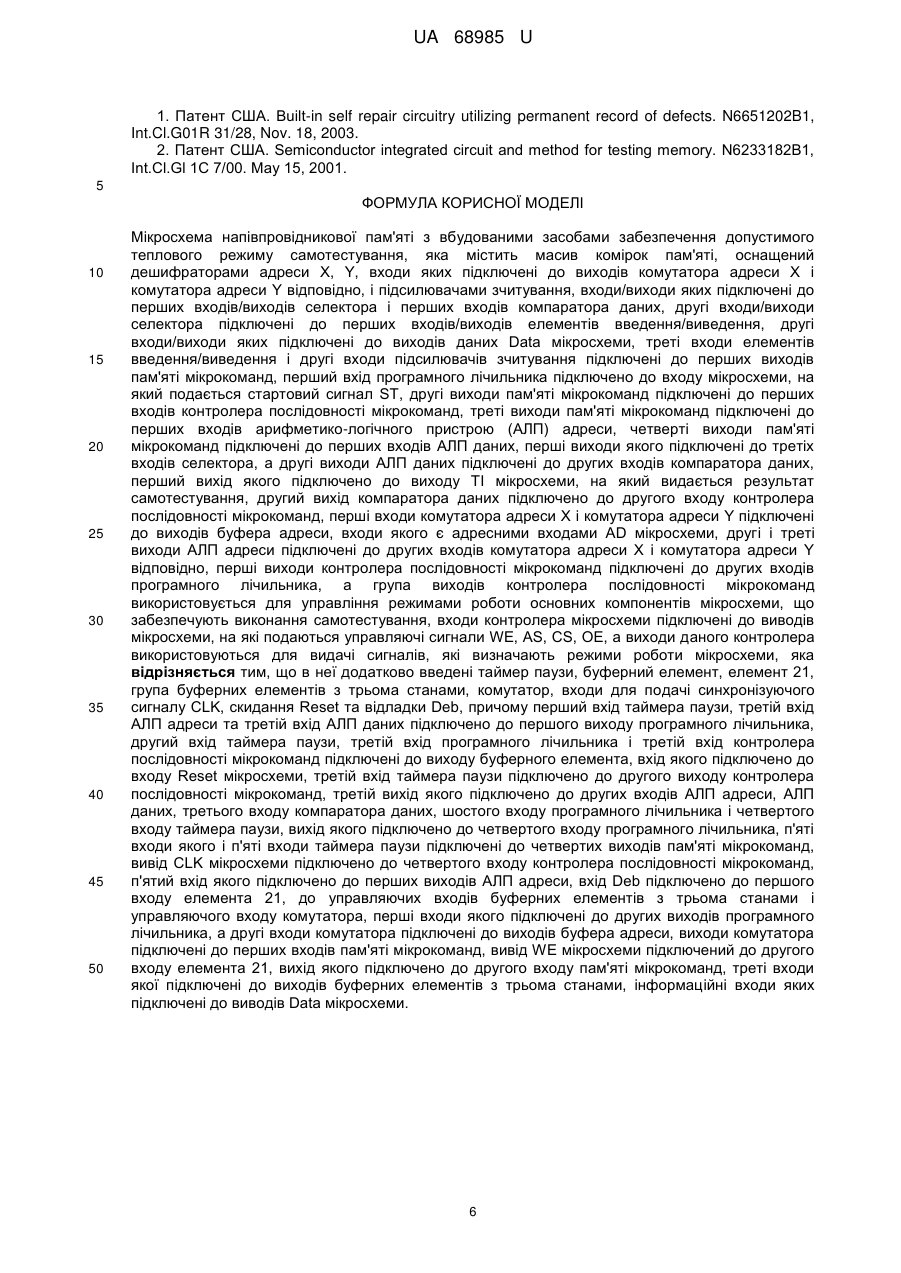

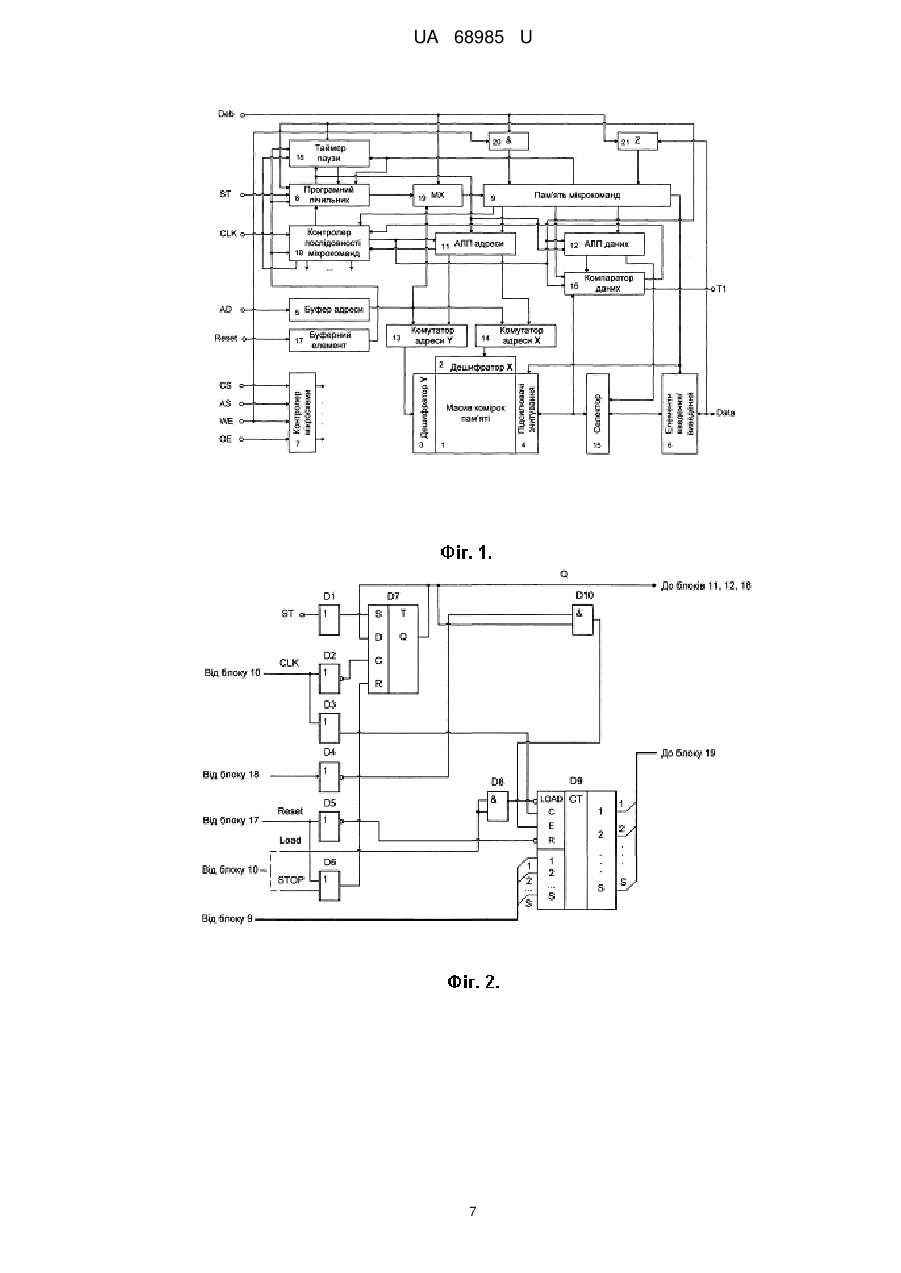

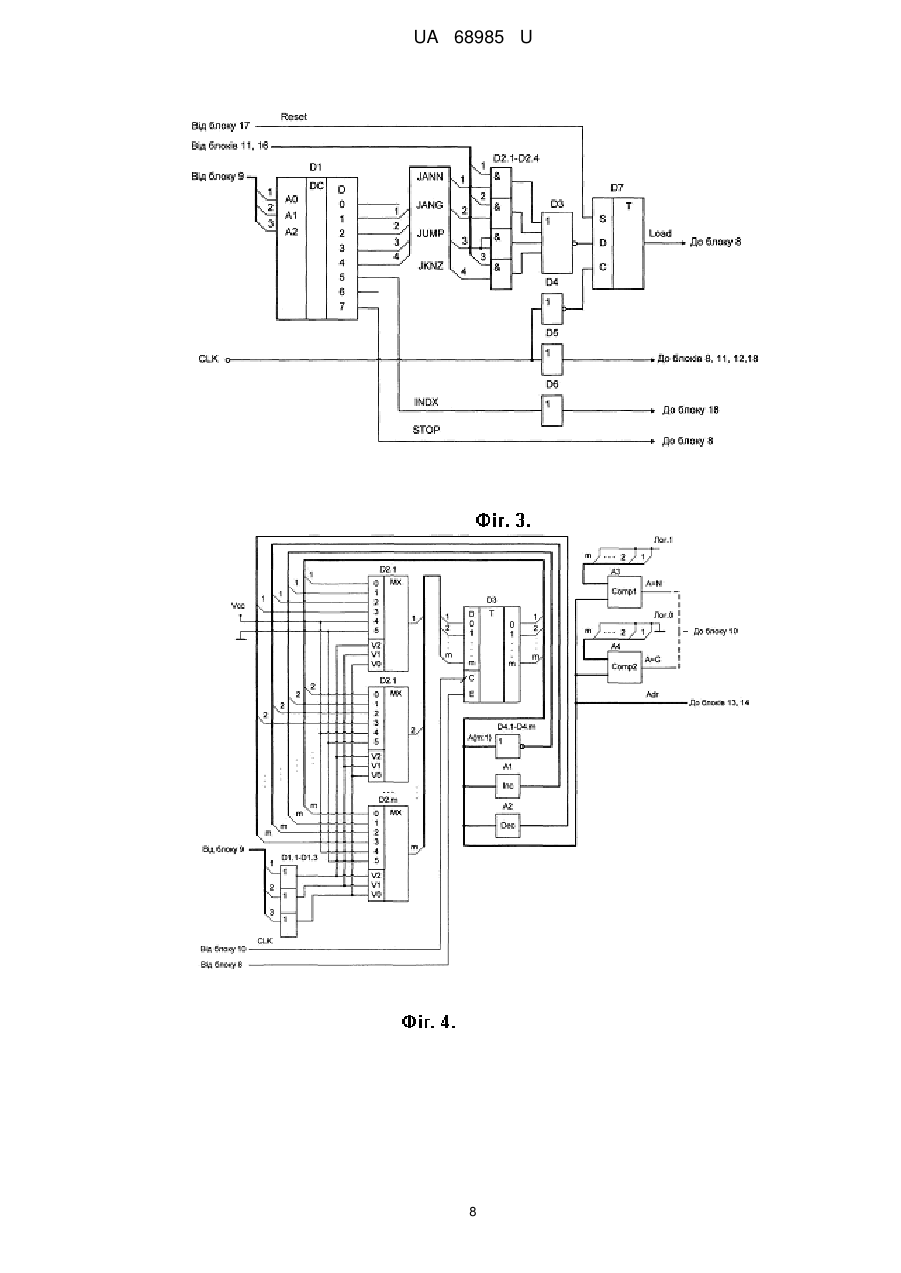

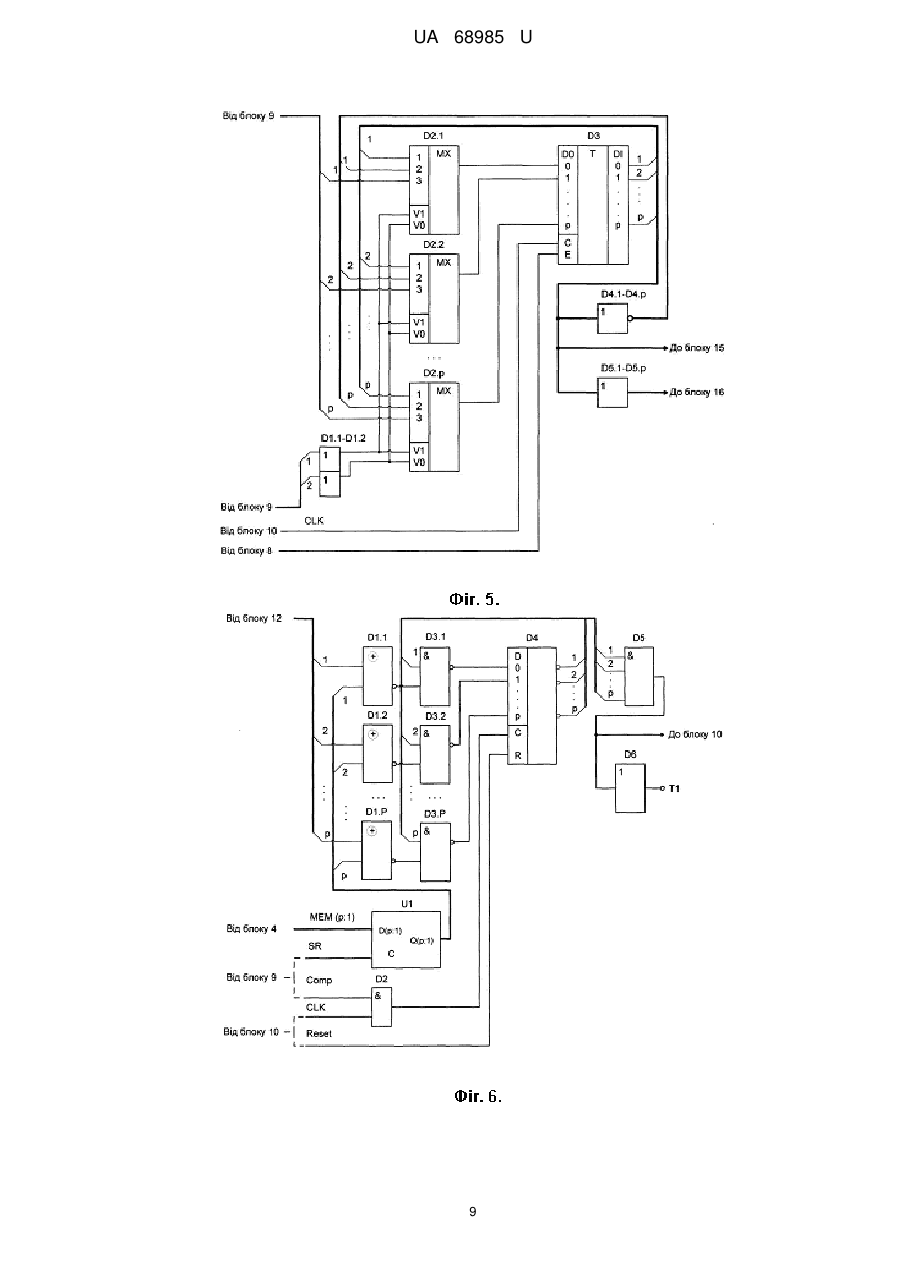

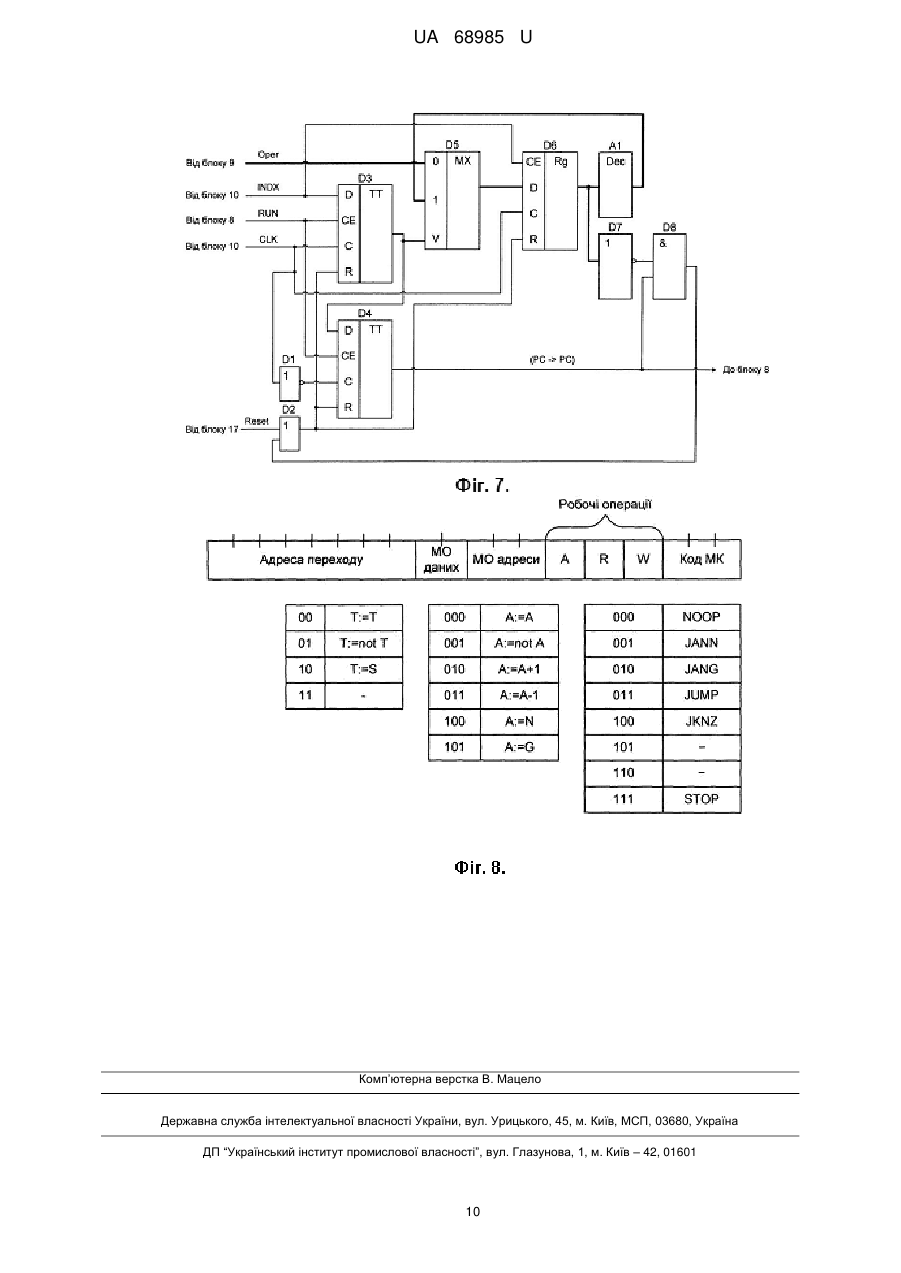

Реферат: Мікросхема напівпровідникової пам'яті з вбудованими засобами забезпечення допустимого теплового режиму самотестування містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора адреси X і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних Data мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мікрокоманд, перший вхід програмного лічильника підключено до входу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мікрокоманд, треті виходи пам'яті мікрокоманд підключені до перших входів арифметикологічного пристрою (АЛП) адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних. UA 68985 U (54) МІКРОСХЕМА НАПІВПРОВІДНИКОВОЇ ПАМ'ЯТІ З ВБУДОВАНИМИ ЗАСОБАМИ ЗАБЕЗПЕЧЕННЯ ДОПУСТИМОГО ТЕПЛОВОГО РЕЖИМУ САМОТЕСТУВАННЯ UA 68985 U UA 68985 U 5 10 15 20 25 30 35 40 45 50 55 60 Мікросхема напівпровідникової пам'яті з вбудованими засобами забезпечення допустимого теплового режиму самотестування належить до засобів обчислювальної техніки і її можна застосовувати для побудови напівпровідникових запам'ятовуючих пристроїв, що містять вбудовані засоби для виконання самотестування, які забезпечують формування кодів адреси, даних, необхідних для запису тестових наборів, зчитування та порівняння даних з еталонними значеннями. Відома мікросхема запам'ятовуючого пристрою з вбудованими засобами ремонту та постійної реєстрації дефектів, яка містить запам'ятовуючий масив комірок з контролером резервних елементів, вбудовані засоби самотестування, які складаються з контролера станів цифрового автомата, генератора адреси, генератора даних і комутатора, а також регістра несправностей, модуля ремонту й регістра сканування [1]. Недоліком даної мікросхеми є можливість перевищення максимально допустимої температури кристалу при самотестуванні великого масиву запам'ятовуючих комірок, що призводить до виникнення нових дефектів. Найбільш близьким до запропонованої моделі є метод тестування пам'яті та інтегральна напівпровідникова мікросхема [2], яка містить масив пам'яті, дешифратор адреси X, дешифратор адреси Y, підсилювачі зчитування, буфер адреси, елементи введення/виведення, контролер мікросхеми, програмний лічильник, пам'ять мікрокоманд, контролер послідовності мікрокоманд, АЛП адреси, АЛП даних, комутатор адреси X, комутатор адреси Y, компаратор, що здійснює порівняння даних. Недоліком даної мікросхеми є можливість її перегрівання, оскільки самотестування виконується без пропусків тактів звертання до мікросхеми, а в реальному режимі експлуатації виникають паузи в роботі мікросхеми для обробки даних процесором. Додаткові дефекти, які виникають через перегрівання кристалів при виконанні самотестування, знижують відсоток виходу придатних виробів. З метою усунення даного недоліку необхідно до складу мікросхеми включити додаткові апаратні засоби, які забезпечують зниження ефективної частоти самотестування, що дозволить виключити перегрівання кристалів. Задача корисної моделі - визначення режиму самотестування, який забезпечує допустимий тепловий режим мікросхеми шляхом зниження ефективної частоти самотестування за допомогою включеної до складу мікросхеми таймера паузи. Вказана задача вирішується тим, що в мікросхему напівпровідникової пам'яті, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора адреси X і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних Data мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мікрокоманд, перший вхід програмного лічильника підключено до входу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мікрокоманд, треті виходи пам'яті мікрокоманд підключені до перших входів АЛП адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключено до виходу ТІ мікросхеми, на який видається результат самотестування, другий вихід комутатора даних підключено до другого входу контролера послідовності мікрокоманд, перші входи комутатора адреси X і комутатора адреси Y підключені до виходів буфера адреси, входи якого є адресними входами AD мікросхеми, другі і треті виходи АЛП адреси підключені до других входів комутатора адреси X і комутатора адреси Y відповідно, перші виходи контролера послідовності мікрокоманд підключені до других входів програмного лічильника, а група виходів контролера послідовності мікрокоманд використовується для управління режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми підключені до виводів мікросхеми, на які подаються управляючі сигнали WE, AS, CS, ОЕ, а виходи даного контролера використовуються для видачі сигналів, які визначають режими роботи мікросхеми, додатково введені таймер паузи, буферний елемент, елемент 2І, група буферних елементів з трьома станами, комутатор, входи для подачі синхронізуючого сигналу CLK, скидання Reset та відладки Deb, причому перший вхід таймера паузи, третій вхід АЛП адреси та третій вхід АЛП даних підключено до першого виходу програмного лічильника, другий вхід таймера паузи, третій вхід програмного лічильника і третій вхід контролера послідовності мікрокоманд підключені до виходу буферного 1 UA 68985 U 5 10 15 20 25 30 35 40 45 50 55 60 елемента, вхід якого підключено до входу Reset мікросхеми, третій вхід таймера паузи підключено до другого входу контролера послідовності мікрокоманд, третій вихід якого підключено до других входів АЛП адреси, АЛП даних, третього входу компаратора даних, шостого входу програмного лічильника і четвертого входу таймера паузи, вихід якого підключено до четвертого входу програмного лічильника, п'яті входи якого і п'яті входи таймера паузи підключені до четвертих виходів пам'яті мікрокоманд, вивід CLK мікросхеми підключено до четвертого входу контролера послідовності мікрокоманд, п'ятий вхід якого підключено до перших виходів АЛП адреси, вхід Deb підключено до першого входу елемента 2І, до управляючих входів буферних елементів з трьома станами і управляючого входу комутатора, перші входи якого підключені до других виходів програмного лічильника, а другі входи комутатора підключені до виходів буфера адреси, виходи комутатора підключені до перших входів пам'яті мікрокоманд, вивід WE мікросхеми підключений до другого входу елемента 2І, вихід якого підключено до другого входу пам'яті мікрокоманд, треті входи якої підключені до виходів буферних елементів з трьома станами, інформаційні входи яких підключені до виводів Data мікросхеми. В основу запропонованої моделі мікросхеми пам'яті поставлена задача запобігання перегріванню кристала шляхом зниження ефективної частоти самотестування за допомогою додатково введеного до складу мікросхеми таймера паузи, що вирівнює температурні режими мікросхеми при самотестуванні та експлуатації, оскільки в обчислювальних системах виникають пропуски тактів звертання до мікросхеми, що забезпечується наявністю тактів обробки зчитаних даних процесором. Таким чином, запропоноване рішення задовольняє критерію "істотні відмінності". На фіг. 1 приведена структурна схема напівпровідникової пам'яті з вбудованими засобами забезпечення допустимого теплового режиму самотестування. На фіг. 2 зображена структурна схема програмного лічильника. На фіг. 3 приведена структурна схема контролера послідовності мікрокоманд. На фіг. 4 зображена структурна схема АЛП адреси. На фіг. 5 приведена структурна схема АЛП даних. На фіг. 6 зображена структурна схема цифрового компаратора даних. На фіг. 7 приведена структурна схема таймера паузи самотестування. На фіг. 8 зображено формат мікрокоманд та мікрооперацій. На фіг. 1 приведена структурна схема напівпровідникової пам'яті з вбудованими засобами забезпечення допустимого теплового режиму самотестування, яка містить масив комірок пам'яті 1, оснащений дешифратором адреси X 2 і дешифратором адреси Y 3, входи яких підключені до виходів комутатора адреси X14 і комутатора адреси Y13 відповідно, і підсилювачі зчитування 4, входи/виходи яких підключені до перших входів/виходів селектора 15 і перших входів компаратора даних 16, другі входи/виходи селектора 15 підключені до перших входів/виходів елементів введення/виведення 6, другі входи/виходи яких підключені до виходів даних Data мікросхеми, треті входи елементів введення/виведення 6 і другі входи підсилювачів зчитування 4 підключені до перших виходів пам'яті мікрокоманд 9, перший вхід програмного лічильника 8 підключено до входу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд 9 підключені до перших входів контролера послідовності мікрокоманд 10, треті виходи пам'яті мікрокоманд 10 підключені до перших входів АЛП адреси 11, четверті виходи пам'яті мікрокоманд 9 підключені до перших входів АЛП даних 12, перші виходи якого підключені до третіх входів селектора 15, а другі виходи АЛП даних 12 підключені до других входів компаратора даних 16, перший вихід якого підключено до виходу ТІ мікросхеми, на який видається результат самотестування, другий вихід компаратора даних 16 підключено до другого входу контролера послідовності мікрокоманд 10, перші входи комутатора адреси X 14 і комутатора адреси Y 13 підключені до виходів буфера адреси 5, входи якого є адресними входами AD мікросхеми, другі і треті виходи АЛП адреси 11 підключені до других входів комутатора адреси X 14 і комутатора адреси Y 13 відповідно, перші виходи контролера послідовності мікрокоманд 10 підключені до других входів програмного лічильника 8, а група виходів контролера послідовності мікрокоманд 10 використовується для управління режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми 7 підключені до виводів мікросхеми, на які подаються управляючі сигнали WE, AS, CS, ОЕ, а виходи даного контролера використовуються для видачі сигналів, які визначають режими роботи мікросхеми, яка також містить таймер паузи 18, буферний елемент 17, елемент 21 20, групу буферних елементів з трьома станами 21, комутатор 19, входи для подачі синхронізуючого сигналу CLK, скидання Reset та відладки Deb, причому перший вхід таймера паузи 18, третій вхід АЛП адреси 11 та третій вхід АЛП даних 12 підключено до 2 UA 68985 U 5 10 15 20 25 30 35 40 45 50 55 60 першого входу програмного лічильника 8, другий вхід таймера паузи 18, третій вхід програмного лічильника 8 і третій вхід контролера послідовності мікрокоманд 10 підключені до виходу буферного елемента 17, вхід якого підключено до входу Reset мікросхеми, третій вхід таймера паузи 18 підключено до другого виходу контролера послідовності мікрокоманд 10, третій вихід якого підключено до других входів АЛП адреси 11, АЛП даних 12, третього входу компаратора даних 16, шостого входу програмного лічильника 8 і четвертого входу таймера паузи 18, вихід якого підключено до четвертого входу програмного лічильника 8, п'яті входи якого і п'яті входи таймера паузи 18 підключені до четвертих виходів пам'яті мікрокоманд 9, вивід CLK мікросхеми підключено до четвертого входу контролера послідовності мікрокоманд 10, п'ятий вхід якого підключено до перших виходів АЛП адреси 11, вхід Deb підключений до першого входу елемента 21 20, до управляючих входів буферного елемента з трьома станами 21 та управляючого входу комутатора 19, перші входи якого підключені до других виходів програмного лічильника 8, а другі входи комутатора 19 підключені до виходів буфера адреси 5, виходи комутатора 19 підключені до перших входів пам'яті мікрокоманд 9, вивід WE мікросхеми підключений до другого входу елемента 21 20, вихід якого підключено до другого входу пам'яті мікрокоманд 9, треті входи якої підключені до виходів буферних елементів з трьома станами 21, інформаційні входи яких підключені до виводів Data мікросхеми. На фіг. 2 зображена структурна схема програмного лічильника 8, який складається з логічних елементів D1-D6, D8, D10, D-тригера D7, лічильника D9. При подачі сигналу ST на вхід програмного лічильника тригер D7 перемикається в одиничний стан і на виході елемента D10 формується напруга високого рівня, що забезпечує роботу лічильника D9. При надходженні від таймера паузи 18 на вхід елемента D4 сигналу високого рівня напруги на виході елемента D10 формується сигнал низького рівня напруги, що блокує зміну стану лічильника D9 на період паузи самотестування. На фіг. 3 приведена структурна схема контролера послідовності мікрокоманд 10, який складається з дешифратора D1, логічних елементів D2.1-D2.4, D3-D6 та тригера D7, який перемикається в одиничний стан за сигналом Reset, що надходить на вхід S через буферний елемент 17. При надходженні на входи дешифратора D1 мікрокоманди з набору JANN, JANG, JKNZ і відповідної їм умови тригер D1 перемикається в нульовий стан та формує на виході Load низький рівень напруги. При надходженні мікрокоманди безумовного переходу (JUMP) тригер D7 також перемикається в нульовий стан, що забезпечує занесення коду адреси переходу до програмного лічильника 8. При надходженні мікрокоманди INDX на входи дешифратора D1 на виході елемента D6 формується сигнал високого рівня напруги, що блокує роботу програмного лічильника 8. На фіг. 4 зображена структурна схема АЛП адреси, який складається з логічних елементів D1.1-D1.3, D4.1-D4.m, мультиплексорів D2.1-D2.m, регістра D3, інкриментора А1, декриментора А2, компараторів Comp1, Comp2. Коди з виходів пам'яті мікрокоманд 9 надходять на входи АЛП адреси 11 і забезпечують формування наступних мікрооперацій: А:=А,A:=not А, А:=А + 1, A:=A-l, A:=N, A:=G, де А- поточний код адреси, N - код кінцевої адреси комірок пам'яті, G - код початкової адреси комірок пам'яті. Компаратор Compl формує прапор переходу А = N, комутатор Сотр2 - ознаку переходу А = G, які використовуються контролером послідовності мікрокоманд 10 для реалізації мікрокоманд умовного переходу. На фіг. 5 приведена структурна схема АЛП даних 12, який складається з логічних елементів D1.1-D1.2, D4.1-D4.p, D5.1-D5.p, мультиплексорів D2.1-D2.p і регістра D3. Коди з виходів пам'яті мікрокоманд 9 надходять на входи АЛП даних і забезпечують формування наступних робочих мікрооперацій: Т=Т,Т := not Т,Т := S, де S - код занесення даних, які надходять з виходів пам'яті мікрокоманд 9. Коди даних запам'ятовуються регістром D3 і передаються на виходи АЛП даних 12. На фіг. 6 зображена структурна схема цифрового компаратора даних 16, що містить елементи HІ ВИКЛЮЧНЕ АБО Dl.l-Dl.p, 21 D2, 2І-НІ D3.1-D3.p, регістр D4, багатовхідний елемент І D5, буферний елемент D6 та регістр U1. На фіг. 7 приведена структурна схема таймера паузи самотестування 18, який складається з логічних елементів Dl, D2, D7, D8, D-тригерів D3, D4, комутатора D5, регістра D6 та декриментора А1. При надходженні на вхід таймера паузи 18 коду команди INDX за додатним фронтом сигналу CLK тригер D3 перемикається в одиничний стан, а код операнда, який надходить з виходів пам'яті мікрокоманд 9 через комутатор D5 заноситься до регістра D6 і визначає тривалість паузи самотестування. За від'ємним фронтом сигналу CLK тригер D4 перемикається в одиничний стан, сигнал високого рівня напруги на виході таймера паузи 18 блокує зміну стану програмного лічильника 8. Під дією сигналу CLK регістр D6 за допомогою декриментора А1 і комутатора D5 стан регістра D6 зменшується. При досягненні нульового 3 UA 68985 U 5 10 15 20 25 30 35 40 45 50 55 стану регістром D6 через елементи D7, D8 та D2 формується сигнал скидання тригерів D3, D4 і розблокується робота програмного лічильника 8. На фіг. 8 зображено формат мікрокоманд та мікрооперацій, який складається з наступних полів: - коду мікрокоманди; - робочих мікрооперацій запису (W), зчитування (R), порівняння (А); - коду мікрооперацій даних; - адреси переходу або операндів. Для формування тестів використовуються наступні мікрокоманди: NOOP- відсутність операції, забезпечує перехід до наступної мікрокоманди; JANN- перехід до команди, код адреси якої записано у полі адреси переходу, якщо поточна адреса комірок пам'яті не дорівнює адресі кінцевої комірки (A≠N); JANG- перехід до команди, код адреси якої записано у полі адреси переходу, якщо поточна адреса комірок пам'яті не дорівнює адресі початкової комірки (A≠G); JUMP - безумовний перехід до команди, код адреси якої записано у полі адреси переходу; JKNZ - умовний перехід до команди, адреса переходу якої записана у полі адреси переходу, якщо при порівнянні зчитаних даних з еталонними значеннями виявлена розбіжність кодів (К≠0); INDX - індексна команда, що визначає тривалість паузи самотестування; STOP - зупинка виконання тесту. Запропонована модель є прототипом серійно виробу, що виготовляється і підключається до комп'ютера через паралельний інтерфейс, як зовнішній пристрій. У режимі відладки до пам'яті мікрокоманд 9, яка виконується у вигляді оперативного запам'ятовуючого пристрою, завантажуються коди програми самотестування. У контактні пристрої, в які встановлюється мікросхема, монтується датчик температури мікросхеми, яка вимірюється системою контролю. При високому рівні напруги на вході Deb здійснюється запис кодів до пам'яті мікрокоманд 9. Потім на вхід Deb подається сигнал низького рівня напруги, а на вхід ST - високого рівня і виконується самотестування за допомогою тесту, який забезпечує максимальне виділення тепла мікросхемою за рахунок максимально можливих перемикань компонентів. Наприклад, можна застосувати тест, програма якого забезпечує звертання до мікросхеми без пропусків тактів та наведена нижче. 000 Т:=0, A:=G 001 W, A:=A+1, T:=not T 002 JUMP, 001, W, A:=not A, T:=not T. При досягненні температурою мікросхеми максимально допустимого значення самотестування припиняється подачею на вхід мікросхеми сигналу Reset. Потім знову мікросхема перемикається в режим відладки та до пам'яті мікрокоманд 9 заноситься програма тесту, наведена нижче. 000 Т:=0, A:=G 001 W, A:=A+1, T:=not T 002 JNDX, р 003 JUMP, 001, W, A:=not А, Т:=not T, де р - параметр, який визначає тривалість паузи самотестування. Спочатку виконується тест при р = 1. Якщо температура мікросхеми перевищує максимально допустиме значення, то самотестування припиняється, а значення параметра р збільшують доти, поки не буде забезпечено отримання допустимого температурного режиму при самотестуванні. Після виконання режиму відладки обчислюється максимально допустиме значення скважності самотестування: К st n , np де n - число тактів звертання при виконанні самотестування; р - число циклів паузи. При виконанні самотестування з використанням команди INDX значення р повинне бути вибране таким чином, щоб коефіцієнт скважності самотестування не перевищував максимально допустиме значення. У серійних мікросхемах пам'яті комутатор 19, елемент 21 20 і група буферних елементів з трьома станами 21 не встановлюються, а пам'ять мікрокоманд 9 виконується у вигляді постійного запам'ятовуючого пристрою, до якого заносяться коди вибраної програми, що забезпечує допустимий тепловий режим при виконанні самотестування. 4 UA 68985 U 5 10 15 20 25 30 35 40 45 50 55 Приклад програми тесту MarchC, розробленої з врахуванням попередження перевищення температурного режиму при виконанні самотестування наведено нижче. 000 NOOP, A:=G, Т:=0 001 INDX, n, W, А:=А+1 002 INDX, p1 003 JANN, 001, W, A:=A+1 004 A:=G 005 r 006 a, T:=not T 007 JANN, 005, W, A:=A+1, T:=not T 008 INDX, p2 009 A:=G, T:=not T O0A r 00B a, T:=not T 00C JANN, 00A, W, A:=A+1, T:=not T 00D INDX, p2 00E A:=N, T:=not T 00F r 010 a, T:=not T 011 JANG, 00F, W, A:=A-1, T:=not T 012 JNDX, p2 013 A:=N, T:=not T 014 r 015 a, T:=not T 016 JANG, 014, W, A:=A-1, T:=not T 017 JNDX, p2 018 A:=G, T:=not T 019 r 01A a 01B JANN, 019, A:=A+1 01C STOP У програмі змінна n позначає кількість циклів звертання до мікросхеми за командою INDX. Змінні р1, р2 встановлюють число пропусків тактів звертання, при цьому не відбувається перегрівання компонентів мікросхеми, звідси відповідно, розсіюється менше енергії. Мікросхема напівпровідникової пам'яті працює наступним чином. Для ініціалізації мікросхеми на вхід Reset подається сигнал високого рівня напруги, який через буферний елемент 17 забезпечує встановлення в початковий стан усіх компонентів мікросхеми, які забезпечують виконання самотестування. Після подачі на вхід ST мікросхеми стартового сигналу на виході програмного лічильника 8 формується сигнал високого рівня напруги, який дозволяє роботу лічильника D9 програмного лічильника 8, АЛП адреси 11, АЛП даних 12, за програмою, що занесена до пам'яті мікрокоманд 9. При виконанні самотестування зчитані дані з виходів підсилювачів зчитування 4 надходять на входи регістра U1 компаратора даних 16 і запам'ятовуються ним. Еталонні дані надходять з виходів АЛП даних 12. Порівняння кодів здійснюють елементи HІВИКЛЮЧНЕ АБО Dl.l-Dl.p. Результати порівняння через елементи D3.1-D3.p надходять на входи регістра D4 і запам'ятовуються ним. Одноразово зафіксована розбіжність кодів зчитаних та еталонних даних за допомогою елементів D3.1-D3.p фіксує одиночний стан тих розрядів, в яких зафіксована помилка. Управління режимом роботи регістрів U1 і D4 блока 16 здійснюється за допомогою кодів мікрооперацій, що надходять від пам'яті мікрокоманд 9 і контролера послідовності мікрокоманд 10. Результат самотестування через багатовхідний елемент І D5 та буфер D6 передаються на вивід Т1 і використовується для визначення працездатного стану мікросхеми. За станом напруги на виході Т1 ідентифікується стан мікросхеми. За наявності високого рівня напруги на виході Т1 мікросхема вважається непрацездатною. Техніко-економічний ефект при застосуванні заявленої моделі досягається за рахунок зниження ефективної частоти самотестування за допомогою додатково введеного до складу мікросхеми таймера паузи, що вирівнює температурні режими мікросхеми при самотестуванні та експлуатації. Література 5 UA 68985 U 1. Патент США. Built-in self repair circuitry utilizing permanent record of defects. N6651202B1, Int.Cl.G01R 31/28, Nov. 18, 2003. 2. Патент США. Semiconductor integrated circuit and method for testing memory. N6233182B1, Int.Cl.Gl 1С 7/00. May 15, 2001. 5 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 10 15 20 25 30 35 40 45 50 Мікросхема напівпровідникової пам'яті з вбудованими засобами забезпечення допустимого теплового режиму самотестування, яка містить масив комірок пам'яті, оснащений дешифраторами адреси X, Y, входи яких підключені до виходів комутатора адреси X і комутатора адреси Y відповідно, і підсилювачами зчитування, входи/виходи яких підключені до перших входів/виходів селектора і перших входів компаратора даних, другі входи/виходи селектора підключені до перших входів/виходів елементів введення/виведення, другі входи/виходи яких підключені до виходів даних Data мікросхеми, треті входи елементів введення/виведення і другі входи підсилювачів зчитування підключені до перших виходів пам'яті мікрокоманд, перший вхід програмного лічильника підключено до входу мікросхеми, на який подається стартовий сигнал ST, другі виходи пам'яті мікрокоманд підключені до перших входів контролера послідовності мікрокоманд, треті виходи пам'яті мікрокоманд підключені до перших входів арифметико-логічного пристрою (АЛП) адреси, четверті виходи пам'яті мікрокоманд підключені до перших входів АЛП даних, перші виходи якого підключені до третіх входів селектора, а другі виходи АЛП даних підключені до других входів компаратора даних, перший вихід якого підключено до виходу ТІ мікросхеми, на який видається результат самотестування, другий вихід компаратора даних підключено до другого входу контролера послідовності мікрокоманд, перші входи комутатора адреси X і комутатора адреси Y підключені до виходів буфера адреси, входи якого є адресними входами AD мікросхеми, другі і треті виходи АЛП адреси підключені до других входів комутатора адреси X і комутатора адреси Y відповідно, перші виходи контролера послідовності мікрокоманд підключені до других входів програмного лічильника, а група виходів контролера послідовності мікрокоманд використовується для управління режимами роботи основних компонентів мікросхеми, що забезпечують виконання самотестування, входи контролера мікросхеми підключені до виводів мікросхеми, на які подаються управляючі сигнали WE, AS, CS, ОЕ, а виходи даного контролера використовуються для видачі сигналів, які визначають режими роботи мікросхеми, яка відрізняється тим, що в неї додатково введені таймер паузи, буферний елемент, елемент 21, група буферних елементів з трьома станами, комутатор, входи для подачі синхронізуючого сигналу CLK, скидання Reset та відладки Deb, причому перший вхід таймера паузи, третій вхід АЛП адреси та третій вхід АЛП даних підключено до першого виходу програмного лічильника, другий вхід таймера паузи, третій вхід програмного лічильника і третій вхід контролера послідовності мікрокоманд підключені до виходу буферного елемента, вхід якого підключено до входу Reset мікросхеми, третій вхід таймера паузи підключено до другого виходу контролера послідовності мікрокоманд, третій вихід якого підключено до других входів АЛП адреси, АЛП даних, третього входу компаратора даних, шостого входу програмного лічильника і четвертого входу таймера паузи, вихід якого підключено до четвертого входу програмного лічильника, п'яті входи якого і п'яті входи таймера паузи підключені до четвертих виходів пам'яті мікрокоманд, вивід CLK мікросхеми підключено до четвертого входу контролера послідовності мікрокоманд, п'ятий вхід якого підключено до перших виходів АЛП адреси, вхід Deb підключено до першого входу елемента 21, до управляючих входів буферних елементів з трьома станами і управляючого входу комутатора, перші входи якого підключені до других виходів програмного лічильника, а другі входи комутатора підключені до виходів буфера адреси, виходи комутатора підключені до перших входів пам'яті мікрокоманд, вивід WE мікросхеми підключений до другого входу елемента 21, вихід якого підключено до другого входу пам'яті мікрокоманд, треті входи якої підключені до виходів буферних елементів з трьома станами, інформаційні входи яких підключені до виводів Data мікросхеми. 6 UA 68985 U 7 UA 68985 U 8 UA 68985 U 9 UA 68985 U Комп’ютерна верстка В. Мацело Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 10

ДивитисяДодаткова інформація

Назва патенту англійськоюSemiconductor memory microelectronic circuit with built-in capabilities to provide allowed thermal self-testing conditions

Автори англійськоюUtkina Tetiana Yuriivna, Riabtsev Volodymyr Hryhorovych, Andrienko Volodymyr Oleksandrovych

Назва патенту російськоюМикросхема полупроводниковой памяти со встроенными средствами обеспечения допустимого теплового режима самотестирования

Автори російськоюУткина Татьяна Юрьевна, Рябцев Владимир Григорьевич, Андриенко Владимир Александрович

МПК / Мітки

МПК: G11C 7/00

Мітки: допустимого, забезпечення, вбудованими, теплового, пам'яті, мікросхема, режиму, самотестування, засобами, напівпровідникової

Код посилання

<a href="https://ua.patents.su/12-68985-mikroskhema-napivprovidnikovo-pamyati-z-vbudovanimi-zasobami-zabezpechennya-dopustimogo-teplovogo-rezhimu-samotestuvannya.html" target="_blank" rel="follow" title="База патентів України">Мікросхема напівпровідникової пам’яті з вбудованими засобами забезпечення допустимого теплового режиму самотестування</a>

Попередній патент: Спосіб очищення рідини

Наступний патент: Сільськогосподарський комбайн, система та спосіб повторного обмолоту згонин у комбайні

Випадковий патент: Пристрій до редуктора-випарника з економайзером та електромагнітним клапаном газобалонної апаратури для легкових автомобілів