Напівпровідниковий запам’ятовуючий пристрій з відновленням працездатності при багатократних відмовах

Номер патенту: 82607

Опубліковано: 12.08.2013

Автори: Уткіна Тетяна Юріївна, Рябцев Володимир Григорович, Колпаков Іван Олександрович, Андрієнко Володимир Олександрович

Формула / Реферат

Напівпровідниковий запам'ятовуючий пристрій з відновленням працездатності при багатократних відмовах, який містить основний і запасний масиви запам'ятовуючих комірок, контролер самотестування, генератори кодів адреси і даних, мультиплексори кодів операцій, адреси і даних, компаратор, причому перші, другі і треті виходи контролера самотестування підключені до перших входів мультиплексора коду операцій, генератора коду адреси і генератора коду даних відповідно, перший, другий, третій входи контролера самотестування підключені до виводів ST, CLK і RST пристрою відповідно, другі входи мультиплексорів кодів операцій, адреси і даних підключені до виводів WR, Sys_Address, Sys_Data пристрою відповідно, виходи мультиплексорів коду операцій і коду адреси підключені до перших і других входів основного і запасного масивів запам'ятовуючих комірок відповідно, виходи генератора коду адреси підключені до перших входів мультиплексора кодів адреси, виходи генератора коду даних підключені до перших входів мультиплексора коду даних і перших входів компаратора, другі і треті входи якого підключені до виходів основного і запасного масивів запам'ятовуючих комірок відповідно, перший вихід компаратора підключено до четвертого входу контролера самотестування і виводу Т пристрою, який відрізняється тим, що в нього додатково введені блок відновлення працездатності, реконфігуратор вхідних даних і реконфігуратор вихідних даних, виходи якого підключені до виводів Data пристрою, перші і другі входи реконфігуратора вихідних даних підключені до виходів основного і запасного масивів запам'ятовуючих комірок відповідно, перші виходи блока відновлення працездатності підключені до третіх входів реконфігуратора вихідних даних і перших входів реконфігуратора вхідних даних, виходи якого підключені до третіх входів запасного масиву запам'ятовуючих комірок, виходи мультиплексора коду даних підключені до других входів реконфігуратора вхідних даних, другі виходи компаратора підключені до перших входів блока відновлення працездатності, четверті входи компаратора підключені до четвертих виходів контролера самотестування, п'ятий вихід якого підключено до другого входу блока відновлення працездатності, другий вихід якого підключено до виводу Fail пристрою.

Текст

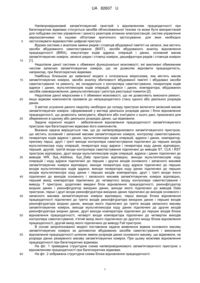

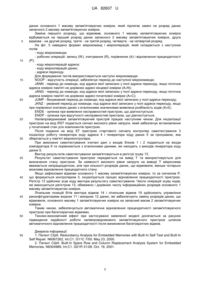

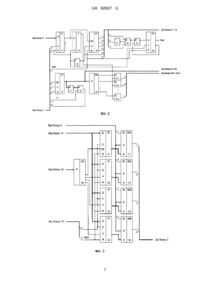

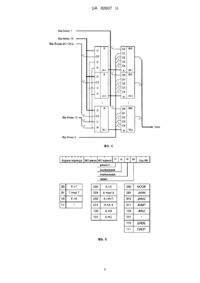

Реферат: Напівпровідниковий запам'ятовуючий пристрій з відновленням працездатності при багатократних відмовах містить основний і запасний масиви запам'ятовуючих комірок, контролер самотестування, генератори кодів адреси і даних, мультиплексори кодів операцій, адреси і даних, компаратор, причому перші, другі і треті виходи контролера самотестування підключені до перших входів мультиплексора коду операцій, генератора коду адреси і генератора коду даних відповідно, перший, другий, третій входи контролера самотестування підключені до виводів ST, CLK і RST пристрою відповідно, другі входи мультиплексорів кодів операцій, адреси і даних підключені до виводів WR, Sys_Address, Sys_Data пристрою відповідно, виходи мультиплексорів коду операцій і коду адреси підключені до перших і других входів основного і запасного масивів запам'ятовуючих комірок відповідно, виходи генератора коду адреси підключені до перших входів мультиплексора кодів адреси, виходи генератора коду даних підключені до перших входів мультиплексора коду даних і перших входів компаратора, другі і треті входи якого підключені до виходів основного і запасного масивів запам'ятовуючих комірок відповідно, перший вихід компаратора підключено до четвертого входу контролера самотестування і виводу Т пристрою. В нього додатково введені блок відновлення працездатності, реконфігуратор вхідних даних і реконфігуратор вихідних даних. UA 82607 U (54) НАПІВПРОВІДНИКОВИЙ ЗАПАМ'ЯТОВУЮЧИЙ ПРИСТРІЙ З ВІДНОВЛЕННЯМ ПРАЦЕЗДАТНОСТІ ПРИ БАГАТОКРАТНИХ ВІДМОВАХ UA 82607 U UA 82607 U 5 10 15 20 25 30 35 40 45 50 55 60 Напівпровідниковий запам'ятовуючий пристрій з відновленням працездатності при багатократних відмовах стосується засобів обчислювальної техніки та може бути використаний для побудови систем управління і захисту реакторів атомних електростанцій, систем управління аерокосмічними та іншими об'єктами критичного застосування, для яких необхідно застосовувати відмовостійкі цифрові пристрої. Відома система з аналізом заміни рядків і стовпців вбудованої пам'яті на запасні, яка містить засоби вбудованого самотестування (BIST), засоби вбудованого аналізу відновлення працездатності (BIRA), комутатори кодів адреси, операцій і даних, основний масив запам'ятовуючих комірок, запасні рядки і стовпці комірок, дешифратори рядків і стовпців комірок [1]. Недоліком даної системи є обмежені функціональні можливості, які викликані обмеженим числом запасних запам'ятовуючих комірок, що не дозволяє відновити працездатність, наприклад, при багатократних відмовах. Найбільш близькою до заявленої моделі є інтегральна мікросхема, яка містить масив запам'ятовуючих комірок, засоби аналізу збитковості вбудованої пам'яті і вбудовані засоби самотестування та ремонту, які складаються з контролера самотестування, генераторів кодів адреси і даних, мультиплексорів кодів операцій, адреси і даних, компаратора, вбудованих засобів самовідновлення, демультиплексора і регістра реєстрації помилок [2]. Недоліком даної мікросхеми є її обмежені можливості, що не дозволяють виконати ремонт, якщо відмови компонентів призвели до непрацездатного стану одного або декількох розрядів даних. З метою усунення даного недоліку необхідно до складу пристрою включити запасний масив запам'ятовуючих комірок, сформований у вигляді декількох розрядів даних і блок відновлення працездатності, що дозволить записувати, зберігати або зчитувати з нього дані, призначені для збереження в одному або декількох розрядах даних, що відмовили. Задача корисної моделі - забезпечення відновлення працездатності запам'ятовуючого пристрою при багатократних відмовах його компонентів. Вказана задача вирішується тим, що до напівпровідникового запам'ятовуючого пристрою, що містить основний і запасний масиви запам'ятовуючих комірок, контролер самотестування, генератори кодів адреси і даних, мультиплексори кодів операцій, адреси і даних, компаратор, причому перші, другі і треті виходи контролера самотестування підключені до перших входів мультиплексора коду операцій, генератора коду адреси і генератора коду даних відповідно, перший, другий, третій входи контролера самотестування підключені до виводів ST, CLK і RST пристрою відповідно, другі входи мультиплексорів кодів операцій, адреси і даних підключені до виводів WR, Sys_Address, Sys_Data пристрою відповідно, виходи мультиплексорів коду операцій і коду адреси підключені до перших і других входів основного і запасного масивів запам'ятовуючих комірок відповідно, виходи генераторакоду адреси підключені до перших входів мультиплексора кодів адреси, виходи генератора коду даних підключені до перших входів мультиплексора коду даних і перших входів компаратора, другі і треті входи якого підключені до виходів основного і запасного масивів запам'ятовуючих комірок відповідно, перший вихід компаратора підключено до четвертого входу контролера самотестування і виводу Т пристрою, додатково введені блок відновлення працездатності, реконфігуратор вхідних даних і реконфігуратор вихідних даних, виходи якого підключені до виводів Data пристрою, перші і другі входи реконфігуратора вихідних даних підключені до виходів основного і запасного масивів запам'ятовуючих комірок відповідно, перші виходи блока відновлення працездатності підключені до третіх входів реконфігуратора вихідних даних і перших входів реконфігуратора вхідних даних, виходи якого підключені до третіх входів запасного масиву запам'ятовуючих комірок, виходи мультиплексора коду даних підключені до других входів реконфігуратора вхідних даних, другі виходи компаратора підключені до перших входів блока відновлення працездатності, четверті входи компаратора підключені до четвертих виходів контролера самотестування, п'ятий вихід якого підключено до другого входу блока відновлення працездатності, другий вихід якого підключено до виводу Fail пристрою. В основі запропонованої моделі поставлена задача виявлення відмов основного масиву запам'ятовуючих комірок за допомогою вбудованих засобів самотестування і виконання відновлення працездатності шляхом заміни розрядів даних основного масиву, що відмовили, на розряди даних резервного масиву запам'ятовуючих комірок. При цьому можливе відновлення працездатності при багатократних відмовах. На фіг. 1 приведена структурна схема напівпровідникового запам'ятовуючого пристрою з відновленням працездатності при багатократних відмовах. На фіг. 2 зображена структурна схема блока відновлення працездатності. 1 UA 82607 U 5 10 15 20 25 30 35 40 45 50 55 60 На фіг. 3 приведена структурна схема реконфігуратора вхідних даних. На фіг. 4 зображена структурна схема реконфігуратора вихідних даних. На фіг. 5 наведено формат мікрокоманд і мікрооперацій. На фіг. 1 приведена структурна схема напівпровідникового запам'ятовуючого пристрою з відновленням працездатності при багатократних відмовах, яка містить основний 1 та запасний 2 масиви запам'ятовуючих комірок, контролер самотестування 3, генератори кодів адреси 4 і даних 5, мультиплексори кодів операцій 6, адреси 7 і даних 8, компаратор 9, блок відновлення працездатності 10, реконфігуратор вхідних даних 11 і реконфігуратор вихідних даних 12, причому перші, другі і треті виходи контролера самотестування 3 підключені до перших входів мультиплексора коду операцій 6, генератора коду адреси 4 і генератора коду даних 5 відповідно, перший, другий і третій входи контролера самотестування 3 підключені до виводів ST, CLK і RST пристрою відповідно, другі входи мультиплексорів кодів операцій 6, адреси 7 і даних 8 підключені до виводів WR, Sys_Address, Sys_Data пристрою відповідно, виходи мультиплексорів коду операцій 6 і коду адреси 7 підключені до перших і других входів основного 1 і запасного 2 масивів запам'ятовуючих комірок відповідно, виходи генератора коду адреси 4 підключені до перших входів мультиплексора кодів адреси 7, виходи генератора коду даних 5 підключені до перших входів мультиплексора коду даних 8 і перших входів компаратора 9, другі і треті входи якого підключені до виходів основного 1 і запасного 2 масивів запам'ятовуючих комірок відповідно, перший вихід компаратора 9 підключено до четвертого входу контролера самотестування 3 і виводу Т пристрою, виходи реконфігуратора вихідних даних 12 підключені до виводів Data пристрою, перші і другі входи реконфігуратора вихідних даних 12 підключені до виходів основного 1 і запасного 2 масивів запам'ятовуючих комірок відповідно, перші виходи блока відновлення працездатності 10 підключені до третіх входів реконфігуратора вихідних даних 12 і перших входів реконфігуратора вхідних даних 11, виходи якого підключені до третіх входів запасного 2 масиву запам'ятовуючих комірок, виходи мультиплексора коду даних 8 підключені до других входів реконфігуратора вхідних даних 11, другі виходи компаратора 9 підключені до перших входів блока відновлення працездатності 10, четверті входи компаратора 9 підключені до четвертих виходів контролера самотестування 3, п'ятий вихід якого підключено до другого входу блока відновлення працездатності 10, другий вихід якого підключено до виводу Fail пристрою. На фіг. 2 зображена структурна схема блока відновлення працездатності, яка містить зсувний регістр 13, лічильник позицій бітів 14, D-тригер 15, логічні елементи 16-18, 21-23, лічильник числа відмов 19, дешифратор 20 позицій бітів, групу логічних елементів 24.1-24.р і Dтригер 25. До регістру 13 з компаратора 9 заздалегідь заноситься вектор відмов, сформований після виконання операції самотестування пристрою. Після подання сигналу Р регістр 13 перемикається до режиму зсуву вправо і число відмов запам'ятовується лічильником 19. Код позиції кожного біту вектора відмов запам'ятовується лічильником 14, дешифрується дешифратором 20 і надходить на входи елементів 24.1-24.р. Стани лічильника 19 використовуються для управління роботою реконфігуратора вхідних даних 11 і реконфігуратора вихідних даних 12. Якщо кількість розрядів даних, що відмовили, основного 1 масиву запам'ятовуючих комірок більша чотирьох, то в даній моделі відновлення працездатності неможливе і за допомогою логічних елементів 21-24 і D-тригеру 25 на виході пристрою діагностується сигнал Fail (невдача). На фіг. 3 приведена структурна схема реконфігуратора вхідних даних, що забезпечує відновлення працездатності при чотирьохкратних відмовах в різних розрядах даних і складається з дешифратора 26, регістрів 27-30 та мультиплексорів 31-34. В початковому стані регістри 27-30 знаходяться в нульовому стані і на виходи мультиплексорів 31-34 надходять дані з виходів мультиплексора вхідних даних 8, призначені для діагностування працездатного або непрацездатного стану запасного 2 масиву запам'ятовуючих комірок. При виявлені відмов компонентів основного 1 масиву запам'ятовуючих комірок до регістру 27 заноситься код позиції першої відмови, до регістру 28 - другої відмови, до регістру 29 третьої відмови, до регістру 30 – четвертої другої відмови, до регістру 29 - третьої відмови, до регістру 30 - четвертої відмови. Через мультиплексори 31-34 коди станів регістрів 27-30 забезпечують перемикання вхідних даних розрядів, що відмовили, основного 1 масиву запам'ятовуючих комірок, на входи резервного 2 масиву запам'ятовуючих комірок. На фіг. 4 зображена структурна схема реконфігуратора вихідних даних, яка містить регістри 35.1-35.р і мультиплексори 36.1-36.р. На інформаційні входи регістрів 35.1-35.р надходять коди номеру виявленої відмови, а номер виявленої відмови забезпечує вибірку відповідного розряду 2 UA 82607 U 5 10 15 20 25 30 35 40 45 50 55 даних основного 1 масиву запам'ятовуючих комірок, який підлягає заміні на розряд даних запасного 2 масиву запам'ятовуючих комірок. Заміна першого розряду, що відмовив, основного 1 масиву запам'ятовуючих комірок відбувається на перший розряд даних запасного 2 масиву запам'ятовуючих комірок, друга відмова - на другий розряд, третя - на третій розряд, четверта - на четвертий розряд. На фіг. 5 наведено формат мікрокоманд і мікрооперацій, який складається з наступних полів: - коду мікрокоманди; - робочих операцій: запису (W), зчитування (R), порівняння (А) і відновлення працездатності (Р); - коду мікрооперацій адреси; - коду мікрооперацій даних; - адреси переходу. Для формування тестів використовуються наступні мікрокоманди: NOOP - відсутність операції, забезпечує перехід до наступної мікрокоманди; JANN - перехід до команди, код адреси якої записано у полі адреси переходу, якщо поточна адреса комірок пам'яті не дорівнює адресі кінцевої комірки (АN); JANG - перехід до команди, код адреси якої записано у полі адреси переходу, якщо поточна адреса комірок пам'яті не дорівнює адресі початкової комірки (АС); JUMP - безумовний перехід до команди, код адреси якої записано у полі адреси переходу; JKNZ - умовний перехід до команди, код адреси якої записано у полі адреси переходу, якщо при порівнянні зчитаних даних з еталонними значеннями виявлена розбіжність кодів (К0); ENDE - зупинка при виявленні несправностей пристрою, що діагностується; ENDP - зупинка при відсутності несправностей пристрою, що діагностується. Напівпровідниковий запам'ятовуючий пристрій працює наступним чином. Для ініціалізації пристрою на вхід RST подається сигнал високого рівня напруги, який забезпечує встановлення у початковий стан усіх компонентів пристрою. Після подання на вхід ST пристрою стартового сигналу контролер самотестування 3 ініціалізує роботу генератора коду адреси 4 і генератора коду даних 5 за програмою, яка зберігається у пам'яті мікроконтролера. При виконанні самотестування зчитані дані з входів блоків 1 і 2 подаються на входи компаратора 9 та порівнюються з еталонними даними, які находять з виходів генератора коду даних 5. Вектор результатів самотестування запам'ятовується в регістрі зсуву 13. Результат самотестування пристрою передається на вивід Т та використовується для визначення стану пристрою. За наявності високого рівня напруги на виводі Т мікросхема вважається непрацездатною, але при кількості розрядів даних, що відмовили, менше чотирьох можливе відновлення працездатного стану. Якщо зафіксовані відмови основного 1 масиву запам'ятовуючих комірок, то за сигналом Р, що формується контролером 3, ініціалізується процес відновлення працездатності пристрою. Регістр 13 здійснює зсув коду вектора результату самотестування. Число операцій зсуву кодів, які виконуються регістром 13, обмежено і дорівнює числу інформаційних розрядів основного 1 масиву запам'ятовуючих комірок. Лічильник позицій бітів вектора відмов 14 і лічильник відмов 19 здійснюють управління реконфігураторами вхідних 11 і вихідних 12 даних, які забезпечують заміну розрядів даних, що відмовили, основного масиву 1 запам'ятовуючих комірок на запасний масив 2 запам'ятовуючих комірок. Таким чином, забезпечується автоматичне відновлення працездатності запам'ятовуючого пристрою при багатократних відмовах. Техніко-економічний ефект при застосуванні заявленої моделі досягається за рахунок підвищення надійності роботи напівпровідникового запам'ятовуючого пристрою шляхом автоматичного відновлення працездатності після виникнення багатократних відмов. Джерела інформації: 1. Патент США. Redundancy Analysis for Embedded Memories with Built-In Self Test and Built-In Self Repair. N6067262, Int.C1. G11С 7/00. May 23, 2000. 2. Патент США. Built-In Spare Row and Column Replacement Analysis System for Embedded Memories. N6304989, Int.C1. G01R 31/28. Oct. 16, 2001. 3 UA 82607 U ФОРМУЛА КОРИСНОЇ МОДЕЛІ 5 10 15 20 25 Напівпровідниковий запам'ятовуючий пристрій з відновленням працездатності при багатократних відмовах, який містить основний і запасний масиви запам'ятовуючих комірок, контролер самотестування, генератори кодів адреси і даних, мультиплексори кодів операцій, адреси і даних, компаратор, причому перші, другі і треті виходи контролера самотестування підключені до перших входів мультиплексора коду операцій, генератора коду адреси і генератора коду даних відповідно, перший, другий, третій входи контролера самотестування підключені до виводів ST, CLK і RST пристрою відповідно, другі входи мультиплексорів кодів операцій, адреси і даних підключені до виводів WR, Sys_Address, Sys_Data пристрою відповідно, виходи мультиплексорів коду операцій і коду адреси підключені до перших і других входів основного і запасного масивів запам'ятовуючих комірок відповідно, виходи генератора коду адреси підключені до перших входів мультиплексора кодів адреси, виходи генератора коду даних підключені до перших входів мультиплексора коду даних і перших входів компаратора, другі і треті входи якого підключені до виходів основного і запасного масивів запам'ятовуючих комірок відповідно, перший вихід компаратора підключено до четвертого входу контролера самотестування і виводу Т пристрою, який відрізняється тим, що в нього додатково введені блок відновлення працездатності, реконфігуратор вхідних даних і реконфігуратор вихідних даних, виходи якого підключені до виводів Data пристрою, перші і другі входи реконфігуратора вихідних даних підключені до виходів основного і запасного масивів запам'ятовуючих комірок відповідно, перші виходи блока відновлення працездатності підключені до третіх входів реконфігуратора вихідних даних і перших входів реконфігуратора вхідних даних, виходи якого підключені до третіх входів запасного масиву запам'ятовуючих комірок, виходи мультиплексора коду даних підключені до других входів реконфігуратора вхідних даних, другі виходи компаратора підключені до перших входів блока відновлення працездатності, четверті входи компаратора підключені до четвертих виходів контролера самотестування, п'ятий вихід якого підключено до другого входу блока відновлення працездатності, другий вихід якого підключено до виводу Fail пристрою. 4 UA 82607 U 5 UA 82607 U 6 UA 82607 U Комп’ютерна верстка М. Мацело Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 7

ДивитисяДодаткова інформація

Назва патенту англійськоюSemiconductor memory with multiple failure recovery

Автори англійськоюAndrienko Volodymyr Oleksandrovych, Kolpakov Ivan Oleksandrovych, Riabtsev Volodymyr Hryhorovych, Utkina Tetiana Yuriivna

Назва патенту російськоюПолупроводниковое запоминающее устройство с восстановлением работоспособности при многократных отказах

Автори російськоюАндриенко Владимир Александрович, Колпаков Иван Александрович, Рябцев Владимир Григорьевич, Уткина Татьяна Юрьевна

МПК / Мітки

МПК: G11C 7/00

Мітки: відмовах, багатократних, відновленням, працездатності, напівпровідниковий, пристрій, запам'ятовуючий

Код посилання

<a href="https://ua.patents.su/9-82607-napivprovidnikovijj-zapamyatovuyuchijj-pristrijj-z-vidnovlennyam-pracezdatnosti-pri-bagatokratnikh-vidmovakh.html" target="_blank" rel="follow" title="База патентів України">Напівпровідниковий запам’ятовуючий пристрій з відновленням працездатності при багатократних відмовах</a>

Попередній патент: Туберкуліногенний штам, виділений із мікобактерій пташиного виду m. avium-іеквм для виготовлення туберкуліну очищеного для птиці

Наступний патент: Масажний пристрій

Випадковий патент: Спосіб деамонізації конденсатів цукрового виробництва