Спосіб виготовлення напівпровідникового елемента з окремо розміщеним в підкладці з’єднувальним елементом, а також напівпровідниковий елемент, виготовлений цим способом

Номер патенту: 57865

Опубліковано: 15.07.2003

Автори: Плаза Гюнтер, Кукс Андреас, Штокан Регіна, Браун Хельга, Какошке Рональд

Формула / Реферат

1. Спосіб виготовлення напівпровідникового елемента, що містить щонайменше частково розміщену у підкладці з'єднувальну систему, причому він містить щонайменше один розміщений у напівпровідниковій підкладці електропровідний з'єднувальний елемент (24) і щонайменше один розміщений на напівпровідниковій підкладці електропровідний з'єднувальний елемент (14, 18), причому спосіб узгоджений зі способом виготовлення МОН-транзисторів щонайменше двох типів, і включає такі етапи:

а) підготовлюють напівпровідникову підкладку (1), що містить щонайменше одну першу область (3) другого типу провідності для транзисторів першого типу і другу область (5) першого типу провідності для транзисторів другого типу,

б) на напівпровідникову підкладку (1) наносять перший ізоляційний шар (8),

в) легуючий матеріал першого типу провідності наносять у першій області (3) в зоні майбутньої точки перетину розміщеного у напівпровідниковій підкладці (1) електропровідного з'єднувального елемента (24) і розміщеного на напівпровідниковій підкладці (1) електропровідного з'єднувального елемента (14) і/або легуючий матеріал другого типу провідності наносять у другій області (5) в зоні майбутньої точки перетину розміщеного у напівпровідниковій підкладці (1) електропровідного з'єднувального елемента (24) і розміщеного на напівпровідниковій підкладці електропровідного з'єднувального елемента (18),

г) на перший ізоляційний шар (8) наносять електропровідний шар (10),

д) за допомогою фототехніки наносять першу маску (12), яка покриває другу область (5) майже повністю, а у першій області (3) в основному покриває лише доріжки затворів виготовлюваних транзисторів першого типу, а також при необхідності розміщений на напівпровідниковій підкладці (1) електропровідний з'єднувальний елемент (14),

е) першу маску (12) використовують для перетворення електропровідного шару (10) у другий ізоляційний шар (22) або для його видалення і внесення у напівпровідникову підкладку (1) щонайменше одного легуючого матеріалу (15) першого типу провідності,

є) за допомогою фототехніки наносять другу маску (17), яка майже повністю покриває першу область (3), а у другій області (5) в основному покриває лише доріжки затворів виготовлюваних транзисторів другого типу, а також при необхідності розміщений на напівпровідниковій підкладці (1) електропровідний з'єднувальний елемент (18) і першу область (3),

ж) другу маску (17) використовують для перетворення електропровідного шару (10) у другий ізоляційний шар (22) або для його видалення і внесення у напівпровідникову підкладку (1) щонайменше одного легуючого матеріалу (20) другого типу провідності,

з) шляхом підвищення температури легуючих матеріалів, нанесених в зоні точки перетину і за допомогою першої чи другої масок, формують розміщений в напівпровідниковій підкладці електропровідний з'єднувальний елемент (24).

2. Спосіб за п. 1, який відрізняється тим, що між першою і другою областями (З, 5) передбачають область (19), не покриту жодною з масок (12, 17).

3. Спосіб за пп. 1 або 2, який відрізняється тим, що на електропровідний шар (10) наносять захисний шар (11), який після нанесення маски (масок) (12, 17) видаляють відповідно до маски (масок) (12, 17).

4. Спосіб за п. 3, який відрізняється тим, що захисний шар (11) виконують у вигляді оксидно-нітридно-оксидного шару.

5. Спосіб за одним із пп. 1-4, який відрізняється тим, що електропровідний шар (10) виконують у вигляді полікремнієвого шару.

6. Спосіб за п. 5, який відрізняється тим, що полікремнієвий шар (10) шляхом оксидування перетворюють у другий ізоляційний шар (22).

7. Спосіб за п. 5, який відрізняється тим, що полікремнієвий шар (10) перетворюють у другий ізоляційний шар (22) шляхом видалення частини полікремнієвого шару (10) і перетворення решти цього шару (10) у шар (22) оксиду кремнію шляхом оксидування.

8. Спосіб за одним із пп. 1-7, який відрізняється тим, що легуючий матеріал (15, 20) вводять у напівпровідникову підкладку (1) шляхом імплантації з наступною тепловою обробкою.

9. Спосіб за п. 5, який відрізняється тим, що легуючий матеріал (15, 20) вводять у напівпровідникову підкладку (1) шляхом нагрівання при оксидуванні полікремнію.

10. Спосіб за одним із пп. 1-9, який відрізняється тим, що перша і друга області (З, 5) мають зони (32, 34), передбачені для контактів підкладки, перша маска (12) над зонами (32) другої області (5), передбаченими для контактів підкладки, має отвори і накриває зони (34) першої області (3), призначені для контактів підкладки, а друга маска (17) над зонами (34) першої області (3), передбаченими для контактів підкладки, має отвори і накриває зони (32) другої області (5), призначені для контактів підкладки.

11. Спосіб за одним із пп. 1-10, який відрізняється тим, що у попередньо заданих областях (3, 5), в яких мають бути розміщені транзистори, утворюють ізоляційні зони, зокрема зони товстого шару оксиду або зони з мілкими ізоляційними канавками, які обмежують транзистори.

12. Напівпровідниковий елемент, що містить щонайменше частково розміщену у підкладці з'єднувальну систему, який відрізняється тим, що він виготовлений способом за одним із пунктів 1-11.

Текст

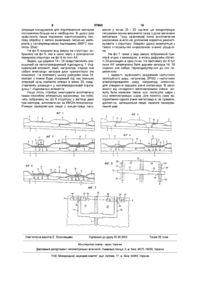

1 Спосіб виготовлення напівпровідникового елемента, що містить щонайменше частково розміщену у підкладці з'єднувальну систему, причому він містить щонайменше один розміщений у напівпровідниковій підкладці електропровідний з'єднувальний елемент (24) і щонайменше один розміщений на напівпровідниковій підкладці електропровідний з'єднувальний елемент (14, 18), причому спосіб узгоджений зі способом виготовлення МОН-транзисторів щонайменше двох типів, і включає такі етапи а) підготовлюють напівпровідникову підкладку (1), що містить щонайменше одну першу область (3) другого типу провідності для транзисторів першого типу і другу область (5) першого типу провідності для транзисторів другого типу, б) на напівпровідникову підкладку (1) наносять перший ІЗОЛЯЦІЙНИЙ шар (8), в) легуючий матеріал першого типу провідності наносять у першій області (3) в зоні майбутньої точки перетину розміщеного у напівпровідниковій підкладці (1) електропровідного з'єднувального елемента (24) і розміщеного на напівпровідниковій підкладці (1) електропровідного з'єднувального елемента (14) і/або легуючий матеріал другого типу провідності наносять у другій області (5) в зоні майбутньої точки перетину розміщеного у напівпровідниковій підкладці (1) електропровідного з'єднувального елемента (24) і розміщеного на напівпровідниковій підкладці електропровідного з'єднувального елемента (18), г) на перший ІЗОЛЯЦІЙНИЙ шар (8) наносять електропровідний шар (10), д) за допомогою фототехніки наносять першу маску (12), яка покриває другу область (5) майже повністю, а у першій області (3) в основному покриває лише доріжки затворів виготовлюваних транзисторів першого типу, а також при необхідності розміщений на напівпровідниковій підкладці (1) електропровідний з'єднувальний елемент (14), є) першу маску (12) використовують для перетворення електропровідного шару (10) у другий ІЗОЛЯЦІЙНИЙ шар (22) або для його видалення і внесення у напівпровідникову підкладку (1) щонайменше одного легуючого матеріалу (15) першого типу провідності, є) за допомогою фототехніки наносять другу маску (17), яка майже повністю покриває першу область (3), а у другій області (5) в основному покриває лише доріжки затворів виготовлюваних транзисторів другого типу, а також при необхідності розміщений на напівпровідниковій підкладці (1) електропровідний з'єднувальний елемент (18) і першу область (3), ж) другу маску (17) використовують для перетворення електропровідного шару (10) у другий ІЗОЛЯЦІЙНИЙ шар (22) або для його видалення і внесення у напівпровідникову підкладку (1) щонайменше одного легуючого матеріалу (20) другого типу провідності, з) шляхом підвищення температури легуючих матеріалів, нанесених в зоні точки перетину і за допомогою першої чи другої масок, формують розміщений в напівпровідниковій підкладці електропровідний з'єднувальний елемент (24) 2 Спосіб за п 1, який відрізняється тим, що між першою і другою областями (3, 5) передбачають область (19), не покриту жодною з масок (12, 17) 3 Спосіб за пп 1 або 2, який відрізняється тим, що на електропровідний шар (10) наносять захисний шар (11), який після нанесення маски (масок) (12, 17) видаляють ВІДПОВІДНО ДО маски (масок) (12, 17) О ю (О 00 ю 4 Спосіб за п 3, який відрізняється тим, що захисний шар (11) виконують у вигляді оксиднонітридно-оксидного шару 5 Спосіб за одним із пп 1-4, який відрізняється тим, що електропровідний шар (10) виконують у вигляді полікремнієвого шару 6 Спосіб за п 5, який відрізняється тим, що полікремнієвий шар (10) шляхом оксидування перетворюють у другий ІЗОЛЯЦІЙНИЙ шар (22) 7 Спосіб за п 5, який відрізняється тим, що полікремнієвий шар (10) перетворюють у другий ІЗОЛЯЦІЙНИЙ шар (22) шляхом видалення частини полікремнієвого шару (10) і перетворення решти цього шару (10) у шар (22) оксиду кремнію шляхом оксидування 8 Спосіб за одним із пп 1-7, який відрізняється тим, що легуючий матеріал (15, 20) вводять у напівпровідникову підкладку (1) шляхом імплантації з наступною тепловою обробкою 9 Спосіб за п 5, який відрізняється тим, що легуючий матеріал (15, 20) вводять у напівпровідникову підкладку (1) шляхом нагрівання при оксидуванні полікремнію Винахід стосується способу виготовлення напівпровідникового елемента, що містить частково розміщену в підклад ці з'єднувальну систему, а також напівпровідниковий елемент, виготовлений цим способом Напівпровідникові елементи з окремо розміщеними у підклад ці з'єднувальними елементами ВІДОМІ, наприклад, із опису DE 35 02 713 А1 і з викладеного опису винаходу до DE 16 14 250 Інтегральні мікросхеми, зокрема мікросхеми, що містять комплементарні структури "металоксид-напівпровідник" (КМОН-мікросхеми), виготовляються в ході великої КІЛЬКОСТІ, технологічних операцій Витрати на виготовлення цих мікросхем визначаються складністю процесів і часом фізичної обробки Складні модулі часто потребують виконання кількох сотень технологічних операцій і виготовлення їх триває багато днів При цьому частина технологічних процесів має бути виконана для виготовлення з'єднувальних елементів, що з'єднують між собою окремі активні елементи мікросхеми або забезпечують зв'язок інтегральної схеми із "ЗОВНІШНІМ СВІТОМ" Зазвичай такі з'єднання реалізуються одним чи кількома рівнями провідників із алюмінію Одначе с застосування, при яких рівні провідників із алюмінію є, по-перше, надто дорогими, а, по-друге, потребують надто великої площі До того ж, інтегральні мікросхеми з алюмінієвими з'єднувальними елементами не в достатній мірі захищені від ЗОВНІШНІХ зловмисних маніпуляцій або від інженерного аналізу структури схеми Для здійснення таких маніпуляцій у інтегральних мікросхемах спочатку має бути проаналізована сама схема Для цього шар за шаром мають бути зняті пасивувальний шар чи ІЗОЛЯЦІЙНІ шари між з'єднувальними рівнями для вивчення звільнених таким чином з'єднувальних рівнів При цьо 57865 10 Спосіб за одним із пп 1-9, який відрізняється тим, що перша і друга області (3, 5) мають зони (32, 34), передбачені для контактів підкладки, перша маска (12) над зонами (32) другої області (5), передбаченими для контактів підкладки, має отвори і накриває зони (34) першої області (3), призначені для контактів підкладки, а друга маска (17) над зонами (34) першої області (3), передбаченими для контактів підкладки, має отвори і накриває зони (32) другої області (5), призначені для контактів підкладки 11 Спосіб за одним із пп 1-10, який відрізняється тим, що у попередньо заданих областях (3, 5), в яких мають бути розміщені транзистори, утворюють ІЗОЛЯЦІЙНІ зони, зокрема зони товстого шару оксиду або зони з мілкими ІЗОЛЯЦІЙНИМИ канавками, які обмежують транзистори 12 Напівпровідниковий елемент, що містить щонайменше частково розміщену у підкладці з'єднувальну систему, який відрізняється тим, що він виготовлений способом за одним із пунктів 1-11 му якщо з єднувальні рівні виконані із алюмінію, то такий аналіз схеми може бути здійснений порівняно просто Тому в основі винаходу лежить задача розробки способу виготовлення напівпровідникового елемента з окремо розміщеними в підкладинці з'єднувальними елементами, а також напівпровідникового елемента, виготовленого цим способом, в якому значно утруднене здійснення аналізу структури інтегральної мікросхеми, а також маніпуляцій Крім того, спосіб виготовлення таких з'єднувальних елементів має бути добре узгодженим зі способом виготовлення транзисторів і потребувати якомога меншої КІЛЬКОСТІ технологічних операцій Ця задача вирішена у способі згідно з п 1 формули винаходу, а також у , напівпровідниковому елементі згідно з п 12 формули винаходу, ІНШІ ВИГІДНІ форми виконання, оформлення і аспекти даного винаходу відображені у додаткових пунктах формули винаходу і доданих кресленнях Згідно З винаходом, розроблено спосіб виготовлення напівпровідникового елемента, що містить щонайменше частково розміщену у підкладинці з'єднувальну систему причому він містить щонайменше один розміщений у напівпровідниковій підкладинці електропровідний з'єднувальний елемент і щонайменше один розміщений на напівпровідниковій підкладинці електропровідний з'єднувальний елемент Винайдений спосіб включає такі кроки а) підготовлюють напівпровідникову підкладинку, що містить щонайменше дві області, причому у першій області розміщені транзистори першого типу, а у другій області розміщені транзистори другого типу, б) на напівпровідникову підкладинку наносять перший ІЗОЛЯЦІЙНИЙ шар, в) легувальний матеріал першого типу провідності наносять у першій області в зоні майбутньої точки перетину розміщеного у напівпровідниковій під кладинці електропровідного з'єднувального елемента і розміщеного на напівпровідниковій підкладинці електропровідного з'єднувального елемента і/або легуючий матеріал другого типу провідності наносять у другій області в зоні майбутньої точки перетину розміщеного у напівпровідниковій під кладинці електропровідного з'єднувального елемента і розміщеного на напівпровідниковій підкладинці електропровідного з'єднувального елемента г) на перший ІЗОЛЯЦІЙНИЙ шар наносять електропровідний шар, д) за допомогою фототехніки наносять першу маску, яка у першій області в основному покриває лише доріжки затворів виготовлюваних транзисторів першого типу, а також при необхідності майже повністю покриває розміщені на напівпровідниковій підкладинці електропровідні з'єднувальні елементи і другу область, є) ВІДПОВІДНО до цієї першої маски електропровідний шар перетворюють у другий ІЗОЛЯЦІЙНИЙ шар або видаляють і у напівпровідникову підкладинку вносять щонайменше один легуючий матеріал першого типу провідності, є) за допомогою фототехніки наносять другу маску, яка у другій області в основному покриває лише доріжки затворів виготовлюваних транзисторів другого типу, а також при необхідності майже повністю покриває розміщені на напівпровідниковій підкладинці електропровідні з'єднувальні елементи і першу область, ж) ВІДПОВІДНО до цієї другої маски електропровідний шар перетворюють у другий ІЗОЛЯЦІЙНИЙ шар або видаляють і у напівпровідникову підкладинку вносять щонайменше один легуючий матеріал другого типу провідності внаслідок чого легуючими матеріалами, нанесеними в зонах точок перетину і за допомогою першої чи другої масок, утворюються розміщені в напівпровідниковій підкладинці електропровідні з'єднувальні елементи Кроки способу не обов'язково мають виконуватися у вказаній ПОСЛІДОВНОСТІ, зокрема кроки б) і в) у загальному технологічному процесі можуть бути ПОМІНЯНІ місцями Виготовлені згідно з винаходом напівпровідникові елементи містять розміщені під рівнем затворів низькоомні з'єднувальні елементи, завдяки чому значно утруднюється зловмисний аналіз схеми Тому напівпровідникові елементи згідно з винаходом придатні для застосувань, в яких висуваються вимоги високої безпеки проти ЗОВНІШНІХ маніпуляцій Додатковою перевагою винайденого способу є також те, що для виготовлення транзисторів щонайменше двох типів, наприклад, рМОН- і пМОНтранзисторів, а також розміщених у підкладинці з'єднувальних елементів потрібні лише три фоторівні, тоді як звичайні способи виготовлення потребують 6 або більше фоторівнів У способі згідно з винаходом маски, виготовлені за допомогою фототехніки, служать як для структурування доріжок затворів і розміщених на підкладинці з'єднувальних елементів, так і для внесення легуючого матеріалу для утворення областей витік/сток і розмі 57865 щених у підкладинці зєднувальних елементів Завдяки економії трьох фоторівнів, технологічний процес виготовлення значно спрощується, прискорюється і тому здешевлюється Такі інтегральні мікросхеми можуть знайти застосування у випадках, коли йдеться про низькі витрати на виготовлення У способі згідно з винаходом доцільним є зокрема полишення між першою І другою областями зони (чи зон), не накритої жодною із двох масок Таким чином забезпечується, що у рівні електропровідного шару лише дійсно передбачені з'єднувальні елементи утворюють електропровідне з'єднання між першою і другою областями Крім того, доцільним є нанесення на електропровідний шар захисного шару, зокрема шару оксид-нітрит-оксид, який після нанесення масок видаляють ВІДПОВІДНО до цих масок Доцільним Є також виготовлення електропровідного шару із полікристалічного кремнію Згідно З формою виконання винаходу, шар полікристалічного кремнію шляхом оксидування перетворюють у другий ІЗОЛЯЦІЙНИЙ шар При цьому особливо доцільним є перетворення шару полікристалічного кремнію у другий ІЗОЛЯЦІЙНИЙ шар шляхом видалення частини шару полікристалічного кремнію і перетворення залишеної частини у шар оксиду кремнію шляхом оксидування Крім того, доцільним є нанесення легуючого матеріалу шляхом імплантації у напівпровідникову підкладинку з на поступною тепловою обробкою При цьому для вживления легувального матеріалу може бути використана висока температура, необхідна при оксидуванні шару полікристалічного кремнію До того ж доцільним є варіант, у якому перша і друга області мають зони, передбачені для контактів підкладинки, перша маска над зонами другої області, передбаченими для контактів підкладинки, має отвори і накриває зони першої області, призначені для контактів підкладинки, а друга маска над зонами першої області, передбаченими для контактів підкладинки, має отвори, і накриває зони другої області, призначені для контактів підкладинки Крім того, доцільним є варіант, у якому в областях, де мають бути розміщені транзистори, передбачені ІЗОЛЯЦІЙНІ зони, зокрема зони товстого шару оксиду або зони з мілкими ІЗОЛЯЦІЙНИМИ канавками, які обмежують транзистори Нижче винахід детальніше пояснюється з використанням фігур На них схематично зображено Фіг 1-5 поперечний переріз напівпровідникового елемента на різних стадіях способу згідно з винаходом, Фіг 6 і 7 види на варіанти виконання структури, зображеної в перерізі на фіг 4 На фіг 1 зображена напівпровідникова підкладинка 1, підготовлена як вихідний пункт для способу згідно з винаходом У напівпровідниковій підкладинці 1, що має провідність р-типу, виконано кишеню 2, що має провідність n-типу, п-кишеня 2 визначає одну із областей 3, яка пізніше прийме рдифузію з утворенням електропровідного з'єднувального елемента Крім того, у напівпровідниковій підкладинці 1 виконано кишеню 4, що має про 57865 15 2 БІДНІСТЬ р-типу, р-кишеня 4 також визначає одну із імплантації 20кеВ, доза імплантації 2-10 см ) областей 5, яка пізніше прийме n-дифузію з утвоОскільки надалі імплантовані у ІЗОЛЯЦІЙНИЙ шар 6 ренням електропровідного з'єднувального елемеатоми бору не грають ніякої ролі, на фіг 3 показано нта, У напівпровідниковій підкладинці 1 у вигляді лише атоми бору, імплантовані у напівпровідникозони товстого шару оксиду виконано ІЗОЛЯЦІЙНІ ву підкладинку 1 зони 6, які латеральне ізолюють один від іншого При цьому після структурування захисного окремі з'єднувальні елементи Для покращення шару 11 або після структурування електропровідІзоляції під зонами товстого шару оксиду додатконого шару 10 маску 12 можна було б видалити, во виконано польові імплантовані зони 7 одначе краще її залишити до закінчення імплантації легувального матеріалу Таким чином може На підготовлену таким чином напівпровідникобути використаний порівняно тонкий електропрову підкладинку 1 наносять оксидний шар 8 як ІЗОвідний шар, який викликає лише незначні ВІДМІНЛЯЦІЙНИЙ шар між зонами товстого шару оксиду НОСТІ топології на поверхні підкладинки Цей оксидний шар 8 в подальшому в інших областях напівпровідникової підкладинки 1 служить окПісля закінчення імплантації бору першу маску сидним шаром затворів транзисторів, що ще ма12 видаляють і за допомогою фототехніки наноють бути виготовлені (не показані) Отримана в сять другу маску 17 При цьому друга маска 17 над результаті структура зображена на фіг 1 р-кишенею 4 накриває лише з'єднувальний елемент 18 і майже повністю покриває п-кишеню 2 Потім за допомогою фототехніки у п-кишені 2 напівпровідникової підкладинки 1 імплантують Над зоною 19 (див фіг 4) між обома кишенями атоми бору 33 (енергія імплантації 20кеВ, доза 2 і 4 маска 17 дещо відтягнута назад, внаслідок імплантації 2-Ю1 см При цьому атоми бору імчого також і ця зона залишається вільною плантують у зону 23, яка пізніше утворить точку ВІДПОВІДНО ДО ЦІЄЇ другої маски 17 шляхом перетину між розміщеними у напівпровідниковій травлення видаляють ще наявні, тепер відкриті підкладинці електропровідними з'єднувальними частини оксидно-нітридно-оксидного шару 11 крім елементами 24 і розміщеними на напівпровідникотого, ВІДПОВІДНО до цієї другої маски 17 видаляють вій підкладинці електропровідними з'єднувальнище наявні, відкриті частини полікремнієвого шару ми елементами 14 (див, фіг 6) 10 до попередньо заданої товщини Завдяки цьоПотім за допомогою фототехніки у р-кишені 4 му у зоні 19 між першою і другою областями, не напівпровідникової підкладинки 1 імплантують покритими обома масками, полікремнієвий шар 10 атоми фосфору 35 (енергія імплантації 20кеВ, довидаляється повністю 1Д У Нарешті, ВІДПОВІДНО до цієї другої маски 17 у за імплантації 2-10 см ) При цьому атоми фоснапівпровідникову підкладинку 1 і у ІЗОЛЯЦІЙНИЙ фору імплантують у зону 25, яка пізніше утворить шар 6 імплантують атоми 20 фосфору і/або миш'яточку перетину між розміщеними у напівпровіднику (фосфор енергія імплантації ІЗОкеВ, доза їмковій підкладинці електропровідними з'єднувальними елементами 24 і розміщеними на напівпровідниковій підкладинці електропровідними з'єднувальними елементами 18 (див фіг 6) Отримана в результаті структура зображена на фіг 2 Потім методом осадження із газової фази на оксидний шар 8 і ІЗОЛЯЦІЙНІ ЗОНИ 6 як електропро відний шар наносять шар 10 полікристалічного кремнію При цьому полікремнієвий шар 10 має товщину, наприклад 150нм і п*-легування 2 0-10 см це легування може бути здійснене одночасно із осадженням шляхом додаткової імплантації або так званого POCL-покриття Потім виконують осадження оксидно-нітридного шару на полікремнієвий шар 10, причому пізніше із оксидно-нітридного шару шляхом оксидування утворюють оксидно-нітридно-оксидний захисний шар 11 За допомогою фототехніки на оксиднонітридно-оксидний шар 11 наносять першу маску 12 Прицьому перша маска 12 над n-кишенею покриває в основному лише з'єднувальний елемент 14, а р-кишеню 4 покриває майже повністю Над зоною 19 (див фіг 4) між обома кишенями 2 і 4 маска 12 дещо відтягнута назад, внаслідок чого також і ця зона залишається вільною ВІДПОВІДНО ДО ЦІЄЇ першої маски 12 ВІЛЬНІ час тини оксидно-нітридно-оксидного шару 11 видаляють шляхом травлення Крім того, ВІДПОВІДНО ДО цієї першої маски 12 видаляють відкриту частину полікремнієвого шару 10 до попередньо заданої товщини і, нарешті, ВІДПОВІДНО ДО ЦІЄЇ першої маски 12 у напівпровідникову підкладинку 1 і ІЗОЛЯЦІЙНИЙ шар 6 імплантують атоми бору 15 (енергія 1Д ? плантації 1-10 см , миш'як енергія імплантації 150кеВ, доза імплантації 2-1015см 2) Оскільки надалі імплантовані у ІЗОЛЯЦІЙНИЙ шар 6 атоми легуючих матеріалів не грають ніякої ролі, на фіг 4 показано лише атоми легуючих матеріалів, імплантовані у напівпровідникову підкладинку 1 Після закінчення імплантації фосфору/миш'яку другу маску 17 видаляють і здійснюють оксидування ще наявного і не покритого захисним шаром 11 полікремнію 10, внаслідок чого утворюється оксидний шар 22 При цьому покриті оксиднонітридно-оксидним шаром 11 з'єднувальні елементи 14, 18 не оксидуються Оксидування полікремнієвого шару 10 здійснюють, наприклад, у вологій атмосфері при температурі близько 950°С протягом 80 хв Цю підвищена температура одночасно використовують для вживляння легуючих матеріалів - бору і фосфору/миш'яку - у напівпровідникову підкладинку 1 для утворення розміщених у напівпровідниковій підкладинці електропровідних елементів 24 При цьому концентрацію легуючих матеріалів вибирають такою, щоб розміщені у напівпровідниковій підкладинці 1 з'єднувальні елементи 24 в зонах 23, 25 точок перетину 32, 34 мали достатню електропровідність Це запобігає утворенню транзисторів у точках перетину 32, 34 Утворена структура зображена на фіг 5 Згідно З ІНШОЮ формою виконання винайденого способу полікремнієвий шар 10 під час травлення видаляють не до попередньо заданої товщини, а повністю Завдяки цьому довготривала 57865 10 вання у зонах 23 і 25 одначе цю концентрацію операція оксидування для перетворення залишків легування можна визначити лише з дуже великими полікремнію більше не є необхідною В цьому разі витратами Тому здійснений після виготовлення здійснюють лише порівняно короткотривалу тепмікросхеми аналіз не допоможе коректно реконстлову обробку з метою вживления легуючих матеруювати и структуру Завдяки цьому маніпуляція з ріалів у напівпровідникову підкпадинку (950°С протакою інтегральною мікросхемою значно утруднетягом 20хв) на На фіг 6 показано вид зверху на структуру, зображену на фіг 5, яка в свою чергу є розгорнутим На фіг 7 також у виді зверху зображений приперерізом структури на фіг 6 по лінії АА' стрій згідно з винаходом, в якому дифузійні області 24 розміщені в одну ЛІНІЮ На противагу фіг 6 тут Видно, що доріжки 14 і 18 представляють розЛІНІЯ АА' випрямлена Зате доріжки затворів 14, 18 міщений на напівпровідниковій підкладинці 1 з'єдз'єднані між собою перпендикулярною до них пенувальний елемент, який, наприклад, з'єднує між ремичкою собою електроди затворів двох транзисторів (не показано) На противагу цьому дифузійні зони 24, І, нарешті, здійснюють осадження наступного контакт з якими буде утворений під час ПІЗНІШИХ ІЗОЛЯЦІЙНОГО шару, наприклад, BPSG, і наступного операцій крізь контактні отвори в зонах ЗО, пределектропровідного шару, наприклад, алюмінію, ставляють розміщені у напівпровідниковій підкладля утворення першого рівня металізації В залединці 1 з'єднувальні елементи жності від складності виготовлюваної схеми, можуть бути нанесені також ІНШІ ІЗОЛЯЦІЙНІ шари і Якщо хтось спробує аналізувати виготовлену ІНШІ електропровідні шари Для простих схем витаким способом інтегральну мікросхему, він побакористання одного рівня металізації є, як правило, чить зображену на фіг 6 структуру у вигляді двох достатнім, залишається лише нанести пасивуватранзисторів, виготовлених за КМ ОН-технологією льний шар Різниця проявляється лише у концентрації легуФІГ 2 Комп'ютерна верстка Е Ярославцева Підписано до друку 05 08 2003 Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ТОВ "Міжнародний науковий комітет", вул Артема, 77, м Київ, 04050, Україна

ДивитисяДодаткова інформація

Назва патенту англійськоюMethod for producing a semiconductor element with wiring extending partly in a substrate, and a semiconductor element produced by using the method

Назва патенту російськоюСпособ изготовления полупроводникового элемента с контактными дорожками, частично расположенными в подложке, и полупроводниковый элемент, изготовленный с помощью этого способа

МПК / Мітки

МПК: H01L 27/02

Мітки: спосіб, виготовлений, напівпровідниковий, способом, розміщеним, елементом, також, підкладці, цим, з`єднувальним, напівпровідникового, елемент, виготовлення, елемента, окремо

Код посилання

<a href="https://ua.patents.su/5-57865-sposib-vigotovlennya-napivprovidnikovogo-elementa-z-okremo-rozmishhenim-v-pidkladci-zehdnuvalnim-elementom-a-takozh-napivprovidnikovijj-element-vigotovlenijj-cim-sposobom.html" target="_blank" rel="follow" title="База патентів України">Спосіб виготовлення напівпровідникового елемента з окремо розміщеним в підкладці з’єднувальним елементом, а також напівпровідниковий елемент, виготовлений цим способом</a>

Попередній патент: Спосіб полімеризації олефінів з використанням місточкових металевих комплексів

Наступний патент: Спосіб одержання в’яжучого

Випадковий патент: Вапнокарбонізатор