Схема регулятора напруги для інтегральних мікросхем чіп-карток

Формула / Реферат

1. Схема регулятора напруги для інтегральних мікросхем чіп-карток, що містить виконану як послідовний регулятор (L) схему для формування внутрішньої напруги живлення (VDDint) із зовнішньої напруги живлення (VDDext), в якій послідовний регулятор (L) містить послідовний регулювальний транзистор (М1), виводи витоку і стоку якого під'єднані між виводами внутрішньої напруги живлення (VDDint) і зовнішньої напруги живлення (VDDext), а також регулювальний вивід (R), призначений для регулювання потенціалу, прикладеного до виводу затвора послідовного регулювального транзистора (М1), яка відрізняється тим, що між виводом внутрішньої напруги живлення (VDDint) і регулювальним виводом (R) послідовно під'єднані конденсатор (С1) і діючий як перехідний елемент (TG1) польовий транзистор, і вхід цього перехідного елемента (TG1) з'єднаний з виходом схеми формування змінного електричного потенціалу, який під час перехідного процесу в схемі відкриває перехідний елемент, внаслідок чого здійснюється заряд конденсатора (С), а після закінчення перехідного процесу закриває перехідний елемент.

2. Схема регулятора напруги за п. 1, яка відрізняється тим, що вивід перехідного елемента (TG1) з'єднаний з частиною схеми, яка формує сигнал, напруга якого послідовно в часі приймає два різні значення.

3. Схема регулятора напруги за п. 2, яка відрізняється тим, що двоступеневий сигнал є сигналом скидання при вмиканні напруги живлення (POR = Power-On Reset), що відповідає керувальному сигналу інтегральної мікросхеми для чіп-картки.

Текст

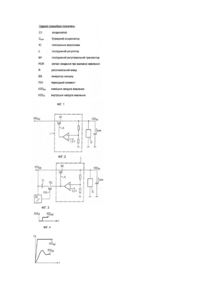

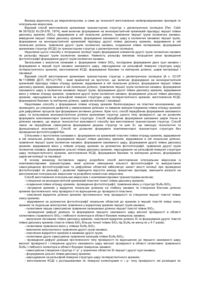

Винахід стосується схеми регулятора напруги для галузі проектування інтегральних мікросхем для чіп-карток. Інтегральні мікросхеми з різними доменами напруги (зовнішні і внутрішні напруги) містять зазвичай регулятори напруги, як написано, наприклад, на стор.10 публікації LP2954/LP2954A 5 V and Adjustable Micropower Low-Dropout Voltage Regulators фірми National Semiconductor Corporation за червень 1999 року. Робоча напруга інтегральної мікросхеми є різницею потенціалів між виводом маси (VSS) і потенціалом живлення. Ця напруга , яка в по даль шому назива ється вн утрі шньою напр угою жи влення VDDi nt форм ується із зовнішньої напр уги живлення VDD ext за допомогою складної схеми регулятора напруги, виконаного як послідовний регулятор. Для спрощення пояснення на Фіг.1 наведена відповідна рівню техніки схема послідовного регулятора напруги, яка і люстр ує пр инцип ро бо ти тако го ре гуля то ра шля хом ке р ування по слідо вним регулювальним транзистором. Зображена на Фіг.1 схема містить послідовний регулятор L, яка має послідовний регулювальний транзистор, і перетворює зовнішню напругу живлення VDDext у вн утрішню напругу живлення VDDint . До ви воду затвора послідовного регулювального транзистора М1 , що викон ує фун к ці ю ре гулюва льн о го ви во ду R по слі до вно го ре гуля тор а прикладається електричний потенціал, призначений для керування перетворенням напруги. Цей потенціал є внутрішнім аналоговим сигналом регулятора. Внутрішня напруга живлення VDDіnt призначена для живлення інтегральної мікросхеми чіп-картки. Буферний конденсатор для пояснення функціонування схеми позначений Сcore. Схема послідовного регулятора зазвичай значно складніша і відрізняється від зображеного простого прикладу при такому ж принципі роботи. Недоліком зображеної на Фіг.1 схеми регуля тора напруги є те, що при швидкому вмиканні зовнішньої напруги живлення VDDext виникають переколивання внутрішньої напр уги живлення VDDint , які від певного рі вня інтеграці ї біль ше не можуть бути припустимими, оскільки вони ведуть до пошкодження тонких оксидних шарів затворів транзисторів, з'єднаних з внутрішньою напругою живлення VDDint. На Фіг.4 зображені часові діаграми напруг VDDext і VDDint під час процесу вмикання. Крім того, для інтегральних мікросхем чіп-карток попередньо задана кількість приєдн увальни х кон тактни х пло ща док, які заз ви чай наз иваються сто впчико вими контактами (їх п'ять: VDDext , VSS, Clock - синхронізація, ІО введення/виведення, Reset - скидання), а також відпо відна станда ртам ISO/GSM послідо вність їх вмикання. Том у немає можливості досягнення бажаної перехідної характеристики шляхом введення додаткового стовпчикового контакту чи іншої послідовності вмикання. Задачею даного винаходу є розробка якомога простішої схеми регуля тора напруги для інтегральних мікросхем чіпкарток, в якому не виникає проблема переколивання при процесі вмикання. Ця задача вирішена у схемі регулятора напруги з ознаками п.1 формули винаходу. Вдосконалення винаходу відображені у додаткових пунктах формули винаходу. Відповідна винаходо ві схема регулятора напруги містить відомий сам по собі послідовний регулятор, призначений для одержання внутрішньої напруги живлення VDDint із зовнішньої напруги живлення VDD ext , причом у між виводом зовні шньої напруги живлення VDDext і регулювальним виводом послідовного регулятора послідовно під'єднані ко нденса тор і поль о вий тр анзи сто р у фун кці ї пере хі дно го е лемен та . Для цьо го перехідно го елемента сформований електричний потенціа л, змінюваний відповідно до керувального сигналу інтегральної мікросхеми чіп-картки. Послідовний регулятор містить послідо вний ре гулювальний транзистор, виво ди ви ток у і сток у яко го під'єднані між виводами внутрішньої напруги живлення VDDint і зовнішньої напруги живлення VDD ext, a ви від затвора є ре гулювальним ви водом послідо вно го р егуля тора або принаймні підведений до регулювального виводу. Потенціал, прикладений до затвора послідовного регулювального транзистора, є регульованим. На фігурах, призначених для пояснення винаходу, зображено: Фіг.1 - пояснена вище схема регулятора напруги із рівня техніки; Фіг.2 - переважна форма виконання відповідної винаходові схеми регулятора напруги; Фіг.3 - часова діаграма POR-сигналу; Фіг.4 - часові діаграми VDDint і VDDext для схеми згідно з Фіг.1; Фіг.5 - часові діаграми VDDіnt і VDDext для схеми згідно з Фіг.2. Н а Фі г.2 пре дста влени й прик ла д викона ння ві дпо ві дн о ї ви на ходо ві схеми регулятора напруги, в якому послідовний регулятор L для пояснення принципу дії схеми зображений таким же, як і на Фіг.1. Модифікації послідовного регулятора дають приклади виконання відповідної вина ходо ві схеми, які не потребують спеціального опису. Між витоком і затвором послідовного регулювального транзистора М1, канал витік-стік якого використовується для перетворення напруги, послідовно під'єднані конденсатор С1 і перехідний елемент TG1, утворений польовим транзистором. Інші схемні елементи відповідають звичайній схемі, наприклад, згідно з Фіг.1. Керування перехідним елементом здійснюють за допомогою сигналу, сформованого п р и з н а че н и м для ць о го си гн а ль н и м ге н е р а то р о м S G у ви г ля д і P OR -си гн а л у (POR = Power-On Resets скидання при вмиканні живлення), типова часова діаграма якого представлена на Фіг.3 . Цей PORсигнал є ци фро вим сигна лом і має два значення, а саме потенціал маси або VSS і зовнішня напруга живлення VDDext. Він формується в інтегральній мікросхемі чіп-картки незалежно від відповідної винаходові частини схеми і використовується під час процесу вмикання. В момент вмикання конденсатор С1 розряджений. При подачі зовнішньої напруги живлення VDDext внаслідок провідного стан у перехідного елемента послідовний регулювальний транзистор М1 відкри вається ві дпо відно до здійснювано го тепер заряджання конденсатора С1. Оскільки цей процес заряджання потребує певного часу, послідовний регулятор L відкривається досить повільно. Відповідні винаходові схемні елементи С1 і TG1 як суттєві для винаходу компоненти наявні у схемі незалежно від конкретної форми виконання п ослідо вно го ре гуля тора . Вони роз ра хо вуються на отримання сталої часу, більшої, ніж (внутрішня) стала часу регулятора напруги. Внаслідок цього (внутрішній) буферний конденсатор Ссоrе заряджається повільно, завдяки чому усувається переколивання внутрішньої напруги живлення VDDint. Цій схемі відповідають часові діаграми напруг, зображені на Фіг.5. П ісля зак ін че ння вн утр і шнь о го пе ре хі дно го про це су п ере хі дн ий елемен т закривається POR-сигналом. Оскільки додатковий конденсатор С1 під'єднаний лише до виводу зовнішньої напруги живлення VDD ext , а перехідний елемент під час роботи мікросхеми закритий, динамічні параметри інтегральної мікросхеми не погіршуються схемою регулятора напруги. Статичне і динамічне споживання струму під час експлуатації мікросхеми також не зазнають впливу. Перевагою зниження піків стр ум у є погіршення міграції електронів.

ДивитисяДодаткова інформація

Назва патенту англійськоюVoltage regulator for an integrated circuit of a smart card

Назва патенту російськоюСхема регулятора напряжения для интегральной схемы интеллектуальной карточки

МПК / Мітки

МПК: G05F 1/56, G06K 7/00, G05F 1/565, H02M 3/04, G06F 1/26, G06K 19/07

Мітки: мікросхем, регулятора, напруги, схема, чіп-карток, інтегральних

Код посилання

<a href="https://ua.patents.su/4-73218-skhema-regulyatora-naprugi-dlya-integralnikh-mikroskhem-chip-kartok.html" target="_blank" rel="follow" title="База патентів України">Схема регулятора напруги для інтегральних мікросхем чіп-карток</a>

Попередній патент: Нвч керуючий пристрій

Наступний патент: Електромеханічний реверсивний кроковий двигун

Випадковий патент: Спосіб одержання залізофулеренової сполуки с60fe3