Спосіб контролю інтегральних мікросхем пам’яті

Завантажити PDF файл.

Формула / Реферат

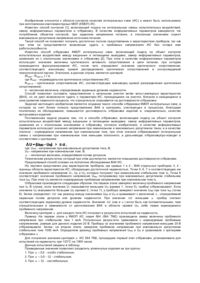

Способ контроля интегральных микросхем памяти, в соответствии с которым производят последовательную запись контрольного кода в объект контроля, выключают электропитание, а через время рассасывания избыточного заряда в дефектных ячейках памяти включают электропитание, считывают реакцию объекта контроля сравнивают импульсный код с эталонным значением, отличающийся тем, что перед началом контроля не менее двух раз включают электропитание, считывают информацию с каждой ячейки памяти, затем включают электропитание, время же выключенного состояния устанавливают больше, чем время рассасывания избыточного заряда для бездефектных ячеек памяти, параллельно запоминают адреса и информационные состояния только тех ячеек памяти, которые в процессе считывания повторяют свое информационное состояние, а на объект контроля подают контрольный код. противоположный написанному до начала контроля.

Текст

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля микросхем полупроводниковой памяти или других микросхем, содержащих триггерные ячейки. Известен способ контроля интегральных микросхем памяти [1], сущность которого состоит в следующем. При отключении питающего напряжения полупроводникового ЗУ происходит выключение генератора тока, задающего ток через ячейки памяти и начинается рассасывание избыточного заряда, накопленного во включенном элементе памяти (триггерная ячейка состоит из двух элементов - вентилей). Время отключения питания устанавливают равным времени рассасывания избыточного заряда для ячеек памяти, имеющих расчетный уровень параметров, обеспечивающих работоспособность ЗУ в диапазоне температур. В де фектных ячейках произойдет полное рассасывание избыточного заряда и, следовательно, при последующем считывании информация не будет соответствова ть ранее записанной. Недостатком способа является . низкая надежность выявления дефектных ячеек, потому что после включения питающего напряжения часть дефектных ячеек устанавливается в состояние, обусловленное существующей динамической асимметрией плеч триггера. Наиболее близким по технической сущности является способ контроля интегральных микросхем памяти [2], который включает выполняемые последовательно для каждой ячейки памяти операции записи контрольного кода в ячейку памяти, снижение напряжения питания до нуля. а затем через время, определяемое временем рассасывания избыточного заряда в дефектных плечах ячеек памяти, повышение напряжения питания до его номинального значения, считывание кода из ячейки памяти и сравнение полученного кода с эталонным. Недостатком известного способа является большое время контроля, обусловленное как большим значением времени рассасывания избыточного заряда даже в дефектных ячейках памяти, так и большим количеством ячеек памяти в запоминающих устройства х большой информационной емкости. Задачей изобретения является сокращение времени контроля интегральных микросхем памяти за счет предварительного выявления ячеек памяти, имеющих явно выраженную асимметрию плеч. Поставленная задача решается тем, что в способе контроля интегральных микросхем памяти, включающем последовательную запись контрольного кода в объект контроля, выключение электропитания, а затем через время рассасывания избыточного заряда в дефектных ячейках памяти включение электропитания, считывание кода и сравнение полученного кода с эталонным, согласно изобретению, перед началом контроля не менее двух раз включают электропитание, считывают информацию с каждой ячейки памяти и выключают электропитание, при этом время выключенного состояния устанавливают больше, чем время рассасывания избыточного заряда для бездефектных ячеек памяти, параллельно запоминают адреса и информационные состояния только тех ячеек памяти, которые в процессе считывания повторяют свое информационное состояние, а на объект контроля подают контрольный код, противоположный записанному до начала контроля. Заявляемый способ отличается от известного тем, что операции контроля выполняют лишь с потенциальнонеустойчивыми ячейками памяти и в одном из двух устойчивых состояний, для выявления которых и определения состояний, в которых необходимо проводить контроль, выполняют не менее, чем двукратное включение напряжения питания, считывание информации с каждой ячейки памяти без предварительной записи и выключение питания на время большее, чем время рассасывания избыточного заряда для бездефектных ячеек памяти, и параллельно за поминают адреса и информационные состояния только тех ячеек памяти, которые в процессе проведения считывания повторяют свое информационное состояние. Основной причиной отказа отдельных ячеек памяти является локальная дефектность одного из плеч ячейки, которая параметрически проявляется в снижении ниже расчетного значения коэффициентов передачи транзисторов, входящих в него, либо большой уровень токов утечки. Как правило, отказавшие в диапазоне температур элементы памяти имеют отклонение этих же параметров и при нормальной температуре, которое изза локального характера дефекта не может быть выявлено при технологическом контроле в процессе производства. Общим параметром, зависящим от величины коэффициента усиления и от уровня токов утечки, является время рассасывания избыточного заряда ранее открытого плеча элемента памяти. Определив время рассасывания избыточного заряда, можно различать дефектные элементы памяти по меньшей величине времени рассасывания. Однако, контроль каждой ячейки памяти по времени рассасывания в двух ее устойчивых состояниях, особенно для микросхем памяти большой информационной емкости, занимает значительное время и, поэтому, не пригоден для серийного производства. Так, для микросхемы памяти 185РУ5, информационной емкостью 1024 бита, со времени обрыва питания 0,5 сек время контроля одного кристалла составляет 1024 сек » 17 мин . Время контроля можно существенно сократить, если предварительно выявить ячейки памяти и их информационные состояния, которые имеют устойчивое предпочтительное состояние, а значит, устойчивую динамическую асимметрию плеч, одной из главных причин которой является локальная дефектность. Для выявления таких ячеек памяти в заявляемом способе используется следующий цикл операций: включение питания, считывание, запоминание адреса и состояния ячейки памяти, включение питания на время, заведомо большее времени рассасывания избыточного заряда с бездефектных ячеек. Такой цикл операций повторяется не менее двух раз. После этого выявляют адреса и информационные состояния тех ячеек памяти, у которых в каждом таком цикле информационное состояние остается неизменным, т.е. это их состояние является устойчиво предпочтительным. Выявленные таким способом ячейки памяти в состоянии, противоположном устойчивому, и подвергают в дальнейшем контролю по времени рассасывания по известному способу. Предложенный способ был осуществлен на микросхеме серии 185РУ5. Время проверки 3 экспериментальных партий пластин было сокращено в 37 раз и составило в среднем для одного кристалла 27 сек.

ДивитисяДодаткова інформація

Назва патенту англійськоюMethod for control of memory integral micro-circuits

Автори англійськоюBotvinik Mykhailo Ovsiiovych

Назва патенту російськоюСпособ контроля интегральных микросхем памяти

Автори російськоюБотвиник Михаил Евсеевич

МПК / Мітки

МПК: G01R 31/28

Мітки: контролю, мікросхем, інтегральних, пам'яті, спосіб

Код посилання

<a href="https://ua.patents.su/1-3749-sposib-kontrolyu-integralnikh-mikroskhem-pamyati.html" target="_blank" rel="follow" title="База патентів України">Спосіб контролю інтегральних мікросхем пам’яті</a>

Попередній патент: Пристрій для фотоекспонування екрану кольорової електронно-променевої трубки

Наступний патент: Бульдозер

Випадковий патент: Спосіб отримання органічного добрива методом ферментації із місцевої сировини