Спосіб електротермотренування інтегральних мікросхем

Номер патенту: 5309

Опубліковано: 28.12.1994

Автори: Молчанов Костянтин Вікторович, Ілюк Ігор Євгенович, Пенцак Іван Борисович, Остапчук Анатолій Іванович

Формула / Реферат

Способ электротермотренировки интегральных микросхем, в соответствии с которым подают тестовые воздействия и напряжение питания на клеммы для подключения объекта контроля, к выходу же объекта контроля подключают нагрузку, отличающийся тем, что электротермотренировку проводят при температуре окружающей среды в режиме, обеспечивающем пиковую мощность рассеивания объекта контроля, при этом кратковременно подают одновременно на входные и питающие выводы объекта контроля испытательное напряжение одинаковой величины, которая выше номинального значения, а величину нагрузки выбирают таким образом, чтобы обеспечить предельный выходной ток, входные же и питающие выводы объекта контроля соединяют таким образом, чтобы обеспечить при открытом выходе активное состояние интегральной микросхемы.

Текст

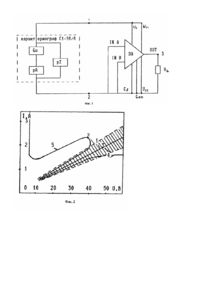

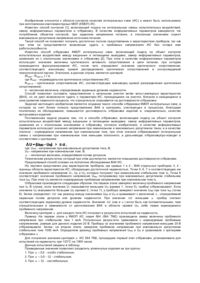

Изобретение относится к области измерительной техники и может быть использовано для контроля надежности интегральных схем (ИС). Известен способ электротермотренировки (ЭТТ) ИС. заключающийся в подаче тестовых воздействий на клеммы для подключения объекта контроля [I]. При этом тестовые воздействия, имитирующие режим работы ИС. подаются на входные и питающие выводы, а испытания, как правило, проводятся при температуре 125°С на протяжении нескольких суток. Длительная и трудоемкая операция проведения ЭТТ, даже в течение 240 часов, не позволяет с необходимой достоверностью выявить ИС склонные к отказам при нагрузках близких к экстремальным. ' Известен способ ЭТТ ИС, в соответствии с которым подают тестовые воздействия и напряжение питания на клеммы для подключения объекта контроля, к выходу же1 объекта контроля подключают нагрузку [2]. Способ предусматривает имитацию режима работы ИС подачей случайной последовательности импульсов. При этом на выводы питания подается номинальное напряжение, а на выходные выводы ИС через резисторы - напряжение, равное половине питающего. В связи с тем, что в реальных условиях эксплуатации ИС они подвергаются нагрузкам, превышающим режимы ЭТТ, а сам процесс электротермотренировки достаточно сложен и продолжителен во времени, затрудни ельно использовать данный способ при изготовлении ИС, особенно при значительных объемах производства. В основу изобретения поставлена задача усовершенствования способа электротермотренировки интегральных микросхем путем кратковременного.задания экстремальных режимов, что позволяет выявить дефектные ИС и, тем самым, повысить качество выпускаемых изделий при сокращении времени на проведение ЭТТ. Поставленная задача решается тем, что в способе электротермотренировки интегральных микросхем, по которому подают тестовые воздействия и напряжение питания на клеммы для подключения объекта контроля, к выходу же объекта кон і роля подключают нагрузку, согласно изобретению электротермотренировку проводят при температуре окружающей среды в режиме, обеспечивающем пиковую мощность рассеивания ИС, при этом кратковременно подают одновременно на входные и питающие выходы и пытательное натяжение одинаковой величины, которая выше номинального значения, а величину нагрузки выбирают таким образом, чтобы обеспечить предельный выходной ток, входные же и питающие выводы объекта контроля соединяют таким образом, чтобы обеспечить при открытом выходе активное ее состояние. Технический результат в предложенном методе достигается за счет того, что он проводится в режиме близком к предельному, обеспечивающему электротоковую тренировку практически всех р-n-переходов на предельных нагрузках, что позволяет выявить ИС с дефектами, вызванными флуктуациями технологических процессов и сократить продолжительность проведения ЭТТ. На фиг.1 приведена электрическая схема реализации предложенного способа ЭТТ ИС (на примере интегральной схемы КР1021ХА5), на фиг.2 - вольт-амперные характеристики (ВАХ) при нагрузке RL = 20 Ом (для КР1021ХА5), на фиг.3 блок-схема проведения ЭТТ. Изображенная на фиг.1 схема предназначена, при установлении требуемых норм и режимов, для реализации способа вручную и содержит; DA - испытуемых ИС с функциональ щ-ми выводами (Ucc, Uss, GND, Uc, InA, ІпГ); RL - сопротивление нагрузки ИС; Gu - источник постоянного напряжения; рА - измеритель тока; pZ - характериограф; Gu, pA, pZ- представляют собой прибор типа С1-96/6; 1, 2, 3 - узлы соединения выводов. На фиг,2 приведены ВАХ, снятые в соответствии со способом (пример для КР1021ХА5) характериографом (pZ) на узлах соединений 1 и 2 при нагрузке 20 Ом, где: - кривые 1, 2, 3 - типовые зависимости годных ИС, - кривые 4 и 5 - зависимости ИС, неустойчивых к предельным нагрузкам. На фиг.3 приведена блок-схема проведения ЭТТ в автоматическом режиме. В данном случае предполагается при контроле ИС по техническим условиям, который осуществляется на автоматизированных измерительных системах, одновременно проводить ЭТТ ИС, т.е. реализовать контроль по рассматриваемому способу. Схема содержит испытуемую ИС 1, контактное устройство 2, блок управления 3, блок коммутации 4, блок нагрузки 5, блок задания режимов 6, блок контроля 7, блок отображения информации 8. Пример: проводилась ЭТТ ИС КР1021ХА5. Выводы данной ИС, имеющие общепринятую н умерацию, разделялись на следующие гр уппы: первая - это выводы 6 и 9 (9-Ucc, 6-Uc), которые соединялись в узел 1 (см. фиг.1, на которой приведены эти узлы и гр уппы) и подключались к источнику напряжения Gu положительной полярности; вторая - это выводы 1, 2, 3, 4, 8 (1 - вход драйвера, 2 - общий, 3 - вход схемы переключения, 4 общий вывод выходного каскада, 8 - выход генератора обратного хода) которые соединяют в узел 2 и подключают к общему выводу источника напряжения Gu через измеритель рА, третья - это вывод 5 (выход усилителя), который подключается к сопротивлению RL нагрузки с одной стороны (узел 3), а другая сторона которого подключается к общему выводу в узел 2. После коммутации выводов в узлы 1 и 2, что обеспечивает при открытом выходе ИС (DA - на фиг.1) активное ее состояние, подавалось первое испытательное напряжение, равное номинальному напряжению питания и регистрировалось первое значение тока. Затем испытательное напряжение увеличивали до предельной величины и измеряли второе значение тока при сопротивлении нагрузки RL = 20 Ом. Продолжительность подачи испытательного режима определяется предельной пиковой мощностью рассеивания и составляет для КР1021ХА5 - 10 с. При этом происходит разогрев кристалла ИС до температуры 125-150°С. Микросхемы, ток которых не соответствовал типовым значениям, отбраковывались. Изделия, ток которых соответствует норме (имеют ВАХ, приведенные на фиг.2, зависимости 1,2.3), направляются далее по технологическому маршруту.

ДивитисяДодаткова інформація

Назва патенту англійськоюMethod for electric-thermal training of integrated circuits

Автори англійськоюIlliuk Ihor Yevhenovych, Molchanov Kostiantyn Viktorovych, Ostapchuk Anatolii Ivanovych, Pentsak Ivan Borysovych

Назва патенту російськоюСпособ электро-термо-тренировки интегральных микросхем

Автори російськоюІлюк Игорь Евгеньевич, Молчанов Константин Викторович, Остапчук Анатолий Иванович, Пенцак Иван Борисович

МПК / Мітки

МПК: G01R 31/28

Мітки: електротермотренування, мікросхем, інтегральних, спосіб

Код посилання

<a href="https://ua.patents.su/3-5309-sposib-elektrotermotrenuvannya-integralnikh-mikroskhem.html" target="_blank" rel="follow" title="База патентів України">Спосіб електротермотренування інтегральних мікросхем</a>

Попередній патент: Установка для розподілу і термічної обробки дисперсних матеріалів

Наступний патент: Штабелюючий пристрій

Випадковий патент: Спосіб амортизації стиків рейок та пристрій для його реалізації