Інтегральна схема на комплементарних моп-транзисторах

Номер патенту: 27693

Опубліковано: 16.10.2000

Автори: Ван ден Елсхоут Андреас Антоніус Йоханнес Марія, Харбертс Дірк Віллем, Вендрик Хендрікус Йозефіус Марія

Текст

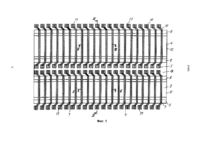

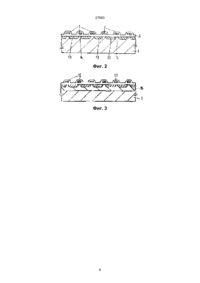

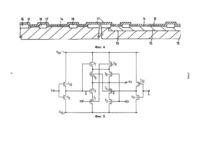

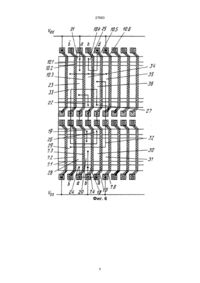

Изобретение относится к интегральной схеме на комплементарных МОП-транзисторах типа матрицы логических элементов, содержащей полупроводниковую подпложку, обеспечивающей на одной поверхности: первый ряд и соседний параллельный второй ряд МОП-транзисторов с каналом p-типа, имеющих общие электроды затвора в виде токопроводящих дорожек, размещенных перпендикулярно направлению обоих рядов; первый ряд и соседний параллельный ряд МОП-транзисторов с каналом р-типа, имеющих общие электроды затвора в виде токопроводящих дорожек, простирающихся перпендикулярно направлению обоих рядов. Такое устройство известно, например, из описания изобретения к патенту США № 4764798. Как известно, применение технологии матриц логических элементов позволяет значительно сократить сроки выпуска интегральных схем, начиная с момента проектирования до их из-готовления. При этом предусматривается изготовление и последующее хранение кремниевых пластин, включающих в себя истоковые и стоковые зоны, и поликристаллический кремний, обычно используемый для электродов затворов МОП-транзисторов с каналами n- и р-типов, образующих регулярную структуру. Если требуется осуществить ввод заданной функции по желанию заказчика, то эта Функция может быть полностью описана в рисунках расположения контактных окон и соединений разводки в одном или более слоях соединений. Для изготовителя это означаете, что он должен с почти уже готовой полупроводниковой пластиной выполнить только последние операции производственного процесса (т.е. технологические операции обеспечения контактных окон и слоев соединений плюс технологические операции травления). При установлении размера полевых транзисторов или более конкретно ширины необходимо принять во внимание ряд более или менее противоречивых требований, которые не всегда полностью обеспечиваются. Следует отметить, что под шириной понимается размер, обусловленный плоскостью параллельной плоскости поверхности, перпендикулярной направлению протекания тока истока и тока. При разработке постоянного запоминающего устройства существенную роль играют транзисторы с очень небольшими размерами, преимущество которых состоит в очень высокой плотности компановки. И наоборот, для выполнения заданных логических функций требуется обеспечить транзисторы со значительно большими размерами. Такие транзисторы могут быть обеспечены в виде транзисторов, размещенных последовательно в ряд и включенных параллельно. Однако было обнаружено, что на практике для реализации такого решения требуется обеспечить очень большое пространство, что, в свою очередь, часто приводит к резкому снижению гибкости при разработке схемы, исполняющей заданную функцию. В вышеупомянутом патенте США № 4764798 предлагается использование вместо одного ряда двух соседних рядов МОП-транзисторов с каналом n-типа, имеющих общие электроды затвора, и двух рядов полевых транзисторов с каналом р-типа, имеющих общие электроды затвора. Если по желанию соседние области n-канала и р-канала соединены соответственно друг с другом, то можно обеспечить транзисторы, характеризующиеся вдвое большей шириной. Благодаря такой конфигурации обеспечивается значительное увеличение гибкости. Имеется возможность, в частности, исполнить транзисторы с каналом р-типа, ширина канала которых в два раза больше ширины транзисторов с каналом n-типа, особенно в случае компенсирования примерно в два раза меньшей мобильности дырок по сравнению с электронами. Однако в случае, если потребуются транзисторы, значение соотношения для ширины канала которых составляет больше 2-х единиц, опять же необходимо при такой конфигурации обеспечивать параллельное включение в ряд транзисторов. Задачей изобретения является создание устройства типа матрицы логических элементов, характеризующегося конфигурацией, при которой достигается высокая плотность размещения и более высокая гибкость, особенно по отношению к ширине каналов транзисторов, без существенного увеличения площади. Изобретение основано на знании того факта, что данная задача может быть решена посредством использования рядов транзисторов, имеющих различную ширину каналов. Интегральная схема матрицы логических элементов, описание варианта которой дано в введении, в соответствии с изобретением характеризуется тем, что, кроме первого и второго рядов транзисторов с каналом n-типа и кроме первого и второго рядов транзисторов c каналом р-типа, соответственно в схеме предусмотрен (по крайней мере)один дополнительный ряд (спроектированный как третий ряд) транзисторов с каналом n-типа и транзисторов с каналом р-типа соответственно, который располагается параллельно первому и второму рядам. При этом электроды затворов транзисторов с каналом n-типа первого и второго рядов одновременно являются электродами затворов транзисторов и каналом n-типа третьего ряда, а электроды затворов транзисторов с каналом р-типа первого и второго рядов одновременно являются электродами затворов транзисторов с каналом р-типа третьего ряда, тог-да как транзисторы третьего ряда транзисторов с каналом n-типа и транзисторов с каналом р-типа соответственно характеризуется шириной, которая, по крайней мере, равна устроенной ширине транзисторов первого и второго рядов транзисторов с каналом n-типа и транзисторов с каналом р-типа соответственно. Например, в случае если ширина транзисторов равняется утроенной ширине транзисторов первого и второго рядов, то эффективное значение ширины канала транзистора может вменяться в 5 раз. Это можно проверить простым способом, посредством включения параллельно транзисторов, расположенных в трех рядах, без обязательного использования соседних транзисторов, размещенных в этом же ряду. Такое повышение гибкости может быть достигнута главным образом без увеличения рабочих площадей поверхности. При параллельном включении в первом и втором рядах транзисторов с узким каналом значение соотношения ширина каналов, равное 1:2, может быть получено по все той же методике, описанной в вышеупомянутом патенте США. Параллельный вариант реализации интегральной схемы в соответствии с изобретением характеризуется тем, что ширина полевых транзисторов третьего ряда транзисторов с каналом n-типа и третьего ряда транзисторов с каналом р-типа соответственно равняется четырехкратной ширине канала полевых транзисторов первого и второго рядов транзисторов с каналом n-типа и первого и второго рядов транзисторов с каналом р-типа соответственно. Более полное описание изобретения дано со ссылкой на несколько вариантов реализации и чертежи, на которых показано: фиг. 1 - вид сверху (горизонтальная проекция) матрицы логических элементов до осуществления разводки по обеспечению соответствующей функции; фиг. 2, 3 и 4 - поперечный разрез этой схемы, выполненный по линиям II-II, III-III и IV-IV соответственно, представленным на фиг. 5; фиг. 5 - принципиальная электрическая схема логического элемента “исключающее или-не”. фиг. 6 - схематичный вариант осуществления этого логического элемента, представленного в матрице логических элементов, показанной на фиг. 1. Следует отметить, что схемы, представленные на чертежах, являются принципиальными схемами и не масштабируются. На горизонтальной проекции схемы, представленной на фиг. 1, и на поперечных разрезах, отображенных на фиг. 2, 3 и 4, часть схемы матрицы логических элементов показана на стадии изготовления, когда транзисторы исполняются на полупроводниковой подложке и устройство готово к выполнению специфической функции, определяемой посредством дальнейшей разводки. Устройство содержит монокристаллическую полупроводниковую подложку I, которая может быть изготовлена из любого приемлемого полупроводникового материала, в данном случае из кремния, например, с удельной проводимостью р-типа. На поверхности 2 подложки I располагаются система 3 транзисторов с каналом n-типа и система 4 транзисторов с каналом р-типа. Система 3 включает в себя первый ряд 5 и параллельный ему второй ряд 6 полевых транзисторов с каналом n-типа, имеющих общие электроды затвора 7, которые располагаются под прямыми углами к направлению обоих рядов 5 и 6. Аналогично система 4 содержит первый ряд 8 и второй ряд 9 полевых трназисторов с каналом p-типа, имеющих общие электроды затвора 10. Транзисторы с каналом n-типа рядов 5 и 6 характеризуются одинаковой или, по крайней мере, почти одинаковой шириной канала Wn. Транзисторы с каналом р-типа рядов 8 и 9 также имеют одинаковую или, по крайней мере, почти одинаковую ширину канала Wp. В соответствии с изобретением каждая из систем 3 и 4 содержит, кроме упомянутых рядов, дополнительный третий ряд II и I2 транзисторов с каналом n-типа и транзисторов с каналом р-типа соответственно, ширина которых, по крайней мере, равна трехкратной ширине Wn и Wр соответственно. Электроды затворов 7 и 10 одновременно являются электродами затворов транзисторов с каналом n-типа II и транзисторов с каналом р-типа 12 соответственно. Как видно из поперечного разреза, представленного на фиг. 2, n-канальные транзисторы ряда содержат последовательность соседних зон удельной проводимости n-типа 13. Части подложки удельной проводимости р-типа между зонами 13 образуют канальные области, которые отделены с помощью тонкого слоя оксида 14, являющегося изолирующим слоем затвора, от электродов затвора 7. При данной конфигурации транзистор может быть образован таким образом, что электрод затвора 7 и зоны с удельной проводимостью n-типа 13 c левой и правой стороны этих электродов соответствующим образом подсоединяются друг к другу. Этот транзистор может быть изолирован как в случае необходимости, так и по желанию, причем таким образом, что на соседние электроды затворов подается очень низкий потенциал (изоляция затвора). Ряды транзисторов с каналом р-типа содержат зону с удельной проводимостью n-типа 15, которая образуется в подложке с удельной проводимостью р-типа 1 и обычно проектируется в виде “кармана” или ”потенциальной ямы” (фиг. З). В зоне 15 обеспечивается последовательность поверхностных зон с удельной проводимостью р-типа, с помощью которых можно образовать транзисторы по той же технологии, что и в случае зон 13, вместе с промежуточными частями зон с удельной проводимостью nтипа 15, образующей каналы с затворами 10. Изоляция между каналами транзисторов может быть обеспечена таким образом, что на соседние электроды 10 подается высокое положительное напряжение. На фиг. 4 схематично отображена ширина каналов для транзисторов с каналом n-типа и транзисторов с каналом р-типа, где показанный поперечный, разрез схемы произведен по линии вдоль электрода затвора 7 и электрода затвора 10. В левой части фиг. 4 показан поперечный разрез системы транзисторов с каналом n-типа. В центре чертежа размещен ряд II, содержащий полевые транзисторы, имеющие сравнительно большую ширину канала. С каждой стороны ряда II расположены ряды 5 и 6, содержащие транзисторы, имеющие сравнительно небольшую ширину канала. Таким же образов в правой части фиг. 4 показана ширина транзисторов с каналом р-типа ряда 12, размещенного в центре, и всех транзисторов с каналом р-тип рядов 8 и 9. Как следует из фиг. 4, области, в которых расположены ряды 5,6,8,9, II и I2 по окончании технологического процесса ограничиваются сравнительно толстым защитным слоем оксида 16, который частично погружается в подложку 1 и имеет значительно большую толщину, чем изолирующий слой затвора 14. На защитном слое оксида 16 (фиг. 1) размещаются контактные поверхности 17 электродов затвора 7 и 10, от которых идут соединения к другим токопроводящим дорожкам, возможно обеспечиваемым на последующих стадиях технологического процесса. Следует отметить, что для рядов транзисторов системы 4 транзисторов с каналами р-типа обеспечивается общий пакет с удельной электрической проводимостью n-типа. В случае необходимости также могут быть обеспечены три ряда 8, 9 и 12, каждый предусмотренный в отдельном пакете. Ширина рядов II и I2, по меньшей мере, в три раза превышает ширину рядов 5, 6 и 8, 9 соответственно. В результате этого, как уже отмечалось выше, имеется возможность широкого выбора эффективных значений ширины, В конкретном варианте реализации изобретения ширина рядов 5, 6, 8 и 9 составляла 2 мкм, тогда как ширина ряда II была равной 9 мкм, а ширина ряда 12 равнялась 12 мкм. При этом имеется возможность получить даже большее значение соотношения ширины каналов. На фиг. 5 и 6 дан пример изготовления так называемой схемы логической операции "исключающее или-не". На фиг. 5 показана электрическая принципиальная схема, которая в данном примере имеет два входа. Входные сигналы обозначены как сигналы a и b , тогда как инверсные сигналы обозначены через и соответственно. Схема содержит четыре транзистора с каналом n-типа Т1, Т2, ТЗ и Т4 и четыре транзистора с каналом р-типа Т5, Т6, Т7 и Т8. Линия питания (например, напряжения величиной 5В) обозначена как Vdd, тогда как линия заземления обозначена через Vss. Транзисторы T1, T3, Т5 и Т7 образуют первое последовательное плечо, расположенное между линиями питания Vdd и заземления Vss, а транзисторы Т2, Т4, Т6 и Т8 образуют второе последовательное плечо. Стоковые области полевых транзисторов Т5 и Т6 подключены друг к другу, а также к выводу выходной клеммы Vo. Стоковые области полевых транзисторов T3 и Т4 также подсоединены к выводу Vo. Входной сигнал a подается к затворам полевых транзисторов Т1 и Т8, тогда как входной сигнал b подается к затворам полевых транзисторов Т2 и Т6. Инверсные сигналы ā и b подаются к затворам полевых транзисторов Т4 и Т5 и к затворам полевых транзисторов T3 и Т7 соответственно. Легко показать, что если входные сигналы a и b равны, т.е. когда они оба одновременно являются сигналами логической "I" или "O", то выходной сигнал Vo является сигналом высокого логического уровня (58). В других случаях выходной сигнал имеет низкий логический уровень ("исключающее или-не"). Для формирования различных сигналов a и b требуется предусмотреть две инвертирующие схемы. Инвертирующая схема, предназначенная для формирования сигнала b содержит транзистор c каналом nтипа Т9 и транзистор c каналом р-типа Т10. Истоковые зоны полевых транзисторов Т9 и Т10 подсоединены к выводу линии заземления Vss и выводу питания Vdd соответственно. Стоковые зоны транзисторов Т9 и Т10 подсоединены к электродам затворов полевых транзисторов T3 и Т7. Входной сигнал подается к электродам затворов полевых транзисторов Т9 и Т10. Выходной сигнал формируется в стоковых областях полевых транзисторов Т9 и Т10 и подается к электродам затворов полевых транзисторов ТЗ и Т7. Аналогично производится инвертирование входного сигнала с помощью инвертирующей схемы, выполненной на транзисторах ТII и ТI2, где транзистор ТII является полевым транзистором с каналом nтипа, а транзистор ТI2 является полевым транзистором с каналом р-типа. Размеры транзисторов Т9 и ТI9 могут быть очень небольшими, поскольку инвертирующие схемы практически не нагружаются. Транзисторы Т1÷Т8 наоборот выбираются гораздо больших размеров. На фиг. 6 показан возможный вариант осуществления схемы, представленной на фиг. 5. Этот вариант схемы является очень компактным благодаря организации системы из одного ряда широких (больших размеров) транзисторов и двух рядов узких (малых размеров) транзисторов. На фиг. 6 разводка отображена просто, обозначена пунктирной линией. Там, где соединения пересекаются друг с другом, они могут образовывать два различных слоя соединений разводки, электрически изолированные друг от друга. В варианте осуществления изобретения, рассматриваемом здесь, достаточно иметь два слоя соединений разводки помимо вышеупомянутого поликристаллического кремниевого слоя, в котором образовываются электроды затворов. Контакты, расположенные между слоями соединений разводки, и зоны или электроды затворов обозначены точкой. В нижней части и в верхней части чертежа показаны две линии, которые используются в качестве линии заземления Vss, и линии питания Vdd соответственно. Линия заземления Vss подсоединена к затворам 7,1 и 7,6 системы транзисторов с каналом n-типа. Под этими логическими элементами не могут быть образованы проводящие каналы, в результате чего между схемой и соседними схемами обеспечивается эффективная электрическая изоляция. Также для того, чтобы изолировать схему системы транзисторов с каналом р-типа линия питания Vdd подсоединяется к затворам 10,1 и 10,6. Кроме того, затвор 7,2 подсоединяется к затвору 10,2, тогда как затвор 7, 3 подсоединяется к затвору 10,3, а затворы 7,4 и 7,5 подсоединяются к затворам 10,4 и 10,5 соответственно. Входные сигналы a и b подаются, например, по сигнальным линиям (не показанным на рисунке) к затворам 7,3/10,3 и 7,4/10,4 соответственно. Потенциал напряжения Vss подается к зонам удельной электрической проводимости n-типа 20 и 21 узкого ряда транзисторов с каналом n-типа и к зоне удельной проводимости n-типа 22 широкого ряда транзисторов c каналом n-типа. Потенциал напряжения Vdd подается к зонам удельной электрической проводимости р-типа 23, 24 узких рядов транзисторов с каналом р-типа и к зоне удельной проводимости р-тип 25 широкого центрального ряда. Транзистор с каналом n-типа ТII образуется затвором 7,3 узкой зоной удельной проводимости n-типа 20, образующей истоковую зону полевого транзистора, и узкой зоной удельной проводимости n-типа 26, образующей стоковую область. Зона 26 подсоединена через затворы 7,5 и 10,5 к зоне удельной проводимости р-типа 27 ряда 9. Эта зона образует стоковую область полевого транзистора с каналом р-типа 12, затвор которого образуется электродом 10,3 и истоковая область которого образуется зоной удельной проводимости р-типа 23. Транзистор с каналом n-типа Т9 располагается в узком ряду 6 и содержит затвор 7,4 и зоны удельной проводимости n-типа 21 и 28, образующие стоковую и истоковую области соответственно. Зона 28, с которой подается инвертирующий сигнал , подсоединена к электродам затворов 7,2 и 10,2 и к зоне удельной проводимости р-типа 29, расположенной в узком ряду 8. Зона 29 является cтоковой областью транзистора с каналом ртипа Т10, затвор которого является затвором 10,4 и исток которого образован зоной удельной проводимости р-типа 24. Для транзисторов с каналом n-типа Т1÷Т4 используются зоны удельной электрической проводимости n-типа широкого ряда II, тогда как для транзисторов с каналом р-типа Т5÷Т8 используются зоны удельной проводимости р-типа широкого ряда 12. Таким образом, транзистор с каналом n-типа Т1 содержит зону удельной проводимости n-типа 22 в качестве истока, зону удельной проводимости n-типа 30 как стоковую область и электрод затвора 7,3, к которому подается сигнал a. В то же время зона 30 является истоком транзистора с каналом n-типа ТЗ, имеющего затвор 7,2, предназначенный для сигнала b и зону удельной проводимости n-типа 31, используемой в качестве истока. Транзистор с каналом n-типа Т2 содержит истоковую область 22, затвор 7,4 и стоковую область 32. Последняя область является одновременно истоком транзистора с каналом n-типа Т4 электрод затвора которого содержит затвор 7,5 и исток которого образуется зоной удельной проводимости n-типа 33. Истоковые области 31 и 33 соединены между собой с помощью соединения 34, которое может подводиться к выгодной клемме Vo для формирования и подачи выходного сигнала. Транзистор с каналом р-типа Т7 образуется как исток (широкой) зоны удельной проводимости р-типа 25, электрод затвора 10,2 и как стоковая область зоны удельной проводимости р-типа 35. Транзистор с каналом р-типа Т8 также содержит как исток зоны 25, электрод затвора 10,3, так и сток зону удельной проводимости р-типа 36. Стоковые области 35 и 36 параллельно включенных транзисторов Т7 и Т8 подсоединены друг к другу и к зоне удельной проводимости р-типа 37, которая образует истоковую область транзистора с каналом р-типа Т5. Электрод затвора полевого транзистора Т5 образуется затвором 10,5 (сигнал), а стоковая область образуется зоной удельной проводимости р-типа 38. Эта зона одновременно образует стоковую область транзистора с каналом р-типа Т6, который имеет электрод затвора 10,4 и истоковая область которого образуется зоной удельной проводимости р-типа 36. Зона 38 подсоединена к выводу 34, с которого может сниматься напряжение сигнала Vo. Благодаря системе как области дырочной электропроводности, так и области электронной электропроводности двух очень узких рядов транзисторов и одного очень широкого ряда может быть получена очень компактная структура, при реализации которой требуемое количество пространства главным образом определяется шириной транзисторов Т1÷Т8. Четыре транзистора Т9÷ТI2, предназначенные для инвертирования входных сигналов a и b в основном не требуют обеспечения дополнительного пространства. Хотя имеется возможность расположить узкие ряды 5/6 и/или 8/9 рядом друг за другом, рассмотренная здесь конфигурация, при которой узкие ряды располагаются с каждой стороны широких рядов, имеет дополнительные преимущества благодаря высокой гибкости при разработке схемы. Ценность изобретения состоит в том, что оно не ограничивается рассмотренным здесь вариантом, но в рамках объема изобретения специалисты в данной области технически могут внести многочисленные дополнительные изменения. Например, как в области электронной электропроводности, так и в области дырочной электропроводности можно расположить больше трех упомянутых рядов, если корпус позволяет предусмотреть ширину узких рядов. Вместо схемы логической операции “исключающие или-не” также могут быть упомянуты другие логические элементы и/или схемы запоминающих устройств описанной здесь матрицы логических элементов. 27693 6 Фиг. 1 27693 Фиг. 2 Фиг. 3 6 Фиг. 4 8 27693 Фиг. 5 27693 Фиг. 6 9 27693 9

ДивитисяДодаткова інформація

Назва патенту англійськоюIntegral circuit based on complemantary mos transistors

Автори англійськоюVendrik Hendrikus Josephius Maria, Van den Elshout Andreas Antonius, Harberts Dirk Willem

Назва патенту російськоюИнтегральная схема на комплементарных моп-транзисторах

Автори російськоюВендрик Хендрикус Йозефиус Мария, Ван ден Элсхоут Андреас Антониус, Харбертс Дирк Виллем

МПК / Мітки

МПК: H01L 27/118

Мітки: схема, інтегральна, моп-транзисторах, комплементарних

Код посилання

<a href="https://ua.patents.su/9-27693-integralna-skhema-na-komplementarnikh-mop-tranzistorakh.html" target="_blank" rel="follow" title="База патентів України">Інтегральна схема на комплементарних моп-транзисторах</a>

Попередній патент: Спосіб визначення крайового кута змочування пористих тіл

Наступний патент: Роторний вітродвигун

Випадковий патент: Спосіб визначення індексу стабільності оборотної води систем технічного водопостачання щодо виділення твердого сасо3